SoC(System on Chip)可以譯為"系統集成芯片",意指它是一個產品,是一個有專用目標的集成電路,其中包含完整系統并有嵌入軟件的全部內容;SoC也可以譯為"系統芯片集成",意指它是一種技術,用以實現從確定系統功能開始,到軟/硬件劃分,并完成設計的整個過程。

作為ASIC(Application Specific IC)設計方法學中的新技術,SoC始于20世紀90年代中期。1994年MOTORLA發布的Flex CoreTM系統(用來制作基于68000TM和Power PCTM的定制微處理器)和1995年LSI Logic公司為SONY公司設計的SoC,可能是基于IP(Intellectual Property)核完成SoC設計的最早報導。由于SoC可以充分利用已有的設計積累,顯著地提高ASIC的設計能力,因此發展非常迅速。在2000年的CICC(Custom IC Conference)會議上,MOTORLA SoC 設計技術研究部主任 Joe Pumo作了主題報告(key note),題目是"SoC:The Convergence Point for Solution of the 21st century[1]。CICC是ASIC設計領域最高層次的國際學術會議。它的主題報告一般代表著ASIC設計領域的技術發展趨勢,也說明SoC在ASIC學術界和工業界受到重視的程度。本文擬對嵌入式SoCIC的設計方法和流程作些討論。

一、系統集成芯片(SoC)是IC設計的發展趨勢

(1)隨著微電子技術和半導體工業的不斷創新和發展,超大規模集成電路和集成度和工藝水平不斷提高,深亞微米(deep-submicron)工藝,如0.18μm、0.13μm已經走向成熟,使得在一個芯片上完成系統級的集成已成為可能。

(2)各種電子系統出于降低成本、減少體積的要求,對系統集成提出了更高的要求。

(3)高性能的EDA工具得到長足發展,其自動化和智能化程度不斷提高,為嵌入式系統設計提供了功能強大的開發集成環境。

(4)計算機硬件平臺性能大幅度提高,使得很復雜的算法和方便的圖形界面得以實現,為復雜的SoC設計提供了物理基礎。

IC技術的迅速發展得益于IC產業內部的細致分工,SoC技術正是IC產業分工的體現。確切地說,60年代的IC產業應該是半導體產業,當時的廠家沒有分工,所掌握的技術十分全面,最典型的代表就是Fairchild公司,不但生產晶體管、集成電路,就連擴散爐都自己制作,如圖2中的第一行所示。到了70年代開始分工,半導體工藝設備和ICCAD設備成為獨立產業,以其精湛的專業技術為IC廠家提供高質量的設備。此時IC廠家可以有更多的精力用于產品的設計與工藝的研究。到了80年代,工藝設備生產能力已經相當強大,而且費用也十分昂貴,IC廠家自己的設計已不足以供其飽和運行。因此開始承接對外加工,繼而由部分到全部對外加工,形成了Foundry加工和Fabless設計的分工。IC產業的這一次分工,再加上ICCAD工具發展為EDA系統和大批沒有半導體背景的系統設計師提供了直接介入IC設計的條件。由于系統設計師來自國民經濟的各行各業,因此使得IC的作用也滲透到各行各業,開拓了IC的應用領域,擴大了對IC的需求。80年代的這次分工是IC發展過程中的一次重要分工,極大地推動了IC產業的發展。

二、何為嵌入式SoC IC

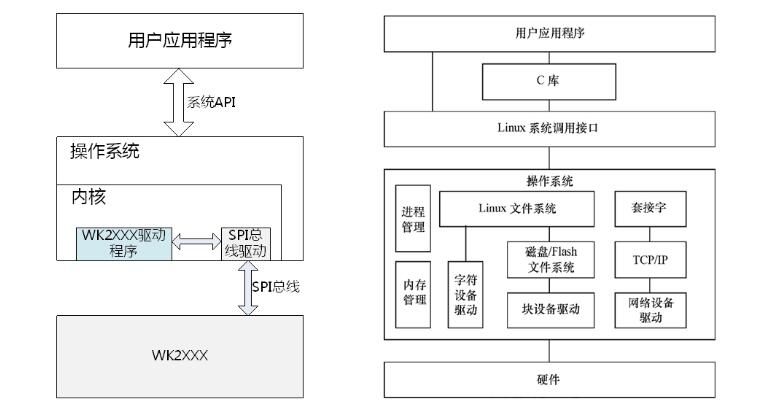

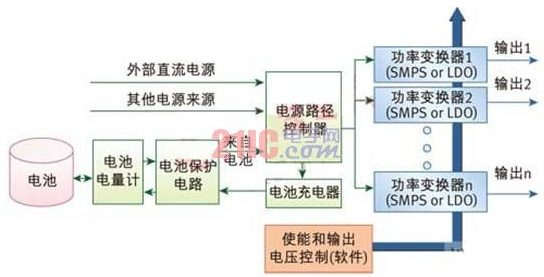

SoC(System on Chip)是指集系統性能于一塊芯片上的系統級芯片。它通常含有一個微處理器核(CPU),有時再增加一個或多個DSP核,以及多個或幾十個的外圍特殊功能模塊和一定規模的存儲器(RAM、ROM)等。嵌入式SoC更是針對應用所需的性能,將其設計在芯片上而成為系統操作芯片。芯片的規模常常可以達到數百萬門甚至上千萬門以上,所以嵌入式SoC是滿足應用的系統級的集成電路產生,一方面要滿足復雜的系統性能的需要,另一方面也要滿足市場上日新月異的對新產品的需求,因此嵌入式SoC的設計也代替了高科技的設計方法和程序。只有在不斷地發展優化下,嵌入式SoC才能提供設計周期短而性能優異的產品。因此,要掌握嵌入式系統芯片的設計,就要了解其設計方法和流程。

三、嵌入式SoC IC的設計方法和流程

SoC IC的設計原則,就是盡可能重用各種功能模塊并集成為所需的系統級芯片。讀到設計重用,必須對重用時需要考慮的因素作一些說明。首先,重用的功能模塊要有詳盡的說明書,對模塊的功能和適用范圍以及芯片集成時的總線接口進行說明。其次,要提供該模塊過去已實現的生產工藝。第三,要提供用于測試該模塊的測試程序及測試平臺。最后,也是最重要的,就是模塊的設計內核。通常提供的設計分為“軟模塊”和“硬模塊”兩種。“軟模塊”只提供RTL語言描述,可以用EDA綜合工具產生電路。它的優點是比較靈活,可以根據不同的生產工藝產生對應的電路。“硬模塊”提供的是已經完成的電路物理設計(physical design),也就是版圖的設計(layout)。它的缺點是一旦生產工藝改變就不能夠再使用了,即使是在采用同樣生產工藝的情況下,由于模塊的物理尺寸已經確定因而也影響了布局(floor-plan)的靈活性;它的優點是在設計采用同樣生產工藝的產品并且其物理尺寸不影響芯片布局的情況下,能夠直接采用,不用重新設計。由于半導體工藝發展極快,通常重用“軟模塊”比較多。

目前,在歐洲和北美已經在產業界形成了基于IP(Interllectual Property)總線模塊的重用標準,對于重用的各個因素都有明確的規定。我國的IC設計產業正在迅速發展,應該盡快建立自己的重用標準,與國際接軌。

通常SoC IC的設計方法有兩種:一種是基于模塊(module-based)的設計方法,另一種是“門海”(sea-of-cell)的設計方法。

Module-based的設計方法是指各個單元模塊完成各自的RTL和電路綜合以及版圖設計,然后,在頂層完成整個芯片的版圖設計。這種方法的優點是當個別模塊進行修改進,不會對整個芯片的設計產生較大的影響。它的設計流程如圖1所示。

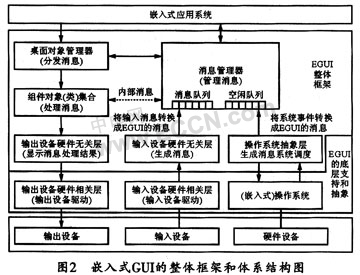

Sea-of-cell的設計方法指的是在各個單元模塊完成RTL后,直接對整個芯片進行綜合,產生整個芯片的網表,然后,完成整個芯片的版圖設計。它的優點是能夠節省芯片面積,缺點是一旦某個模塊修改了,整個芯片要重新做綜合和版圖設計。它的設計流程如圖2所示。

四、SoC IC滿足的時序要求

由于SoC IC的規模一般都非常大,因此各個模塊用于綜合(synthesis)的約束條件必須基于整個芯片的時序要求來產生,才不至于對整個芯片的Timing產生影響。Synopsys公司的Design Budgeting工具能夠根據芯片頂層的約束條件對整個芯片以及子模塊的約束和時序進行分配和控制,并且產生以此為基礎的各個子模塊的約束條件用于電路綜合,由于芯片頂層以及模塊之間的時序已經得到平衡考慮,許多時序問題(timing violations)已經預先得到控制,能夠減少后期對設計進行反復修改的次數。

在對電路進行驗證(verify)的時候,除了驗證功能正確外,還要驗證工作時序的正確性。通常的方法是編寫專門的測試程序,運行EDA仿真工具來完成,這通常稱為動態仿真(dynamic simulation)。由于SoC IC的規模比較大,仿真(simulation)運行的時間比較長,尤其是在完成版圖設計后做后仿真(postlayout simulation)的時候,因此,我們要引入靜態時序分析的方法(static timing analysis)。它是從電路的連接和布線上來推測貪污傳輸的時序,因此當電路的工作時鐘和約束條件確定后,電路中信號傳輸時的設定時間(setup time)和保持時間(hold time)也已經確定,通過靜態時序分析就可以把那些不滿足要求的路徑或電路單元找出來,提供修改設計的依據。它的特點是運行時間遠遠少于動態仿真。許多電路的時序問題可以預先發現而不用等到動態仿真完成,因而可以幫助我們縮短設計周期。常用的設計工具有Synopsys公司的Primetime和Cadence公司的Pearl。

IC工藝的發展也給人們帶來一些憂慮,這就是所謂的"極限"問題。擔心Moore定律是否有效,現行的硅基工藝還能持續多久?這個問題已經討論了10年。在這10年的IC發展中可以得出這樣的結論:21世紀,起碼是21世紀前半,系統集成仍然是以硅基工藝實現。盡管微電子學在化合物和其他新材料方面的研究取得了很大進展,但全世界數以萬億計的設備和技術投入,已經使硅基工藝形成非常強大的產業能力。同時,長期的科研投入已使得人們對硅及其衍生物各種屬性的了解達到十分深刻、十分透徹的地步,成為自然界100多種元素之最,這是非常寶貴的知識積累。產業的能力和知識的積累決定著硅基工藝起碼將在30~50年內起骨干作用,還將繼續發展。即使是Moore定律不再有效,硅工藝為IC設計提供的加工能力也足夠使用幾十年。

五、版圖設計

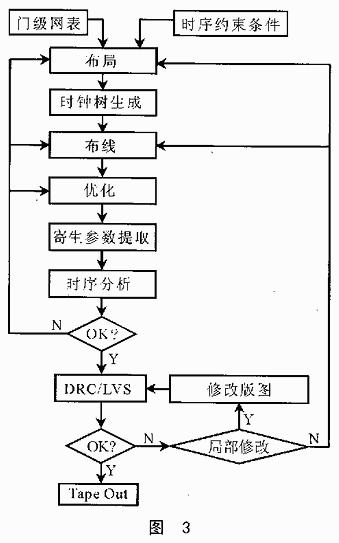

對于復雜的SoC IC,其版圖設計(layout)也是非常復雜的。隨著半導體工藝的越來越精密,芯片的規模越來越大,版圖布線的負荷已成為主要的時序影響因素,所以自動布局布線的時序分析成為設計的重點。無論采用module-based的設計方法還是sea-of-cell的方法,最好要采用時序驅動(timing driven)的版圖設計方式,這樣,可以確保前端各個層次的設計約束條件延伸到物理設計(physical design)中去。具體做法是將綜合電路的約束條件轉化為Layout工具可以識別的格式,用來驅動Layout工具完成設計。此外,為了保證電路的時鐘到達各時序單元的時間的一致性,需要在各時鐘路徑上插入時鐘樹(clocktree),通過一定的約束條件,Layout工具可以通過平衡時鐘路徑之間的差異(skew),自動完成時鐘樹的生成。通常的版圖設計流程如圖3所示。

最后,當布局布線完成之后,還要做DRC和LVS的檢查。DRC(Design Rule Check)是檢查版圖設計定否符號生產工藝的物理規則要求;LVS(Layout Versus Schematic)是檢查版圖設計是否與電路設計一致。只有當這兩項檢查都通過后,版圖設計的工作才算完成。我們通常采用Cadence或Avanti公司的Layout檢查工具。

再要一提的是,當生產工藝小于0.35μm以下時,尤其在采用同步電路設計方法時,因為布線而造成的時序差異和延遲常常超過模塊中電路設計的差異和延遲。因此,在Layout時對布局設計和時鐘樹生成需要仔細考慮。Layout完成后的時序分板是做好設計的關鍵。這也是選擇基于模塊設計方法或是“門海”設計方法時要考慮的因素之一。

對于深亞微米的版圖設計,還有兩個因素要考慮。一個是當走線過長時產生的天線效應(antennaeffect)會對電路的時序產生影響。解決的辦法是在長走線中插入天線二極管(antenna diode),用于抵消天線效應。另一個情況是當兩條平行的走線非常靠近的時候,它們之間的偶合效應會產生交叉干擾(cross-talk),也會對電路的時序造成不利影響。解決的辦法是在線路中加入buffer來克服,采用Cadence公司的Signal Integrity工具可以分析出交叉干擾出現的電路部分并結合Layout工具自動完成buffer的插入。

芯片端口(I/O PAD)的設計也是SoC IC設計的重點,除了要考慮靜電保證ESD、驅動能力等因素外,還要考慮到當兩個PAD靠得很近的時候,它們之間的耦合效應會形成寄生三極管(parasitic transistor)效應,影響I/O PAD的正常功能。

SoC IC通常都是數模混合電路,版圖設計的核心是防止噪聲干擾。通常要從兩個方面來考慮:一是在布局時盡量使相互容易受干擾的模塊分開得遠一些;二是數字電路和模擬電路要采用不同的電源和布線。

六、SoC IC的測試設計DFT(Design For Test)

芯片的測試,一方面是為了保證芯片的質量和可靠性,另一方面也要滿足低成本的生產目的。過去,傳統的測試方法是把我們用于功能仿真的測試程序轉化為生產測試程序輸入測試儀器。它的缺點是測試時間長,尤其是高覆蓋率(test coverage)的要求下,對于大規模的SoC IC,其成本將非常高。現在,通常采用插入測鏈(scan chain)的方法,使得芯片中的時序單元在測試模式下連接成移位寄存器(shift register),然后,采用ATPG(Automatic Test Pattern Generator)工具產生的測試向量,能夠有效地對芯片完成測試。測試時間大大縮短,也能達到高于90%的覆蓋率,保證產品的品質和可靠性。許多EDA工具如Synopsys公司的Design Compiler和Mentor公司的DFT Aduvisor/Fastscan都可以幫助完成這一工作,自動化程序相當高。當然,這一方法的代價是會增加芯片的面積。需要指出的是,采用插入測試鏈的方法只適用于同步電路設計,而且在電路的RTL設計階段就要把這一因素考慮進去。對于異步電路的測試主要還是通過功能測試完成。

由于SoC IC比較復雜,芯處中需要設有專門的測試控制模塊(test control module),將整個芯片分為若干個測試組,每個部分都有獨立的測試鏈完成測試。結合若干個芯片端口完成整個芯片的測試控制。

結束語

設計計劃考慮項目:

Product Design specification(產品設計規格書)

Design methodology and EDA tools selection(設計方法和設計工具的選擇)

Database structure(and choose a Database Manager)(設計數據的存儲結構)

Naming convertion(命名規范)

IP Module re-use consideration (IP模塊重用的考慮)

Test plan(測試計劃)

Chip Integration plan(整個芯片的集成計劃)

Design schedule(設計時間表)

Design Resources requirement plan(設計的人力和軟硬件需求計劃)

Detail design task check off list。(詳盡的設計任務完成情況檢查表)

SoC IC成為現代電子系統的核心已是不爭的事實,一個人或幾個人包打天下的可能性已經很小。有效利用“重用”功能模塊和強大EDA工個的支持是SoC IC設計的基礎,而采用好的設計方法和流程、解決好Timing Closure和Testability是SoC IC設計的核心。如果說在IP模塊設計中更多體現物理背景的話,包括電路的、器件的、工藝的,甚至分子的、原子的,那么系統級設計將更多體現系統背景,包括功能的、行為的、算法的、架構的、設置思路的。赤橙黃綠青藍紫,系統集成的廣譜背景襯映著一個七彩紛呈的絢麗世界。

-

嵌入式

+關注

關注

5087文章

19148瀏覽量

306186 -

IC

+關注

關注

36文章

5965瀏覽量

175803 -

soc

+關注

關注

38文章

4182瀏覽量

218515

發布評論請先 登錄

相關推薦

一種嵌入式Web服務器的設計方案

嵌入式SoC IC 的設計方法和流程

基于SOC技術的智能型嵌入式數據庫研究

汽車嵌入式SoC系統的應用與發展

嵌入式linux系統GUI設計方案

嵌入式圖形用戶界面系統方案

嵌入式軟件技術應用設計方案匯總

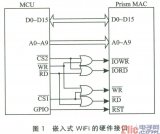

基于嵌入式環境的WiFi通信設計方案詳解

嵌入式Linux串口擴展的驅動設計方案解析

何為嵌入式SoC IC,嵌入式SoCIC的設計方案解讀

何為嵌入式SoC IC,嵌入式SoCIC的設計方案解讀

評論