1 引言

從1976年美國數據加密標準算法(DES)公布以來,到20世紀末,DES算法或其某些變形基本上主宰了對稱算法的研究與開發進程。隨著密碼分析水平、芯片處理能力和計算技術的不斷進步,DES的安全強度已經難以適應新的安全需要,其實現速度、代碼大小和跨平臺性均難以繼續滿足性的應用需求。因此,AES(高級加密標準)應運而生。作為DES的繼承者,AES自從被接納為標準之日起就已經被工業界、銀行業和行政部門作為事實上的密碼標準。在網絡通信和某些工業控制應用場合,對加密速度的需求成為對AES算法的最關鍵要求,同時功耗成為日漸突出的問題,必須進行低功耗設計。

2 AES加密算法簡介

AES是一個密鑰迭代分組密碼,對加密來說,輸入是一個明文分組和一個密鑰,輸出是一個密文分組。它將分組長度固定為128比特,而且僅支持128、196或256比特的密鑰長度,本文僅對密鑰長度為128比特的情況進行討論。

加密過程包括一個初始密鑰加法,記作AddRoundKey,接著進行9次輪變換(Round),最后再使用一個輪變換(FinalRound)。輪變換由SubBytes、ShiftRows、MixColumns 和AddRoundKey 共4個步驟構成。輪變換及其每一步均作用在中間結果上,將該中間結果稱為狀態,可以形象地表示為一個4*4字節的矩陣。

3 AES的改進算法(T盒算法)

假設加密過程中輪變化的輸入為a,輸出為d,則:

上式中SRD(S盒)由有限域GF(28)中的乘法逆變換和GF(2)中的仿射變換復合而成,符號 代表有限域GF(28)中的加法運算,符號 代表有限域GF(28)中的乘法運算。

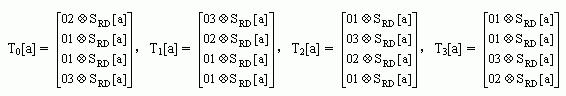

這樣我們可以定義4個表:T0,T1,T2以及T3:

則d簡化為:

該實現方案中T0~T3,每個表都包含了256個雙字,一共占用4KByte的空間。在每次循環迭代中,只要通過4次表查詢和4次異或運算,就能快速地得到一次輪操作中一列的運算結果。改進算法有效降低了關鍵時序路徑的傳輸延遲,能夠明顯的提高ASIC工作頻率。

4 CMOS功耗

對于一個CMOS邏輯門,其功耗主要由靜態功耗和動態功耗兩部分組成。靜態功耗是指門處于非活動狀態時的功耗,大部分是由擴散層到襯底,源極到漏極存在的反偏二極管造成的泄露電流產生的。一般來說,泄漏電流功耗在總功耗中所占的比重不到1%。動態功耗是門處于活動狀態下產生的,它又包含兩部分:開關功耗和內部功耗。內部功耗包括對門內部的寄生電容充放電的翻轉電流功耗,以及PMOS管和NMOS管瞬間同時導通所形成的短路電流功耗。對于信號上升(下降)快的電路,短路電流功耗很小,但對信號上升(下降)較慢的電路,短路電流功耗可能要占總功耗的30%以上。開關功耗是對輸出端負載電容充放電的翻轉電流引起的。

5 低功耗設計

該實現方案中主要采用了以下兩種低功耗設計方法。

1) 動態功耗管理

動態功耗管理是一種系統級低功耗設計方法,降低功耗的主要思路是根據芯片工作狀態改變功耗管理模式,從而在保證性能的基礎上降低功耗。在不同模式下,時鐘的頻率可以進行調整,一些空閑模塊甚至整個芯片的時鐘也可能會被停止。還可以通過調整芯片的電壓,進一步降低功耗。由于工作庫的限制,本文沒有對動態電壓管理作進一步的研究。

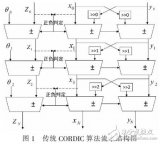

本文采用動態功耗管理,分為normal和idle兩種功耗模式。有開始(START)信號時,芯片由idle模式進入normal模式,開始對明文分組加密。經過初始密鑰加法和10次輪變換,輸出密文分組,并產生結束(STOP)信號,使芯片返回idle模式。因此設計了一個鑒相器產生idle模式的控制信號(EN)。電路由與非門和基本RS觸發器組成(圖1),對輸入信號(開始和結束)的上升沿感應,由D觸發器輸出EN。具有結構簡單的特點,并對噪聲的影響有很好的抑制作用,并能有效地去除毛刺。

2) 時鐘門控

EN有關閉和打開ASIC內部模塊的作用,但這樣不是最佳的,因為EN只是關閉了內部模塊的功能操作,而并沒有把模塊內的時鐘網絡關閉,也就是說時鐘網絡依然處于激活狀態,而時鐘網絡造成的功耗占總功耗的很大部分,只有關閉時鐘網絡才能同時達到關閉模塊功能和降低功耗的目的。

采用時鐘門控技術可以達到關閉時鐘網絡的目的。以圖2(a)中所示電路為例,仿真生成的波形如圖2(b)所示。可以看到只有在EN信號為1和時鐘信號CLK上跳同時發生,ENCLK才會從0變為1,激活時鐘網絡。在其他時刻,時鐘網絡是關閉的。插入的時鐘門控單元不僅能通過關閉時鐘網絡而明顯的降低功耗外,還有其他幾個重要的功能:

① D觸發器的時鐘輸入端口對毛刺敏感,門控單元能有效地濾除信號EN的毛刺,從而確保進入D觸發器時鐘端口的ENCLK信號不會出現毛刺,避免因競爭而導致觸發器發生錯誤的狀態變化。

② 鎖存器的插入增加了ENL信號的延時。

③ 對于n位寄存器組,n條反饋連線和n個多路選擇器被一個門控單元所取代,不僅帶來面

積上的節省,降低后端布線的擁塞,同時又進一步降低了功耗。

6 實現方案

該實現方案采用Synopsys公司的芯片設計流程和VeriSilicon公司0.18μm CMOS工藝。首先根據設計規范,使用Verilog硬件描述語言編寫可綜合的RTL代碼,并對RTL代碼進行仿真。然后對RTL代碼進行綜合。綜合后生成的門級網表和RTL代碼進行等效性檢驗并做靜態時序分析。接著進行版圖設計,先是根據各邏輯單元間的時序采用時序驅動布局策略來做物理布局和全局布線,之后在設計中插入時鐘樹。然后進行詳細布線,并從詳細布線后的版圖中提取出真實的時延值并將其反標給網表,再作等效性檢驗、靜態時序分析和仿真驗證保證滿足時序約束。最后對版圖做設計規則檢查。

7 結論

本文針對AES的ASIC實現,使用改進算法和低功耗設計方法,實現了高速低功耗的AES ASIC設計,其基本思想是:采用T盒算法,只要通過4次表查詢和4次異或運算,就能快速地得到一次輪操作中一列的運算結果,同時在滿足時序約束的前提下,通過動態功耗管理和時鐘門控等方法,根據芯片的工作狀態關閉模塊的功能操作并關閉時鐘網絡,達到了降低功耗的目的。從表1可以清晰地看出,采用T盒算法后,設計的數據吞吐率提高了13.8%,同時采用功耗優化方案后,normal模式下功耗下降了10.7%,在idle模式時更低。該實現方案適用于ECB,CBC等運行模式。

-

asic

+關注

關注

34文章

1206瀏覽量

120682 -

寄存器

+關注

關注

31文章

5363瀏覽量

121006 -

低功耗

+關注

關注

10文章

2418瀏覽量

103862

發布評論請先 登錄

相關推薦

在ASIC的物理設計的低功耗實現技術解析

FPGA設計怎么降低功耗

基于FPGA的AES加密算法的高速實現

基于FPGA的AES加密算法的高速實現

低功耗AES信息安全芯片設計與實現

新型流水線實現高速低功耗ADC的原理及方法

高速低功耗CORDIC算法的研究與實現

高速低功耗的AES ASIC設計如何實現

高速低功耗的AES ASIC設計如何實現

評論