I2S總線協議簡介

I2S(Inter IC Sound Bus)是飛利浦公司為數字音頻設備之間的音頻數據傳輸而制定的一種總線標準,它既規定了硬件接口規范,也規定了數字音頻數據的格式。I2S有三個主要的信號:

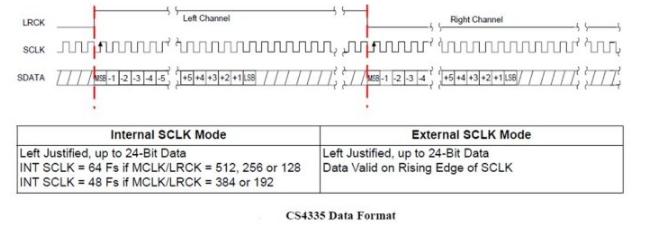

(1)串行時鐘BCLK,也叫位時鐘,即對應于數字音頻的每一位數據,BCLK都有一個脈沖。BCLK的頻率=2×采樣率×采樣位數。

(2)幀時鐘LRCLK,用于切換左右聲道的數據。LRCLK為“1”表示正在傳輸的是右聲道的數據,為“0”則表示正在傳輸的是左聲道的數據。LRCLK的頻率等于采樣頻率。

(3)串行數據SDATA,就是用二進制補碼表示的音頻數據。

有時為了使系統能夠更好的同步,還需要另外傳輸一個信號MCLK,稱為主時鐘,也叫系統時鐘,是采樣頻率的256倍或384倍。典型的I2S接口時序如圖1所示,對于系統而言,產生BCLK和LRCLK信號的信號端是主設備。I2S的數據線用于串行數據,當LRCLK變化(也就是左右通道的數據切換),在第二個BLCK處數據開始,按照高位在先低位在后的順序進行傳輸。數據在BCLK的下降沿改變,在BCLK的上升沿進行數據的采樣。因此,在BCLK的上升沿處數據必須是穩定的,接收端和發送端處理的有效數據的位數可以不同:如果接收端可處理的有效數據的位數多于發送端,將不足的數據位用0補足;反之,則將多余的數據位舍棄。

I2S接口硬件設計

本設計采用Altera公司的Stratix系列的FPGA,EP1S10672I7來實現AD1836中D/A的I2S接口設計。該芯片內核電壓為1.5V,I/O電壓為3.3V,符合AD1836數字接口輸入輸出電平要求,其中D/A部分的I2S接口硬件設計原理圖如圖1所示。

本設計中,將AD1836采樣時鐘設置為48kHz,采樣位數為24位。從AD1836數據手冊可知,其系統時鐘(MCLK)為12.288MHz,左右通道數據切換時鐘(LRCLK)等于采樣時鐘(48kHz),數據位時鐘(DBCLK)為64×左右通道數據切換時鐘(3.072MHz)。所以串行數據線上傳輸的是24位的有效數據,其余數據位時鐘周期對應的數據線上的數據為0,串行數據線DSDATA1、DSDATA2、DSDATA3分別對應于三路的立體D/A,所有的時鐘線和數據線均經過下拉電阻后與FPGA的I/O相連。

基于FPGA的實現

邏輯模塊設計

FPGA內部邏輯模塊主要包括分頻模塊和D_A接口模塊,如圖2所示。其中分頻模塊將AD1836的系統時鐘12.288MHz分頻為3.072MHz(即位時鐘BCLK);start信號為模塊使能信號,為高時,D_A接口模塊將從DATIN引腳輸入的24位并行數據轉換為串行數據,從Datout引腳輸出;當左右通道時鐘切換時,輸入的24位并行數據也相應改變,同時從LRclk引腳輸出48kHz的左右通道數據切換時鐘,從Bclk引腳輸出3.072MHz的位時鐘信號。LRclk和Bclk都是在AD1836的系統時鐘(MCLK)的基礎上分頻得到的,從而保證了整個系統的同步性。

軟件設計

所有軟件的設計是在QuartusⅡ 6.0中采用Verilog HDL語言輸入完成的,系統采用10MHz的有源晶振,通過FPGA內部的鎖相環進行二級倍頻從而得到12.288MHz的時鐘信號,然后通過clkin_12_288M引腳送入分頻模塊。主要的程序如下:

分頻模塊

Module freq3_027M(clkin12_288M, clkout3_027M);

input clkin12_288M; //時鐘輸入引腳

output clkout3_027M; //時鐘輸出引腳

reg clkout3_027M; //分頻計數器

integer cunt;

always@( posedge clkin12_288M) begin

cunt=cunt+1;

if (cunt《=1)

begin clkout3_027M=1‘b0;end

else if((cunt《=3)&&(cunt》=2))

begin clkout3_027M=1’b1;end

else

begin cunt=0;clkout3_027M=1‘b0;end

end

endmodule

D_A接口模塊

(1)左右通道切換時鐘和數據位時鐘

assign LRCLKout = LR_f; //左右通道切換時鐘

assign BCLKout =(BCLK_f)?BCLKin:1’b1; //數據位時鐘

(2)時鐘輸出和數據的并串轉換

always@( negedge BCLKin) begin

if(start) begin //使能信號為高

cunt=cunt+1;

case (cunt)

1: begin LR_f=~LR_f; //左右通道時鐘

BCLK_f=1‘b1;end //送出位數據時鐘

2: datout=DDSdatin[23];//送出最高位

3: datout=DDSdatin[22]; //送出次高位

4: datout=DDSdatin[21];

5: datout=DDSdatin[20];

6: datout=DDSdatin[19];

7: datout=DDSdatin[18];

8: datout=DDSdatin[17];

9: datout=DDSdatin[16];

10: datout=DDSdatin[15];

11: datout=DDSdatin[14];

12: datout=DDSdatin[13];

13: datout=DDSdatin[12];

14: datout=DDSdatin[11];

15: datout=DDSdatin[10];

16: datout=DDSdatin[9];

17: datout=DDSdatin[8];

18: datout=DDSdatin[7];

19: datout=DDSdatin[6];

20: datout=DDSdatin[5];

21: datout=DDSdatin[4];

22: datout=DDSdatin[3];

23: datout=DDSdatin[2];

24: datout=DDSdatin[1];

25: datout=DDSdatin[0]; //數據已經發送完畢

26: datout=0; //剩余的數據送0

27: datout=0;

28: datout=0;

29: datout=0;

30: datout=0;

31: datout=0;

32: datout=0;

default:datout=1’bz;

endcase

end

軟件仿真

模塊的仿真也是在軟件QuartusⅡ6.0中實現的,仿真波形如圖3所示。為了便于仿真,在24位的并行數據輸入口輸入十六進制的常數AB15F7H,此時送入左右通道的數據是相同的。從仿真波形中可以看出,當start信號高有效后,位數據時鐘和左右通道數據切換時鐘送出,將并行的24位數據AB15F7H從數據線上串行送出,在多余的位數據時鐘處數據線上的數據為0,仿真結果與I2S接口時序圖相符合。

結束語

本文以FPGA為控制單元,完成了AD1836中D/A部分的I2S接口設計,它在數字音頻系統的設計中有一定的參考和實用價值。該設計已經成功運用在某話路特性綜合測試系統中,性能良好。

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604656 -

芯片

+關注

關注

456文章

51019瀏覽量

425415 -

I2C

+關注

關注

28文章

1494瀏覽量

124104

發布評論請先 登錄

相關推薦

音頻總線I2S協議:I2S收發模塊FPGA的仿真設計

能幫忙分析下這個電路嗎?AD1836

以AD1836中的D/A為例介紹I2S接口設計

利用MAXIICPLD實現SPI至I2S的接口

音頻接口I2S實驗

基于FPGA和AD1836的I2S接口設計

幾種常見的I2S數據格式

采用FPGA實現AD1836中D/A部分的I2S接口設計

采用FPGA實現AD1836中D/A部分的I2S接口設計

評論