引 言

目前國內急需一種能夠對電火工品的發火過程進行實時無損耗監測的方法和手段,并根據監測結果對火工品的可靠性進行準確的判決和認證,解決科研和生產過程中的具體問題。本系統采用感應式線圈作為非接觸式啟爆電流的啟爆裝置,并采用高速A/D、FPGA、DSP等先進的集成電路實現了電火工品的無損耗檢測。其主要目的是:第一,解決電火工品可靠性試驗中微秒級瞬態信號的檢測、處理和存儲技術;第二,為可靠性試驗提供一種在線的無損耗實時檢測系統,以便對電火工品的發火全過程進行監測;第三,為電火工品的發火可靠性認證和*估提供真實的*價依據,減少或杜絕因拒收產品而出現經濟方面的風險,同時也可減少或杜絕因錯誤地接收產品而出現武器裝備質量方面的隱患。

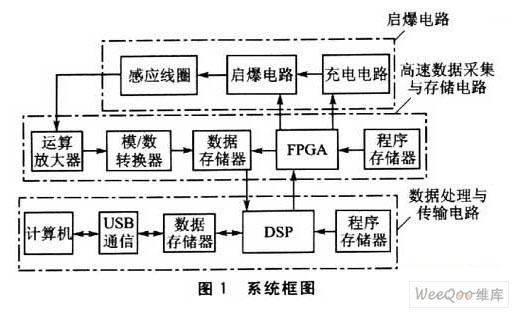

1 系統組成

整個系統的組成如圖1所示。當啟爆電路在DSP和FPGA的控制下啟爆時,感應線圈取出啟爆電流,首先是高速數據采集與存儲電路,以FPGA為核心,對數據進行高速采集與存儲。數據存儲完畢,FPGA發信號告知DSP采集完畢,開始對采集的數據進行相關的處理。DSP對信號處理的內容:首先對信號濾波,然后進行必要的時域和頻域分析,提取相關的信號特征,包括持續時間、信號帶寬、峰值、功率、能量等。處理完的數據通過USB口傳送到計算機,繼而進行專業的相關分析。這里如果采用高速DSP進行數據采集,對于DSP的運算能力是一種浪費。而在高速數據采集方面,FPGA有單片機和DSP無法比擬的優勢。FPGA時鐘頻率高,內部時延小;全部控制邏輯由硬件完成,速度快,效率高.因此有圖1所示的系統組成。

2 硬件電路

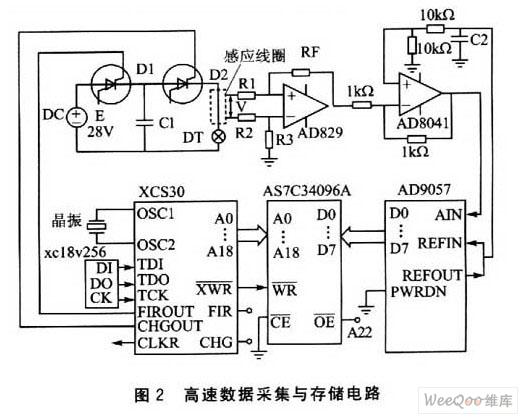

2.1 高速數據采集與存儲電路

為了能夠對作用時間為μs級的電火工品的啟爆電流進行實時監測,采用了由一些大規模集成電路芯片構成的高速數據采集與存儲電路,如圖2所示。

電火工品無損耗檢測的主要內容是對啟爆電流的測量。

電火工品的啟爆電流作用時間為μs級。XCS30是Xilinx公司基于SRAM技術的FPGA芯片,由它發出指令對電容Cl充電并啟爆電火工品DT。非接觸式感應線圈作為啟爆電流的探測裝置,取出電壓。前端調理電路一是擴大可測信號的幅度范圍,設置放大器,對小信號進行放大,以保證足夠的動態范圍;二是為了不給被測信號帶來影響,輸入端應有較高的輸入阻抗。在實驗中測到的電壓帶有噪聲,于是通過濾波器將噪聲濾掉。但這樣處理以后,信號的驅動能力下降,以至于A/D不能正確地采樣,于是加了一級跟隨器,增強驅動能力,這樣A/D就可以正確地采樣了。

XCS30的主要任務是:④控制可控硅D1的導通,使電容器C1充電;②控制可控硅D2的導通,使電火工品啟爆;③在D2導通的同時,啟動A/D轉換,以實現A/D采樣與啟爆信號的同步;④產生地址信號,將A/D輸出的數據存儲到SRAM中;⑤判斷SRAM的存儲空間是否已滿,以便結束A/D采樣,并輸出CLKR信號,通知圖3所示的數據處理與傳輸電路,讀取SRAM中的數據。其中①與②兩項任務是在DSP的控制下進行的,如同3所示,即XCS30接收到DSP的指令后才能完成上述兩項任務。DSP經過XCS30而控制Dl和D2導通的原因,是為了提高負載的驅動能力。也就是說,XCS30的驅動能力比DSP強,可以可靠地使可控硅Dl和D2導通。

實際使用時,數據采集與存儲電路所達到的主要性能是:①采樣速率達到40 Msps,即采樣間隔25 ns;②存儲器容量為512KB;③被采樣信號的最大持續時間為12.8 ms。

被采樣信號因為檢測對象的不同而持續時間有μs級的也有ms級的,因此采樣頻率不能一成不變。經過分析,最小采樣頻率為5 MHz,最大采樣頻率為40 MHz。而FPGA外接晶振的頻率為40 MHz,應該對它進行8分頻。外接一個兩位撥動開關,“00”時對應采樣頻率為40 MHz,“11”時對應的采樣頻率為5 MHz。

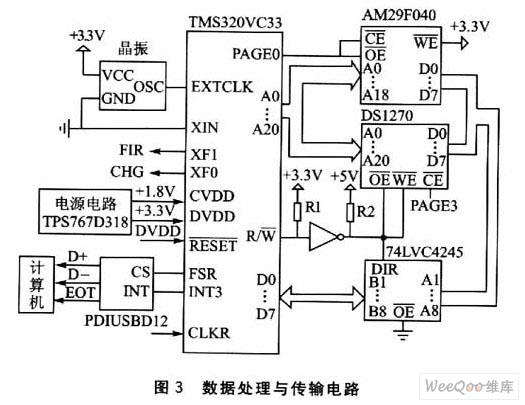

2.2 數據處理與傳輸電路

TMS320VC33是圖3所示電路的核心器件,其主要功能是:①讀取圖2所示SRAM的數據。電路上的連接關系是,TMS320VC33的A19選通AS7C34096A的輸出使能信號OE,DSP的地址線A0~A18及數據線DO~D7分別與SRAM的Ao~A18及數據線D0~D7相接。②對讀取的數據進行處理,包括必要的時域和頻域分析,主要是大數據量的FFT。③通過串行接口芯片將采集和處理后的數據傳輸到計算機。

DSl270是一種非易失性的存儲器。其輸出電壓高電平為5 V,但TMS320VC33的I/O口電平為3.3 V,不能承受高電平為5 V的TTL信號。為了使TMS320VC33與DSl270能交換數據,采用74LVC4245實現3.3V和5V的電平轉換。74LVC4245同時具有3.3 V和5 V兩種供電電源,與DSP相連的I/O腳電平為3.3V,與DS1270相連的I/O腳電平為5 V。

由于TMS320VC33片內設有ROM,掉電后程序和數據信息都將遺失,因此需要外接存儲器。這里選用Flash芯片AM29F040存儲程序,用DS1270存儲數據處理過程中及過程后的數據。電源芯片TPS767D318產生3.3V和1.8 V的電壓給DSP供電;上電后,TPS767D318的復位腳將產生一個低電平,此信號同時將DSP復位,DSP將程序從程序存儲器引導到高速RAM區后開始全速執行。數據進入DSP,DSP對數據進行處理,即進行必要的時域和頻域分析,提取相關信號特征,將處理后的結果再放回DSl270。

3 軟件設計

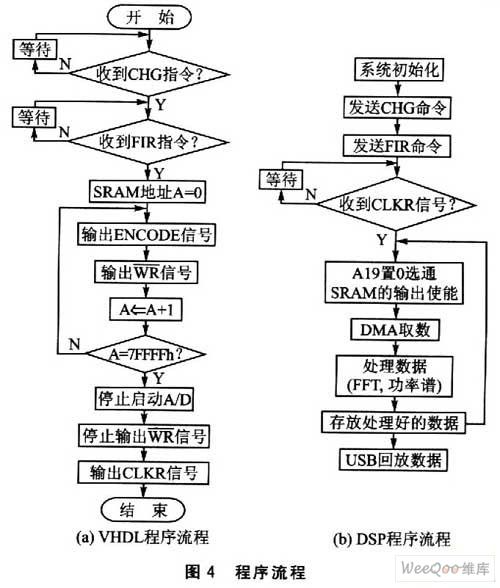

圖2所示電路的核心器件是XCS30,前述5項功能是通過VHDL實現的,其流程如圖4(a)所示。圖中CHG和FIR分別是發給XCS30,并使其發送對電容Cl充電和啟爆電火工品DT的指令;ENCODE是啟動A/D轉換的信號;WR是寫SRAM的信號,地址值A=7FFFFh表示SRAM已滿。這時XCS30輸出CLKR信號,表明采樣和存儲過程已經結束。

圖4(a)分為4個功能模塊:產生發火信號、分頻器、頻率選擇器、地址分配器。圖4(b)為DSP程序流程。

編寫VHDL程序并在ISE7.1中的仿真波形如圖5所示。

4 小 結

DSP的優勢有:數據處理能力強,高速度運算,能實時完成復雜計算,單周期多功能指令,豐富的串口資源。利用DSP強大的數據處理能力和高運行速度的優勢,可以提高分析系統的精度和實時性,滿足監測系統的更高的性能要求。由于將DSP與FPGA等高新的芯片運用到該系統中,一片可以實現許多功能,蹦此減少了使用的其他器件,精簡了主板系統;特別是增加功能比較方便,只需修改軟件。這樣,相對降低了整個系統的成本,而且增強了整個系統的性能。

-

dsp

+關注

關注

553文章

7998瀏覽量

348942 -

FPGA

+關注

關注

1629文章

21736瀏覽量

603420 -

芯片

+關注

關注

455文章

50816瀏覽量

423674

發布評論請先 登錄

相關推薦

利用FPGA和DSP實現信號檢測系統設計

利用FPGA和DSP實現信號檢測系統設計

評論