同步串行通信在航天工程領域中有著廣泛的應用,其中,三線制同步串行通信以其連線少、操作方便、通信速度快等特點,被成功應用在與外圍串行設備的數據通信中。

目前大多數微控制器或微處理器都配置有同步串行通信接口,但含有三線制同步串行通信接口的微控制器或微處理器卻不多,因此在需要應用三線制進行通信的場合,就需要對系統進行三線制同步串行通信接口的擴展,利用FPGA[2]可以實現三線制同步串行通信。由于FPGA具有工作速度高、可配置性強、靈活性好等突出優點,可以滿足高速同步串行通信。根據三線制同步串行通信機制,通過采用Xilinx公司的FPGA器件[3]設計并實現了三線制同步串行通信控制器的IP軟核。該控制器具有高速、易調試、配置靈活等優點,有效利用了FPGA內部硬件資源,減小了系統體積,縮短了系統開發周期。

1 三線制同步串行通信機制介紹

在計算機領域內,有串行傳送和并行傳送兩種數據傳送方式。并行數據傳送中,數據在多條并行1 bit寬的傳輸線上同時由源端傳送到目的端,這種傳送方式也稱為比特并行或字節串行。串行數據傳送中,數據在單條1 bit寬的傳輸線上,逐位按順序分時傳送。

同步傳輸過程中,發送端和接收端必須使用共同的時鐘源才能保證它們之間的準確同步。同步傳輸時,在幀同步脈沖信號觸發下,串行數據信息以連續的形式發送,每個時鐘周期發送1 bit數據。因此,同步傳輸時數據成批連續發送,信息字符間不留任何空隙,它嚴格按照約定的速率發送和接收。為達到接收和發送的準確同步,通常在發送端利用編碼器把要發送的數據和發送時鐘組合在一起,通過傳輸線發送到接收端,在接收端再用解碼器從數據流中分離出接收時鐘。常用的編碼解碼器有曼徹斯*和NRZ-L碼。

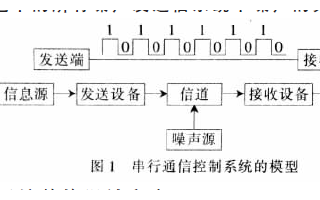

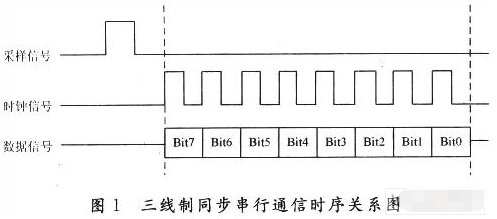

三線制同步串行通信采用的碼型為NRZ-L碼,其時序邏輯關系如圖1所示。

圖1三線制同步串行通信邏輯關系圖

三線制同步信號包括:幀同步信號、時鐘信號和串行數據,通常采用中斷方式接收。串行數據接收或發送時,首先幀同步信號先觸發一個瞬時脈沖,之后保持低電平有效,數據在時鐘信號的上升沿保持穩定,并開始采樣,每個時鐘周期接收或者發送一位串行數據,直至數據接收或者發送完畢,系統再轉而處理其他相關操作。在數據發送或接收的整個過程中,幀同步信號一直處于低電平不變。

2 三線制同步串行通信控制器IP核設計

本設計最終目標是用硬件描述語言VHDL[4]構建一個三線制同步串行通信控制器,也就是建立一個基于FPGA實現的、可復用的IP核[5]。同時,可以將設計好的IP核保存,作為一個子模塊應用于其他需要此模塊的系統中,從而減輕大型設計的工作量,縮短開發周期。

2.1 三線制同步串行通信控制器IP核接口描述

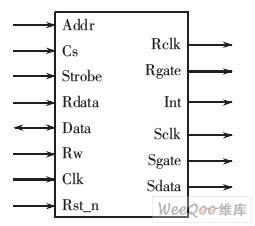

本設計最終實現的目標是生成如圖2所示的IP核接口封裝。

圖2 三線制同步串行通信控制器IP 核接口封裝圖

其中,三線制同步串行通信控制器IP核接口信號定義如表1所示。該IP核共有全局信號管腳8個,接收接口信號管腳和發送接口信號管腳各3個。

表1三線制同步串行通信控制器IP核接口信號描述

2.2 三線制同步串行通信控制器IP核電路結構設計

按照設計目標,根據需要實現的功能,可將三線制同步串行通信控制器結構劃分成幾個大的功能模塊,這些模塊獨自完成一定的任務,結合起來實現通信控制器的整體功能。同時,劃分模塊功能后,可以更方便地用硬件描述語言VHDL對其進行描述。

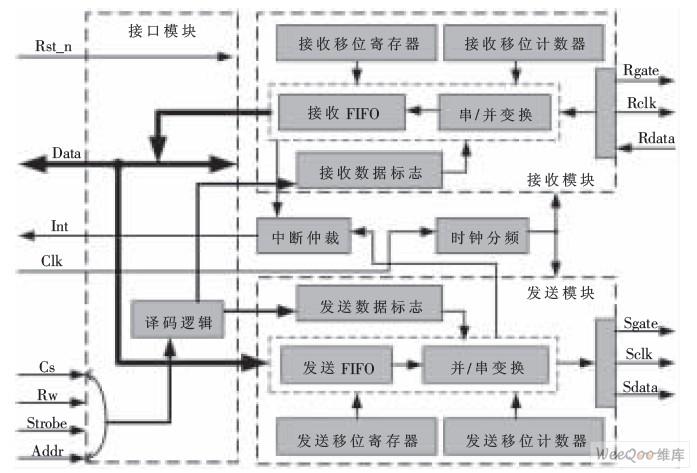

如圖3所示,根據設計要求,可將三線制同步串行通信控制器劃分成3個主要功能模塊:接口模塊、接收模塊和發送模塊。

圖3 三線制同步串行通信控制器結構圖

(1)接口模塊:用于各種全局信號的邏輯組合譯碼控制。同時,對輸入的系統時鐘進行時鐘分頻,為接收模塊和發送模塊提供串行同步時鐘信號。

(2)接收模塊:用于接收外圍串行設備傳來的串行數據,此功能模塊的核心是接收FIFO和串/并變換兩大模塊,其中接收FIFO作為數據緩沖器暫存接收到的數據。在接收數據標志、接收移位寄存器和接收移位計數器的配合驅動下,串行數據按照MSB先、LSB后的順序經過串/并變換后,并行數據被存儲于接收FIFO中,等待中斷響應后CPU對數據進行處理。

(3)發送模塊:用于向外圍串行設備發送串行數據,此功能模塊的核心是發送FIFO和并/串變換兩大模塊。CPU將要發送的數據先放到系統的并行數據總線上,并被暫存于發送FIFO中,在響應發送中斷信號后,并行數據按照MSB首發、LSB后發的順序,在控制信號驅動下,經過并/串變換,發送的數據最終以串行數據格式被送往外圍串行設備端口。

三線制同步串行通信控制器IP核實體名接口用VHDL語言定義如下:

PORT( Rst_n:IN STD_LOGIC;

Clk:IN STD_LOGIC;

Cs:IN STD_LOGIC;

Strobe:IN STD_LOGIC;

Rw:IN STD_LOGIC;

Addr:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

Rdata:IN STD_LOGIC;

Rclk:OUT STD_LOGIC;

Rgate:OUT STD_LOGIC;

Int:OUT STD_LOGIC;

Sdata:OUT STD_LOGIC;

Sclk:OUT STD_LOGIC;

Sgate:OUT STD_LOGIC;

Data:INOUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END SerSendRec;

3 仿真與驗證

利用Xilinx ISE和ModelSim SE工具平臺對三線制同步串行通信控制器IP核進行綜合和功能仿真。數據發送仿真波形如圖4所示,數據接收仿真波形如圖5所示。可以看出,仿真結果完全正確,符合設計的預定目標。

圖4 數據發送仿真波形

圖5 數據接收仿真波形

從圖4的仿真波形中可以看到,data信號線上是系統要向外圍串行設備發送的并行數據,在各種控制信號邏輯組合滿足情況下,系統響應發送中斷信號Int后,CPU先將待發送的數據暫存在04H地址緩沖寄存器中,在幀同步脈沖信號Sgate正脈沖觸發下,每個Sclk周期發送一位串行數據Sdata。圖中并行數據99H和E3H對應的串行數據分別為“10011001”和“11100011”。

同理,從圖5可知,當開始接收數據時,在Rgate正脈沖觸發下,Rdata數據信號線上待接收的二進制串行數據通過串/并變換成“11101010”和“11010111”,并分別暫存在07H和06H所對應的地址緩沖寄存器中,在接收中斷信號Int響應下,將對應的并行數據“EA”和“D7”傳送到系統數據總線上,CPU對數據進行處理。

本文在對三線制同步串行通信機制進行介紹的基礎上,對三線制同步串行通信控制器IP核進行了結構劃分和詳細設計,并結合Xilinx公司的FPGA器件,采用VHDL硬件描述語言,對設計方案進行了仿真與驗證,通過功能仿真波形得出了設計方案的正確性,并被成功用于航天某工程項目中。因其兼具較高的數據傳輸率和IP核的可移植性,可以預見,其在通信領域中將具有更加廣闊的發展空間。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603910 -

控制器

+關注

關注

112文章

16384瀏覽量

178334 -

vhdl

+關注

關注

30文章

817瀏覽量

128159

發布評論請先 登錄

相關推薦

三線制Microware同步串行EEPROM在MCS-51單

基于FPGA的PCIe總線接口的DMA控制器的實現并進行仿真驗證

采用VHDL預言實現基于Petri網的并行控制器設計并進行仿真驗證

如何使用FPGA進行串行通信控制系統的設計

通過FPGA與VHDL設計三線制同步串行通信控制器并進行功能仿真

通過FPGA與VHDL設計三線制同步串行通信控制器并進行功能仿真

評論