與非門介紹

先通過文章《非門(反相器)介紹》了解什么是PMOS,什么是NMOS,以及基本的上下拉CMOS邏輯的概念。

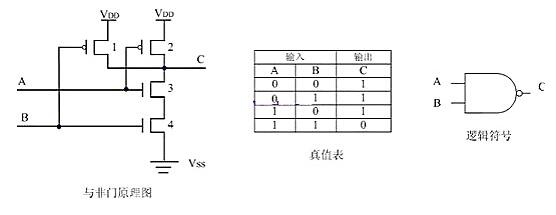

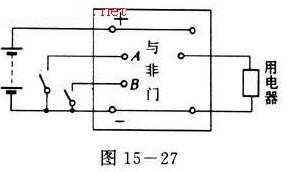

與非門實現的邏輯功能為所有的輸入信號,只要有一個為低電平(0),則輸出為高電平。以2輸入與非門為例,其圖示如下。其中in1,in2為兩個輸入信號,out為輸出。

其邏輯真值表如下。

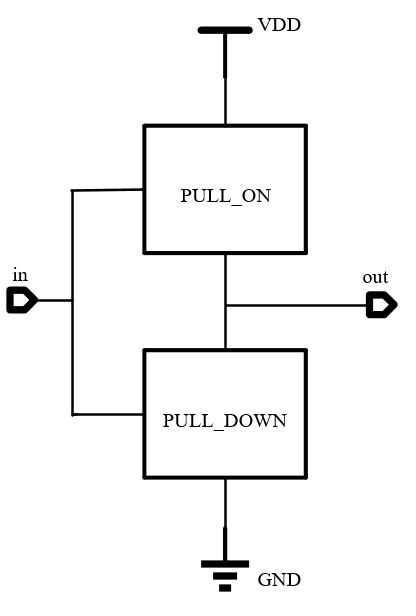

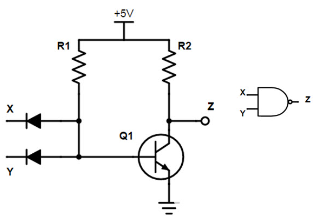

所有邏輯門電路的CMOS結構分為上下拉兩部分,上拉為PMOS結構,下拉為NMOS結構。

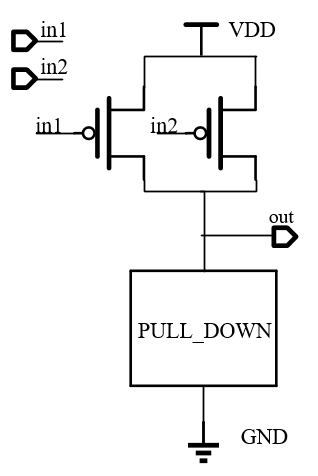

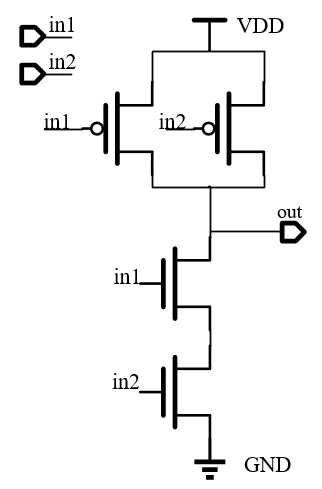

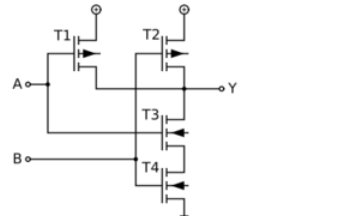

我們來分析一下對于2輸入與非門上拉邏輯要實現的功能:即當in1,in2有任何一個為0時,上拉通路就導通,使得out與VDD相連。故上拉邏輯由兩個PMOS管并聯。PMOS管只有當G端為0時,D與S兩端才導通,故如下圖所示,當in1,in2任何一個為0時,out便與VDD導通,滿足條件。

我們接著分析2輸入與非門下拉網絡要實現的功能:只要當兩個輸入都為1時(高電平),那么下拉網絡才導通,使得out與地相連,輸出為0。根據這個要求,故下拉網絡由兩個NMOS管串聯。NMOS管只有當G端為1時,D與S兩端才導通,故兩個NMOS管串聯,當兩個NMOS管都導通,out才跟地端相連了,符合要求。

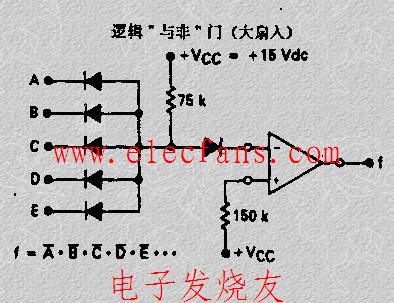

故同樣分析,3輸入與非門上拉網絡為3個PMOS管并連,下拉網絡為3個NMOS管串聯。

或邏輯的Verilog描述符為 “&”。

當用數據流方式描述時,Verilog語言如下:

assign out = in1 & in2;

當用結構級語言描述時(即與門電路的例化),Verilog語言如下,and為或的關鍵字:

and(out,in1,in2);

或非的關鍵字為nand,如果是做或非操作,例化或非門的方式如下:

nand(out,in1,in2);

問題:那么怎么由CMOS結構實現與門呢?

答:在與非門后面加個反相器。

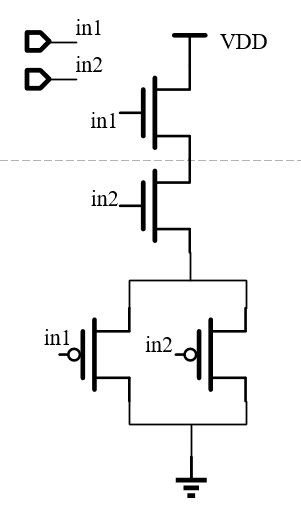

問題:為什么不能如下圖所示,由NMOS做上拉網絡,而PMOS做下拉網絡實現與邏輯呢?

答:因為NMOS做上拉網絡會有閾值損失,PMOS做下拉網絡也會有閾值損失。

-

CMOS

+關注

關注

58文章

5718瀏覽量

235516 -

電平

+關注

關注

5文章

360瀏覽量

39900

原文標題:與邏輯介紹

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

與非門實現非門功能方法介紹

兩個與非門電路的介紹

MOS與非門或非門構成原理

與非門邏輯介紹

與非門邏輯介紹

評論