在學習一門技術之前我們往往從它的編程語言入手,比如學習單片機時,我們往往從匯編或者C語言入門。

所以不少開始接觸FPGA的開發人員,往往是從VHDL或者Verilog開始入手學習的。

但我個人認為,若能先結合《數字電路基礎》系統學習各種74系列邏輯電路,深刻理解邏輯功能,對于學習HDL語言大有裨益,往往會起到事半功倍的效果。

當然,任何編程語言的學習都不是一朝一夕的事,經驗技巧的積累都是在點滴中完成,FPGA設計也無例外。下面就以我的切身體會,談談FPGA設計的經驗技巧。

功能足夠強大的可編程器件PLD/FPGA - Altera/Intel的MAX10

我們先談一下FPGA基本知識

1.硬件設計基本原則

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。

它是作為專用集成電路領域中的一種半定制電路而出現的,既解決了定制電路的不足[功能固定,后期修改不靈活],又克服了原有可編程器件門電路數有限的缺點。

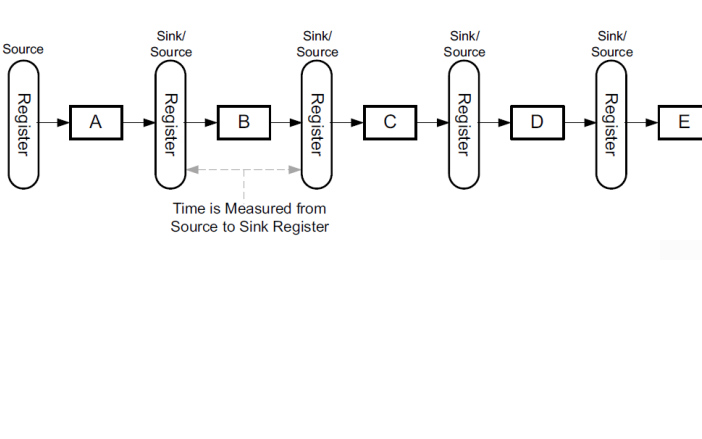

一個設計如果時序余量較大,所能跑的頻率遠高于設計要求,能可以通過模塊復用來減少整個設計消耗的芯片面積,這就是用速度優勢換面積的節約;

反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么可以通過數據流串并轉換,并行復制多個操作模塊,對整個設計采用“乒乓操作”和“串并轉換”的思想進行處理,在芯片輸出模塊處再對數據進行“并串轉換”。從而實現了用面積復制換取速度的提高。

[上面兩段講得有點晦澀,通俗的意思也就是說一個人干不過來的活,可以多個人同時干,這樣速度就快了, FPGA硬件資源豐富,可以通過多個功能模塊并行處理的方式加快系統整體的處理速度]

● 硬件原則: 理解HDL本質。

● 系統原則: 整體把握。

● 同步設計原則: 設計時序穩定的基本原則。

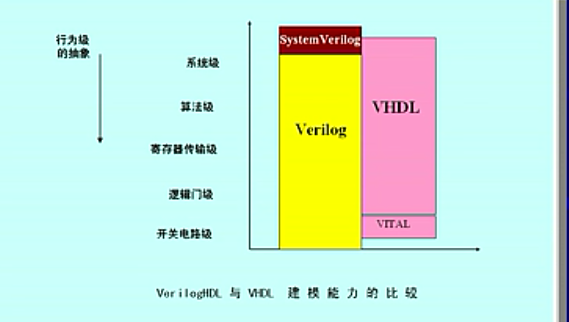

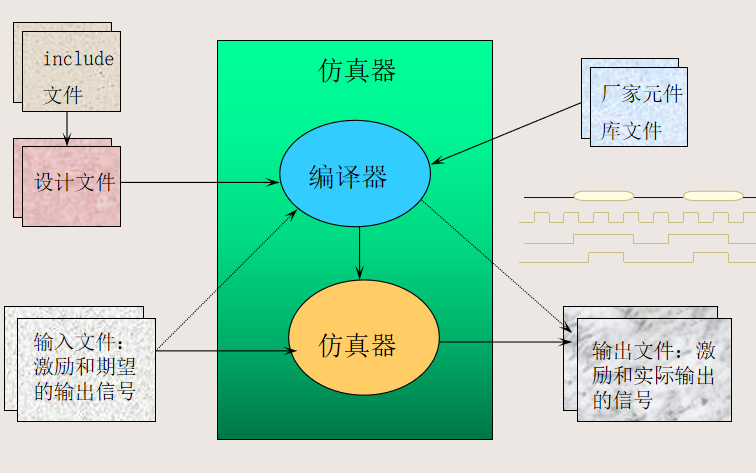

2.Verilog作為一種HDL語言, 對系統行為的建模方式是分層次的

比較重要的層次有系統級、算法級、寄存器傳輸級、邏輯級、門級、電路開關級。

3.實際工作中,除了描述仿真測試激勵時使用for循環語句外,極少在RTL級編碼中使用for循環

這是因為for循環會被綜合器展開為所有變量情況的執行語句,每個變量獨立占用寄存器資源,不能有效的復用硬件邏輯資源,造成巨大的浪費。一般常用case語句代替。

4. if…else…和case在嵌套描述時是有很大區別的

if…else…是有優先級的,一般來說,第一個if的優先級最高,最后一個else的優先級最低。而case語句是平行語句,它是沒有優先級的,而建立優先級結構需要耗費大量的邏輯資源,所以能用case的地方就不要用if…else…語句。

補充:1.也可以用if…; if…; if…;描述不帶優先級的“平行”語句。

5.FPGA一般觸發器資源比較豐富, 而CPLD組合邏輯資源更豐富

【其實這句話說的不對,CPLD的規模一般較小,速度快,內部的寄存器尤其是塊狀寄存器少,而FPGA只是內部的寄存器資源非常豐富,組合邏輯也不殺,取決于選用的系列和具體的型號,在同樣的價格下,如果不需要太多的寄存器,而主要需要的是組合邏輯,選擇PLD會更合適】

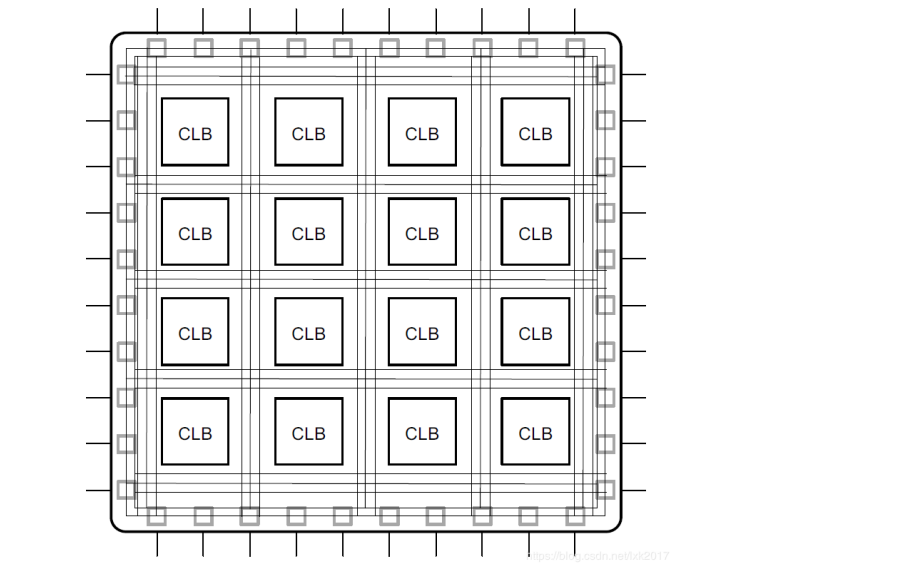

6.FPGA和CPLD的組成

FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等6部分組成。

【時鐘發生器也是很重要的一部分,為了將器件運行在更高的速度,FPGA內部都集成了鎖相環PLL電路】

CPLD的結構相對比較簡單,主要由可編程I/O單元、基本邏輯單元、布線池和其它輔助功能模塊組成。

FPGA內部核心功能

7.Block RAM

3種塊RAM結構,M512 RAM(512bit)、M4K RAM(4Kbit)、M-RAM(64Kbit)。

● M512 RAM:適合做一些小的Buffer、FIFO、DPRAM、SPRAM、ROM等;

● M4K RAM: 適用于一般的需求;

● M-RAM: 適合做大塊數據的緩沖區。

Xilinx 和 Lattice FPGA的LUT可以靈活配置成小的RAM、ROM、FIFO等存儲結構,這種技術被稱為分布式RAM。【Altera/Intel的也可以啊】

補充:但是在一般的設計中,不提倡用FPGA/CPLD的片內資源配置成大量的存儲器,這是處于成本的考慮。所以盡量采用外接存儲器。

8.善用芯片內部的PLL或DLL資源完成時鐘的分頻、倍頻率、移相等操作不僅簡化了設計,并且能有效地提高系統的精度和工作穩定性。

【主要是可以通過外部比較普通的時鐘,就可以在FPGA內部運行到幾百MHz的頻率,并且可以產生各種不同相位的時鐘給不同的時序邏輯】

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604291 -

單片機

+關注

關注

6039文章

44579瀏覽量

636446 -

vhdl

+關注

關注

30文章

817瀏覽量

128174

原文標題:FPGA學習技巧分享

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

學習FPGA需要哪些基礎?怎么學好FPGA?

如何學習FPGA學習FPGA的詳細經驗有哪些階段

FPGA視頻教程之BJ-EPM240學習板的詳細資料介紹

FPGA視頻教程之學習FPGA選擇verilog還是vhdl詳細資料說明

FPGA在深度學習領域的應用

FPGA的學習教程之架構和基本組成單元

FPGA學習教程之硬件設計基本概念

FPGA的Verilog學習教程課件免費下載

Altera FPGA CPLD學習筆記

FPGA學習技巧內容分享

FPGA學習技巧內容分享

評論