今年3月份,賽靈思(Xilinx)歷史上第四位全球CEO Victor Peng 先生在北京正式宣布賽靈思將推出“自適應計算加速平臺”ACAP。Victor 表示:“作為可以和CPU、GPU與FPGA 相提并論、并且性能遠超后二者的產品,ACAP可以覆蓋更加廣泛的應用,幫助人們實現智能互聯并且驅動自適應的世界。”

ACAP采用臺積電7納米技術,在機器學習的計算能力方面比16納米級提升20倍,在5G通信方面能夠支持4倍的帶寬,在性能功耗比方面具有優越的表現。ACAP是賽靈思公司“Everest 行動”(內部稱為“珠穆朗瑪”行動)的重大成果。“Everest 行動”已經歷經四年,投資10億美元、動用1500名工程師,無疑是一個重磅級新型產品。可以說,ACAP的問世,對業界來說是一項重大的技術顛覆,也是自賽靈思公司發明FPGA以來最卓著的工程成就。

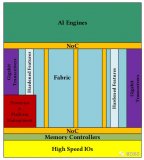

圖1 ACAP架構圖

上圖中的所有其他主要模塊都以某種形式在Xilinx 16nm Zynq、Virtex和Kintex UltraScale+系列中出現過,并不需要詳細說明。這些模塊包括Arm應用和實時處理器、可編程邏輯、HBM(高帶寬存儲器),使用硅基板和2.5D組裝技術連接到Xilinx芯片上的堆疊式DRAM陣列、RFADC和DAC以及高速SerDes端口。

但是那個紅色模塊仍是個謎。這是公司“七面紗之舞蹈”的一部分,它會慢慢揭開Everest 和ACAP產品的細節,從而在設計階段就引起公眾的興趣。(這種營銷技巧的靈感來自于一個世紀前的著名作家和劇作家奧斯卡·王爾德,目前這種技巧受到了高科技營銷人員和真人秀明星的青睞。)

8月份在加利福尼亞州庫比蒂諾舉行的“Hot Chips 30”會議上,揭開了一兩個隱藏著HW和SW可編程引擎的神秘的面紗被揭開。在會議上,Xilinx集團工程總監Juanjo Noguera做了一份詳細報告,標題為“HW/SW可編程引擎:Everest項目的特定架構”。Noguera的演示介紹了許多額外的硬件細節,同時保留了最有趣的細節。

Everest HW/SW可編程引擎是由粗粒度、軟件可編程的VLIW矢量處理器組成的平鋪陣列(tiled array),它們以多種硬件可編程的方式相互連接。Noguera認為,VLIW矢量處理器可以處理各種定點和浮點數據類型。HW/SW可編程引擎陣列出現在下圖的左上角,而具有互連方案的單個模塊細節位于圖中的右下角。

圖2 Xilinx HW/SW可編程引擎對Everest結構的詳細說明

在Everest設計中,HW/SW可編程引擎陣列與PS(處理器系統)和PL(可編程邏輯)獨立通信。陣列中的每個塊的軟件可編程VLIW向量處理器和數據移動器(DMA機器)組成。

陣列中有三種類型的互連鏈路模塊。第一種類型,由圖2中的紅色小箭頭表示,是使用NSEW(北、南、東、西)排列方法將每個模塊與其最近的四個鄰居鏈接起來的平行、雙向數據接口。此外,圖中顯示的綠色小箭頭指向的是單向級聯接口,允許一個瓦片將部分結果直接傳遞給其相鄰的右側鄰居。

這些短的、本地的點到點的連接讓人想起FPGA陣列中用于的短距離LUT-to-LUT通信的本地互連,其級聯接口類似于DSP片之間的進位接口。不過這并不是巧合,因為這些通信路徑在Xilinx設備中一直很常見。

對于平鋪陣列中較長的通信路徑,HW/SW可編程引擎使用200G字節/秒的非阻塞、確定性NOC(片上網絡)。NOC加上并行的本地互連,構成了可編程引擎的“硬件可編程”性。

我們可以以多種方式連接向量處理塊,以實現不同的處理陣列。Noguera在他的演講中討論了五種類似的結構。圖3列出了這些示例:

圖3 Everest HW/SW可編程引擎處理配置示例

配置1是一個簡單的一維單向數據流管道。每個處理塊處理傳入的數據流一部分,然后通過本地內存緩沖區將結果傳遞到下一個塊。配置2是一個數據流圖,該數據流圖可以看成是數據流管道的多維版本。從本質上講,它仍然是管道,不過是在多個維度上運行的。配置3利用NOC將結果從一個處理塊同時多播到兩個或多個后續塊。配置4使用輸入和輸出存儲器緩沖區來匹配連接在NOC上的塊的差分處理速率。配置5可以使用級聯接口將中間結果從一個塊傳遞到下一個塊,而不消耗其他資源。

這只是五個配置示例。使用這種新的處理資源可以創造出更多的處理配置,而且還有一些智能自動化的空間可以合成和優化配置,以滿足高性能、高功率的目標。當然,這些互連方案也可以組合使用。

HW/SW可編程引擎的功能可以使用Everest的片上PL進行擴展,該PL通過多個NOC節點和CDC(時鐘域交叉)緩沖區連接到HW/SW可編程引擎的NOC上,如圖4所示。(顯然,該架構需要CDC緩沖區,因為HW/SW可編程引擎和PL的時鐘速率不同,不過它的運行速度應該不會變慢。)

圖4 HW/SW可編程引擎的NOC通過多個NOC節點和時鐘域交叉緩沖區連接到設備的可編程邏輯。

如圖所示,Everest的HW/SW可編程引擎(圖中縮寫“PE”)與其PL之間的互連總帶寬為Tbytes/sec量級。這將導致許多系統架構師不得不重新思考他們關于處理器體系結構的假設。

我們可以使用連接的PL以多種方式增強HW/SW可編程引擎的能力。例如,可以使用PL的RAM陣列來增加向量處理塊對PL中的片上SRAM (BRAM和UltraRAM)塊的訪問。也可以使用PL來實現硬件加速器,它可以比塊矢量引擎更快地執行特定的計算。Noguera建議使用PL為tile創建“ISA擴展”,但他沒有詳細說明。

機器語言推理和5G無線信號處理的性能結果給人留下了深刻印象,如下圖5所示。

圖5 HW/SW可編程引擎相對于可編程邏輯實現的結果。

值得注意的是ML(機器語言)推理的20倍改進。當涉及到ML推理時,FPGA已經相當快,因為推理計算涉及許多乘法和加法。FPGA中的數以千計的DSP片可以快速地執行這些計算,但是HW/SW可編程引擎似乎更快。Noguera說,5G無線處理中的4倍改進也很重要,因為這意味著珠穆朗瑪峰架構可以達到2G./sec的傳輸速率。

在Noguera演講后的問答環節中,聽眾提出了一些詳細的問題。第一個問題是關于HW/SW可編程引擎的時鐘速率。Noguera的回答是,他還不能直接回答這個問題,但是他試圖通過聲明引擎可以處理2G./sec的5G傳輸比特率來間接回答。他說,HW/SW可編程引擎處理器的工作頻率將是“千兆級”。

另一個問題涉及HW/SW可編程引擎陣列中的模塊數量。答案是每個HW/SW可編程引擎中將有數十到數百個模塊,這取決于設備構成。ACAP設備的HW/SW可編程引擎中有數百個矢量處理器,它們將被大規模并行化。這個范圍與所有FPGA供應商(包括Xilinx)在廣泛的設備家族中將不同數量的資源放置到單個成員中的方式非常一致,并且它傳達了Xilinx開發ACAP設備家族的意圖。

然而,第一款Everest設備還沒有出來。這一里程碑性的計劃將于今年晚些時候實現。同時,七個面紗的舞蹈還在繼續。Noguera承諾將在今年晚些時候在圣何塞、北京和法蘭克福舉行的Xilinx開發者論壇上披露更多細節。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603385

原文標題:秒殺GPU:FPGA發明以來最偉大的技術詳解

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

從FPGA到ACAP,賽靈思再次超越自我

基于7nm工藝的FPGA加速芯片-ACAP

ME結構在FPGA加速芯片ACAP有何作用

勇敢的芯板你玩轉Altera FPGA

【AD新聞】賽靈思新CEO訪華繪藍圖,7nm ACAP平臺要讓CPU/GPU難企及

ACAP的主要架構創新解析

【年度精選】2020年度TOP10榜單——FPGA技術社區問答

晶體管發明史

三張圖解析FPGA/ACAP在AI推理中的優勢

二十世紀最偉大的發明之一--半導體激光器

揭秘賽靈思計算平臺ACAP技術細節

FPGA發明以來最偉大的技術ACAP解析

FPGA發明以來最偉大的技術ACAP解析

評論