同任何IP模塊一樣,存儲器必須接受測試。但與很多別的IP模塊不同,存儲器測試不是簡單的通過/失敗檢測。存儲器通常都設計了能夠用來應對制程缺陷的冗余行列,從而使片上系統(SoC)良率提高到90%或更高。相應地,由于知道缺陷是可以修復的,冗余性允許存儲器設計者將制程節點推向極限。測試過程已經成為設計-制造過程越來越重要的補充。

存儲器測試始終要面臨一系列特有的問題。現在,隨著FinFET存儲器的出現,需要克服更多的挑戰。這份白皮書涵蓋:

FinFET存儲器帶來的新的設計復雜性、缺陷覆蓋和良率挑戰

怎樣綜合測試算法以檢測和診斷FinFET存儲器具體缺陷

如何通過內建自測試(BIST)基礎架構與高效測試和維修能力的結合來幫助保證FinFET存儲器的高良率

雖然這份白皮書以FinFET工藝(制程)為重點,但其中很多挑戰并非針對特定制程。這里呈現的存儲器測試的新問題跟所有存儲器都有關,無論是Synopsys還是第三方IP供應商提供的或是內部設計的。

FinFET與平面工藝比較

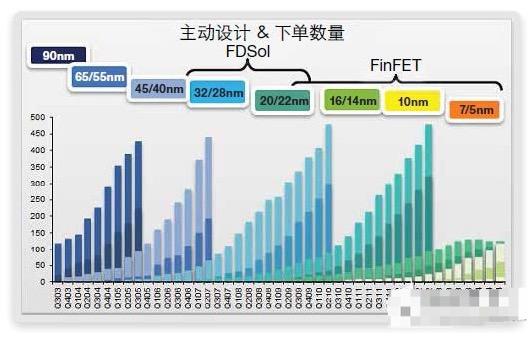

英特爾首先使用了22nm FinFET工藝,其他主要代工廠則在14/16nm及以下相繼加入。自此,FinFET工藝的流行

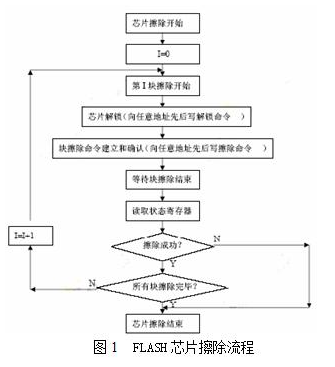

性和重要性始終在增長。如圖1所示。

要理解FinFET架構,設計人員首先應與平面架構進行溝道對比,如圖2所示。左圖標識平面晶體管。改為FinFET的制程相關的主要動機是制程工程師所謂的“短溝道效應”和設計工程師所謂的“漏電”。當柵極下面的溝道太短且太深以至于柵極無法正常地控制它時,即使在其“關閉”的情況下,其仍然會局部“打開”而有漏電電流流動,造成極高的靜態功率耗散。

中間這張圖指示的是FinFET。鰭片(灰色)較薄,柵極將它周圍完全裹住。鰭片穿過柵極的所有溝道部分充分受控,漏電很小。從工藝上說,這種溝道將載流子完全耗盡。這種架構一般使用多個鰭片(兩個或三個),但未來工藝也可能使用更多鰭片。多鰭片的使用提供了比單鰭片更好的控制。

使用多鰭片突出了FinFET與平面架構之間的重大差異。平面工藝使用晶體管寬度和長度尺寸的二維界面。而在FinFET中,鰭片大小是固定不變的,柵極厚度(其定義了溝道長度)也是固定不變的。改變FinFET的唯一參數是鰭片數量,而且必須是整數。比如:不可能有2? (兩個半)鰭片。

FinFET降低了工作電壓,提高了晶體管效率,對靜態功耗(線性)和動態功耗(二次方)都有積極作用。可節省高達50%的功耗。性能也更高——在0.7V上,性能(吞吐量)比平面工藝高37%。

FinFET復雜性帶來了制造困難

與平面工藝相比,FinFET的復雜性一般會導致更加昂貴的制造工藝,至少初期是這樣。隨著代工廠經驗不斷豐富和對工藝過程的控制越來越嫻熟,這些成本可能會下降,但就目前而言,放棄平面工藝的話會增加成本。

FinFET還存在熱挑戰。由于鰭片直立,晶片的基體(襯底)起不到散熱片的作用,這可能導致性能下降和老化。熱挑戰還會影響修復,因為在某些情況下,存儲器不僅需要在生產測試中修復,以后還需要在現場修復。

在使該工藝投產、擴大到量產等情況下,代工廠必須考慮這些挑戰。一般來說,代工廠還要負責存儲器位單元,需要對其做全面分析(通過模擬)和鑒定(通過運行晶圓)。IP提供商,無論是存儲器、標準單元還是接口提供商,也要在構建自己的布局的同時考慮這些問題。

SoC設計人員受到的影響不大,至少對于數字設計流程來說是這樣。一般來說,設計人員見到鰭片的次數絕不會比他們以往見到晶體管的次數更多,除非他們想在其布局與布線工具所使用的,采用金屬結構進行連接的標準單元內部一探究竟。

STAR存儲器系統

Synopsys生態系統(圖3)包括創建布局、完成提取、模擬等需要的所有工具。Synopsys內部各IP小組能夠充分利用完整的Synopsys工具套件來設計、驗證并測試Synopsys IP,包括存儲器在內。

Synopsys已經從最底層起搭建了自己的專門知識。他們與所有不同的FinFET廠家均構建了多個測試芯片:三星、TSMC、英特爾、GLOBALFOUNDRIES和UMC。截止2015年8月,Synopsys運行過的FinFET測試芯片有50個以上。這些芯片均使用了被稱之為DesignWare?STAR存儲器系統?的Synopsys測試和修復解決方案,其中STAR表示自測試與修復。

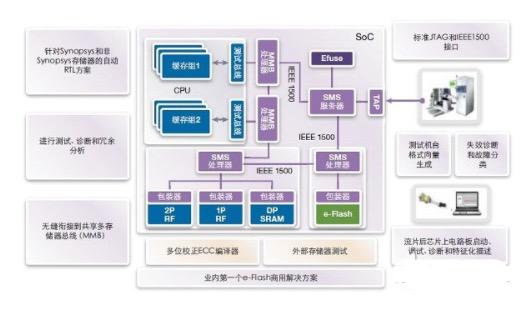

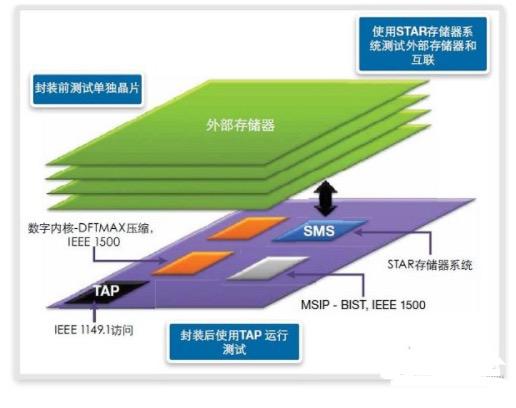

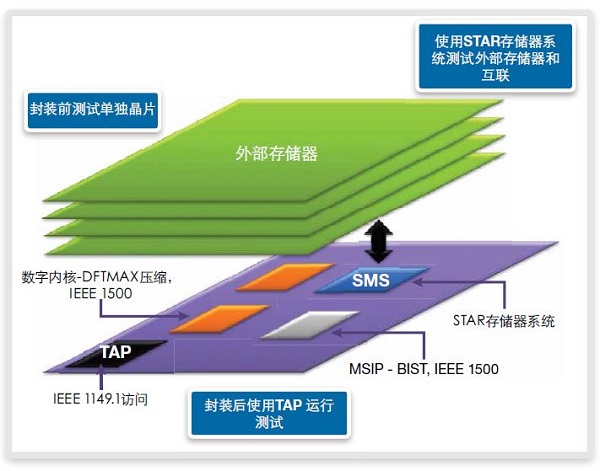

自測試和修復曾經在很多代工藝制程上使用過,不只是FinFET。通過不斷投入,Synopsys改善了STAR存儲器系統。圖4中,STAR存儲器系統用紫色方塊指示。它們包含STAR存儲器系統IP編譯器生成的RTL模塊以應對各種存儲器:SRAM、雙端口、單端口、寄存器文件等。包裝器通過STAR存儲器系統處理器聯系在一起,這些處理器向整個系統的總管理器即STAR存儲器系統服務器報告,而服務器則轉而提供所有必要的調度和握手信號。外部接口則經由JTAG測試訪問端口(TAP)控制器。

每個STAR存儲器系統處理器的能力都足以處理芯片上的檢測、診斷和缺陷修復。連接和配置所有紫色方框可能比較耗時且容易出錯,所以STAR存儲器系統還實現了以下工作的自動化:

生成、插入和確認配置

完成測試向量的生成

執行故障分類

定位失效

糾錯(如果可能)

Synopsys將所有這些自動化步驟映射在FinFET工藝上,以便處理與FinFET存儲器有關的新的分類和失效問題。

自2012年起,Synopsys就一直與產業生態系統中得以較早接觸制程參數的存儲器設計人員合作。在多個FinFET廠家的配合下,Synopsys分析了他們的位單元,也檢查、驗證了他們的模型,創建測試芯片并在Synopsys內部實驗室中直接對硅芯片進行了分析。這個過程讓Synopsys加深了對FinFET缺陷問題的認識,使Synopsys可以優化STAR存儲器系統來解決它們。

因此,如今STAR存儲器系統已被使用在多個方面:

工藝開發:利用STAR存儲器系統特征化描述和理解晶圓制造工藝

IP鑒定:特征化描述和鑒定存儲器IP本身

SoC設計:將STAR存儲器系統納入SoC設計分析中,包括生產測試和修復

管理現場可靠性和老化:處理FinFET工藝中固有的、與鰭片突出和底層熱隔離有關的熱問題。SoC壽命中出現的問題可能是小到軟性錯誤的小問題,它們可以通過糾錯代碼(ECC)自動糾正。但是高可靠性系統中的老化可能需要定期或在上電時使用STAR存儲器系統修復生產測試完成很久以后在現場出現的故障。

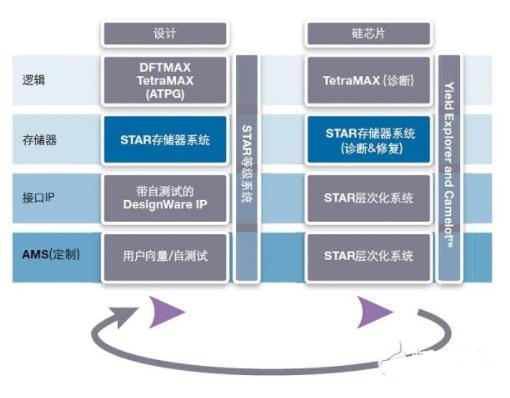

當然,存儲器并非芯片上唯一需要測試的部分。還有邏輯模塊、接口IP模塊、模擬混合信號(AMS)模塊等(也需要測試)。Synopsys提供了一組能與STAR存儲器系統平滑整合的全面的測試和IP方案(圖5)。對于邏輯模塊,Synopsys提供的是DFTMAX?和TetraMax?。接口IP (如DDR、USB和PCIe)有自己的自測試引擎,但它們都能無縫地配合STAR層次化系統(Synopsys的系統級測試方案)一起工作。僅有針對單個模塊的解決方案是不夠的,SoC必須流暢地在頂層上工作。

認識FinFET存儲器故障和缺陷

理解如何測試和修復存儲器之前,設計人員需搞清楚存儲器失效的方式。比如,電阻性故障顯現出來的是邏輯上的性能問題,雖然邏輯通過了測試但無法全速工作。在存儲器中,電阻性故障可以表現為更加微妙的方式。這種故障可能只有在多次操作(一次寫入操作后接著幾次讀操作)之后才引起可檢測性的錯誤,而不是在更標準的一次操作(一次讀操作)后。

設計人員還必須通過研究布局確定哪些錯誤可能真正發生。在數字邏輯測試中,可以通過分析哪些金屬是相鄰的而且可能短路來大幅提高覆蓋率。在存儲器中通過分析信號線可能出現失效等問題所在位置的潛在電阻性短路亦可做到這點。這需要綜合研究布局和分析測試芯片,發現可能的故障。深度分析的需求是Synopsys在多家代工廠中運行50多個FinFET測試芯片的理由之一。來自這些測試的信息用于改進STAR存儲器系統。

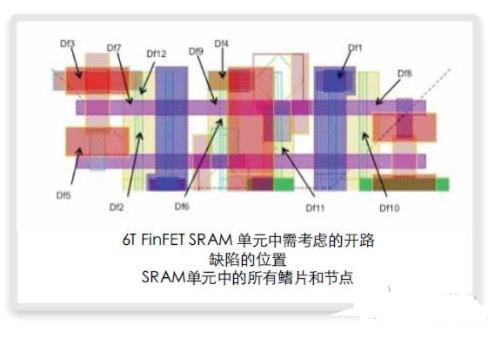

圖6表明了FinFET工藝可能存在的幾種不同的缺陷類型。圖中每個晶體管只有一個鰭片,而實際上每個晶體管的鰭片通常不止一個。當然,開路和短路都可能發生,但在FinFET中它們可能產生不同的表現:鰭片開路、柵極開路、鰭片粘連、柵極-鰭片短路等。每種情形都可能是硬開路或短路,也可能是電阻性的,其中高低不等的電阻值產生不同的表現。

分析布局后,設計人員必須研究拓撲結構,根據晶體管的物理結構判斷故障是否真的會發生。

下一步對設計人員來說要從純晶體管上升一個層級。一個SRAM單元包含六個晶體管,所以要分析這個單元在內部節點中的開路、可能發生的方式以及會產生什么結果。

下一個層次上的目標是單元布局。比如,圖7表示六個晶體管SRAM單元中可能發生的所有可能的開路缺陷。第三,設計人員分析整個存儲器陣列的故障,如位線中的開路、字線之間的短路等等。最后,在模塊級上,整個存儲器,包括周圍的模塊(如地址解碼器)都需要檢驗,就如同讀出放大器那樣。

實際分析通過缺陷注入繼續進行。這基于GDS (版圖)本身。缺陷注入在版圖和SPICE模型上進行,使用了針對每個庫的缺陷庫,然后觀察它們會如何表現。缺陷注入在所有14/16nm FinFET提供商的晶體管上進行,不論是IDM還是代工廠。缺陷注入也在較高節點(如45nm和28nm)的平面工藝上進行。

缺陷注入展示了每種缺陷的行為方式。接下來的任務就是通過測試序列識別(TSI)找到檢測缺陷的測試序列。對于每種潛在的缺陷,一個或多個測試序列得以識別,同樣其檢測的條件及對應的故障模型也被確定。通常需要使用大量的測試序列、應力角和模擬設置,直至找出一個能明顯區別于零缺陷單元的序列。

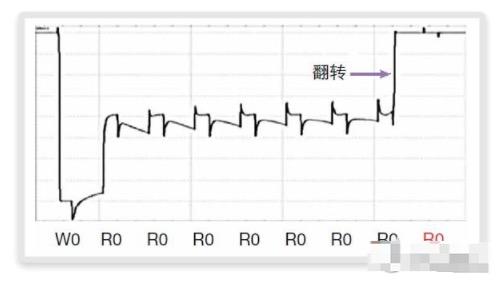

有些情況下,這些缺陷會是以前在平面工藝中見過的故障模型,但FinFET存儲器有幾種額外的失效模式。比如,圖8給出了一種微妙的失效模式。下拉晶體管中的電阻性鰭片開路導致動態偽讀破壞故障(dDRDF)。在此,一個寫操作,接著7個讀操作,導致存儲器單元的位值翻轉。然后可以更加詳細地分析此故障,因為它原來與頻率有關。在1.2MHz頻率上,產生這個故障僅用了4次讀操作,而在4MHz上,則用了18次讀操作。溫度和電壓也會影響這些值。

來自Synopsys關于FinFET工藝故障建模的部分普遍結論是:

FinFET存儲器比平面存儲器對動態故障更敏感

FinFET存儲器對制程變異故障更穩定

靜態單單元和耦合故障在兩種存儲器中均很常見

應力角(電壓、溫度、頻率)對于檢測FinFET故障非常重要,僅使用標稱角會遺漏一些問題。

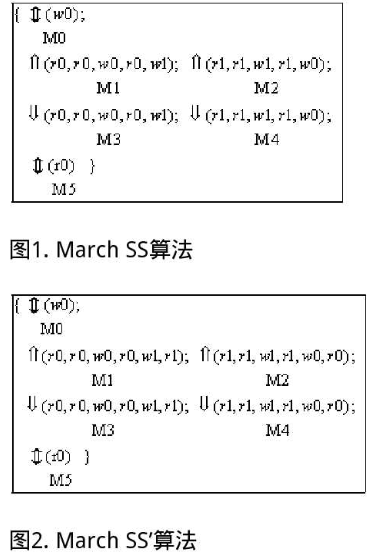

生成測試序列

故障建模背景完成后,設計人員要明確測試的電壓、溫度和頻率要求。給定應力角的序列與稱為測試算法發生器(TAG)的引擎結合。TAG 將與針對個別故障類型的小測試序列組合在一起,產生使測試時間和測試成本最小化的最小測試算法。

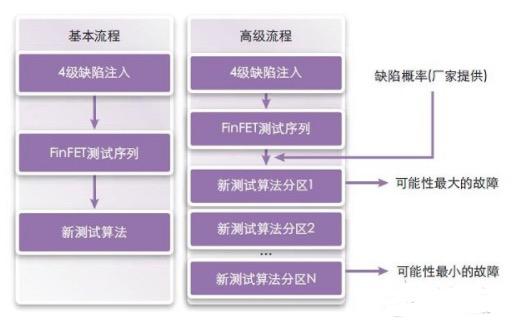

圖9展示了針對FinFET的TAG。圖中的過程是全自動的,從故障注入到測試序列識別再到TAG本身。不同的算法片段可以分割以應對不同的應力角和不同的故障檢測級別。分割形成了一個針對不同條件的測試序列池,這是由于不同用戶和應用具有不同的要求。比如,生產測試期間,設計人員必須識別故障,以便他們能夠糾錯,但是確定每個故障根源的完整分析可能十分耗時。然而,如果某種錯誤經常發生,設計人員會執行更加復雜而昂貴的測試,以縮小故障范圍,從而能采取相應的糾錯措施。

這些過程和測試全部在STAR存儲器系統中得以實現,考慮了來自大多數FinFET提供商的故障,這些故障在不同提供商之間具有很大的共性,盡管位單元彼此相差很大。

STAR存儲器系統還將可編程能力納入其中。可以通過JTAG端口和TAP控制器更新算法,修改測試序列本身或為調試和診斷而升級算法,或者就是簡單的算法升級,甚至是在現場。

使用STAR存儲器系統檢測并修復故障

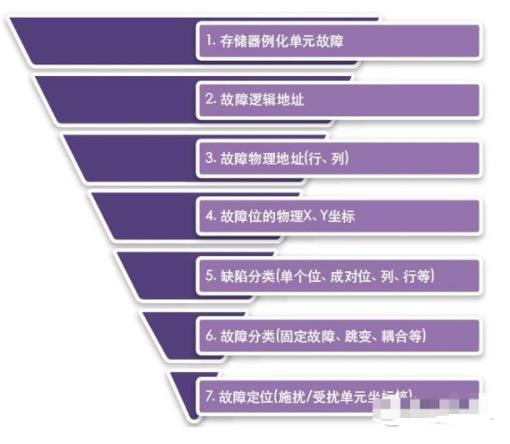

Synopsys對FinFET潛在故障和缺陷的深入而徹底的分析內建在了STAR存儲器系統之中,使得該系統可以在很多層次上使用,如圖10所示。最高層次是了解哪個存儲器例化單元出現失效,這對于生產測試和糾錯可能就足夠了。下一個層次是故障的邏輯地址和物理地址。

STAR存儲器系統可以確定故障位的物理X、Y坐標。缺陷可以分類(單個位、成對位、整列等),故障可以分類并最終精確定位到故障部位。注意,所有這些都由芯片外面的STAR存儲器系統確定,而不是使用電子顯微鏡或其他更精細/昂貴的方式。

開發為SoC用戶(或存儲器IP設計人員)帶來高質量結果的工具和IP是一個漫長而持續的過程。從深入的存儲器設計知識開始,早期接觸多家代工廠的制程參數、大量的故障注入模擬、硅芯片特征化和精確的行為和結構模型,該過程可能需要三年以上。深入理解FinFET特有缺陷得到了對面積影響更小和測試時間更少的優化測試算法,外加對使缺陷易于顯現的應力條件的認識。最后,所有這些知識全部結合在STAR存儲器系統中用于創建自動插入、快速測試和使產出最大化。

FinFET為使用預先插入的一組可調度的存儲器優化時序提供了更多的可能性。BIST多路復用器可隨共享測試總線落實到位。這些測試總線可由定制數據通路創建者和處理器內核進行復用。Synopsys創立了多存儲器總線(MMB)處理器來充分利用FinFET提供的可能性。MMB與映射到該總線上的所有緩存共享BIST/BISR邏輯,因此不再需要存儲器包裝器,減小了面積占用和功率消耗(圖11)。

圖12展示了一個SoC實例,其中部分存儲器傳統地使用STAR存儲器系統,而CPU內核中的存儲器則通過MMB處理器訪問。MMB處理器不直接處理包裝器,而是訪問圖12中紅色方框代表的總線端口。MMB處理器從CPU RTL中讀取信息,理解存儲器細節和寫入總線的配置,引起即時握手。

維修故障

現代存儲器同時具有行和列冗余性(圖13)。檢測到故障時,可以通過在非易失性存儲器中記錄問題和使用維修方案配置冗余列。STAR存儲器系統通過縮小故障范圍和確定置換出故障的方法來自動進行維修。這個過程可以對所有應力角進行優化,故障在一個應力角檢出并擴大到下一個應力角,以此類推。

由于STAR存儲器系統的自動化程度如此之高,診斷和修復可以按預定間隔在現場重復進行,比如系統上電時或按預定的時間長度。這種重復可以通過內建冗余性消除因老化而產生的故障。

負偏壓溫度不穩定性(NBTI)是FinFET最令人頭痛的一個特殊老化問題(平面晶體管沒有這樣的問題)。NBTI主要與溫度有關,會導致取決于 FinFET 工作溫度范圍的性能逐漸下降。

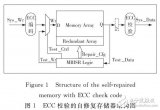

單粒子效應和糾錯

不僅會發生可預測的錯誤,間歇性的軟性錯誤也會發生。間歇性軟性錯誤不需要用內建冗余性修復。它們一般是高能粒子引起的。隨著位單元在較小的制程節點中靠得越來越近,單粒子效應(SEE)可能會影響不止一位,而多位缺陷必須檢測并糾正。

為了應對此類錯誤,STAR存儲器系統包含一個ECC編譯器。該編譯器不僅提供“經典”存儲器ECC(一般允許檢測多位錯誤),而且還能處理一位糾錯。另一方面,該ECC編譯器還能處理多位糾錯。STAR存儲器系統ECC編譯器定義了相關的存儲器配置,用ECC存儲器取代了存儲器(當然,它比需要的數據更寬:一個32位存儲器的寬度約為40位)。然后用所有系統測試和修復邏輯包裝該存儲器。

外部DRAM或memory-on-logic呈現出一組新的挑戰。利用硅通孔(TSV)或其他方法,DRAM的物理位置處在芯片上方,如圖14所示。不過,外界不可以直接訪問存儲器,或者至少沒有達到測試它們所需要的性能。如果它們使用高速接口的話(如DDR4、JEDEC Wide I/O或Micron的混合存儲器立方體),測試工具無法輕易地攔截存儲器與邏輯芯片之間的信號。相反,坐落在SoC上能夠與芯片之外的DRAM交互的引擎則能以需要的高速度驅動這些接口。就像使用片上存儲器一樣,使用外部DRAM的SoC必須找出哪個存儲器、哪一位或者芯片堆疊中的哪個互聯失效及失效原因。STAR存儲器系統能夠滿足這個要求并經常對其進行修復。

STAR層次化系統

所有FinFET SoC都包括存儲器之外的其他模塊。它們會有其他混合信號IP,如PCIe、USB、DDR、PLL等。所有這些接口都需要自測試,很多情況下,故障需要檢測和維修。對快速I/O接口來說,維修意味著調整、校準和組幀。有些接口IP本身就包含存儲器,使得測試和維修更加復雜化。這種復雜系統需要象STAR層次化系統(如圖15所示)這樣的全面測試和維修基礎架構。

STAR層次化系統是對STAR存儲器系統的補充,可以測試、調試和糾正混合信號非存儲器IP。作為一種層次化解決方案,STAR層次化系統能從次芯片級直至整個SoC取得IP及其測試向量,創建存取訪問和接口,并在下一個級別上建立測試向量。

小結

如今Synopsys全面支持各種制程節點,包括14nm和16nm FinFET,而在10nm和7nm工藝上的工作也正在進行之中。利用從這些制程節點的測試芯片中獲得的知識,STAR存儲器系統的各項創新將繼續提高針對嵌入式存儲器的測試和診斷能力,同時增加了優化SoC良率的功能。

Synopsys還提供了STAR層次化系統,通過利用任何現有標準互連(如IEEE 1500)以及TAP控制器全面測試各種其他混合信號和接口IP。

-

FinFET

+關注

關注

12文章

248瀏覽量

90230 -

FinFET存儲器

+關注

關注

0文章

3瀏覽量

4559 -

STAR存儲器

+關注

關注

0文章

2瀏覽量

3985

發布評論請先 登錄

相關推薦

存儲器故障診斷算法實現

基于March SSE算法改善嵌入式RAM存儲器的測試算法

FinFET存儲器的設計挑戰以及測試和修復方法

主流DSP存儲器測試方法學習指南:TI KeyStone

Flash存儲器的故障特征

一種改進的嵌入式存儲器測試算法

檢測和診斷FinFET存儲器具體缺陷和修復方法

一種可擴展的存儲器自修復算法

新型的嵌入式存儲器測試算法[圖]

如何對嵌入式存儲器進行測試和可測性設計?

FLASH存儲器測試程序原理和幾種通用的測試方法

怎樣綜合測試算法檢測診斷FinFET存儲器缺陷資料下載

淺談FinFET存儲器的缺陷修復和測試算法

淺談FinFET存儲器的缺陷修復和測試算法

評論