1 引言

大多數非FPGA類型的、高密度IC(如CPU)對去耦電容都有非常明確的要求。由于這些器件僅為執行特定的任務而設計,所以其電源電流需求是固定的,僅在一定范圍內有所波動。然而,FPGA不具備這種屬性。對于一個設計好的FPGA系統平臺,在綜合時,可以按設計需要的頻率,跨越多個時鐘域,運行幾乎無限多的應用。由于無法確知一個新的FPGA設計的瞬態電流的變化情況,在設計FPGA系統硬件平臺的電源分配系統時,唯一的選擇就是采用保守的最壞情況設計法。

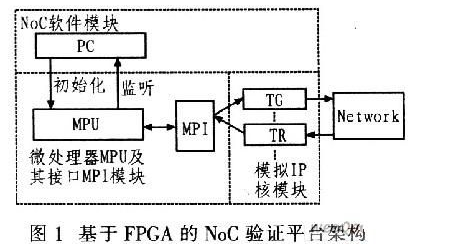

在低噪聲或高功率情況下,電源去耦網絡必須根據瞬態電流的需求準確地度身定制,否則,接地反彈和電源噪聲將超出FPGA的電平限值。高速電路的性能很大程度取決于電源分配系統能否提供穩定、安靜的電源電壓和電流。憑經驗的設計電容去耦網絡,經常造成欠設計(引起EMI和穩定性問題)或過設計(增加系統的成本和復雜度)。因此,在設計系統平臺時,利用電源完整性仿真軟件,對去耦網絡以及電源、地平面對(Power-Ground Plane pair)進行仿真,通過修正電容數量和額定值,調整電容的布局,可以很好地避免欠設計或過設計,使系統目標阻抗滿足要求。本文以基于Xilinx公司的Virtex-4芯片的IC驗證平臺為例,介紹了電源完整性仿真分析方法在電源分配系統中的應用。

2 FPGA平臺的電平及要求

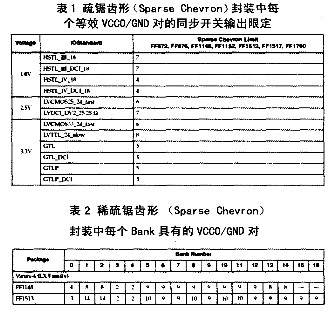

系統采用的FPGA是V4XC4VLX160-FF1513,具有16個I/O Bank。FPGA所使用的電源有:Vc-CINT、VCCO、VCCAUX以及VREF。每個I/O可以支持的電平有:1.2V、1.5V、1.8V、2.5V以及3.3v。由VCCO來決定所在Bank I/O的電平標準。從芯片的用戶手冊可以獲得SSO(Simultaneous Switching Out-put,同步開關輸出)限定信息,來確定該器件所使用的VCCO管腳數量。

在本文設計了5.0V、數字3.3V、數字2.5V、數字1.8V、數字1.2V五個電源分配系統。如下以數字3.3V為例,介紹采用Cadence公司的PCB PI軟件的仿真分析方法。

3 電源完整性仿真分析與設計

3.1 電源分配系統概述

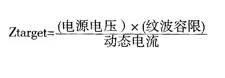

電源分配系統的關鍵參數是目標阻抗,其定義為:

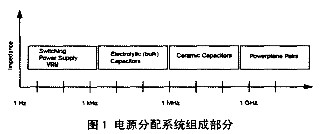

電源分配系統必須在從直流到關注的最高頻率范圍內,以低于或接近目標阻抗來傳遞電流。一個電源分布系統由電壓調節模塊(VRM)、Bulk電容、高頻去耦電容以及電源地平面四個對象組成。它們在不同的頻率范圍內對目標阻抗起到決定性作用。

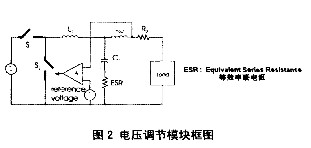

電壓調節模塊將一個直流電平轉換成另一個直流電平。其利用一個參考電壓和反饋環來探測負載處的電壓,并相應調節電流大小。在直流至1kHz頻率范圍內,系統的目標阻抗主要由VRM來決定。

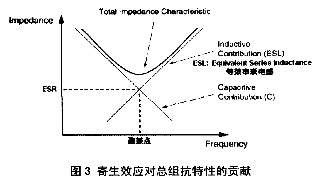

去耦電容分為電解電容(Bulk Electrolytic Ca-pacitor)和高頻陶瓷電容(High-Frequence CeramicCapacitor)。電解電容主要在kHz到1MHz頻率范圍內起作用,而瓷片電容則在較高的MHz頻率(1MHz-400MHz)范圍內起作用。其等效電路是典型的RLC串聯電路。

電源/地平面可以近似為一個電感和有效串聯電阻很小的電容。當頻率很高時(大于400MHz),就需要調節電源/地平面的結構,使系統的目標阻抗滿足要求。

3.2 單節點仿真

根據計算在系統中采用3.3V電平的I/O SSO電流總和不超過10A(由I/O連接的外設以及VCCO來決定)。選擇Artesvn Technologies公司的單輸出10A DC-DC轉換器作為電壓調節模塊(VRM),輸入5.0V,輸出3.3V,取動態電流(Delta Current)為10A,紋波容限(Ripple Tolerance)為5%。于是3.3V/GND電源地平面對的目標阻抗為16.5mΩ。

去耦/旁路電容網絡的設計,一般而言,按電源情況,PDS的每個VCC電源管腳應具備一個電容。將大量電容值并聯組合的目標是在從500kHz到500MHz的頻率范圍內,保持平穩的低電源阻抗。高值(低頻)和低值(高頻)電容都需要。通常,低值電容對總阻抗的影響較小,因此需要使用更多的低值電容,使得其對阻抗的總影響與較少數量的高值電容產生的總影響相同。

為了保持平穩的總阻抗值,防止出現反諧振尖峰,通常,每10倍電容值范圍至少需要1個電容。典型的陶瓷電容值范圍通常為從0.001μF至4.7μF。電容值越多越好,因為這樣產生的總阻抗值越平穩。同時需要考慮PCB板的布局空間以及成本。

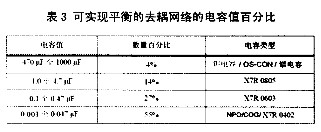

產生相對平穩的阻抗的電容比率為電容值每降低10倍,電容數量約增加一倍。此外,需要鉭電容、OS-CON(SANYO的有機半導體鋁固體電解電容)的電容或其他電解電容等低頻電容。這些高值電容的ESR通常高于貼片陶瓷電容,因此可以在更廣泛的頻率范圍內起作用,也因而不太容易產生反諧振尖峰。所以,不必嚴格遵循每10倍電容值一個電容的規則。一般而言,在從470μF至1000μF的范圍內配置一個值就夠了。表3顯示了可實現平衡的去耦網絡電容百分比(經驗值)。然后通過運行單節點仿真來驗證選擇的不同值的電容數量是否可以在頻率范圍內維持目標阻抗?

對于電容的模型,陶瓷電容可以采用Murata、TDK網站提供的電容模型庫或Cadence Allegro軟件安裝目錄下的參考模型庫。而對于鉭電容,可以使用KEMET以及SANYO等公司的提供的Spice軟件提供的ESR、ESL、諧振頻率以及封裝信息,創建對應的鉭電容模型。

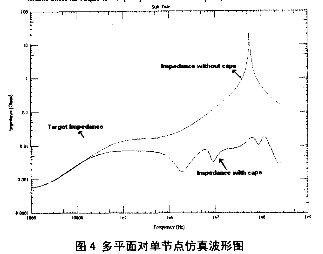

所示為單節點仿真結果(考慮最高工作頻率為266MHz)。由于單節點沒有考慮電容在PCB中的具體位置,SQ-PI提供了一個電容數量的參考值/建議值。然后需要多節點仿真再進行更精確的分析與驗證。

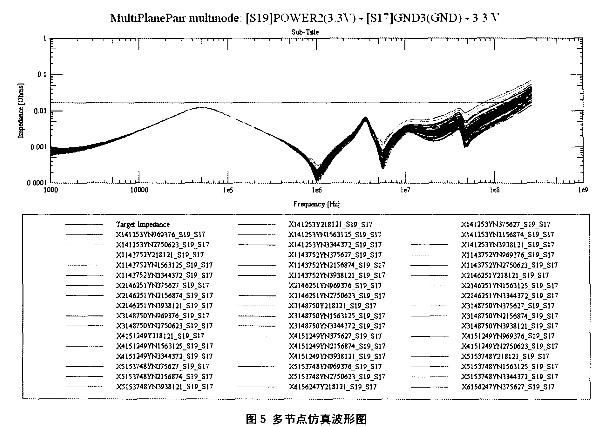

3.3 多節點仿真

單節點仿真可以確定去耦電容的數量,但電源系統的阻抗不僅取決于去耦電容的數量,還取決于電容的分布位置。為了獲得更精確的結果,應該布好去耦電容、噪聲源以及VRM,然后在整個頻率范圍內進行多節點仿真。不同于單節點仿真,此時SQ PI使用一個帶恒流源和恒壓源的理想電路來連接去耦電容和VRM。多節點仿真對物理設計中這些文件的實際布局進行精確的仿真。

多節點仿真通過將電源平而分隔成用戶定義的網絡尺寸,并將VRM、噪聲源以及去耦電容連在網格中合適的節點,通過確定每個節點附近的阻抗來進行更精確的仿真。

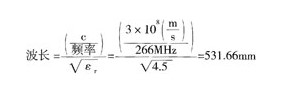

為使仿真最準確,網格中網孔的大小必須大于系統最高頻率對應波長的1/10。系統的最高工作頻率為266MHz(DDR內存模塊),電路板電介質材料是FR-4,介電常數εr為4.5,于是波長如下:

電路板大小為122mm×205mm,故只需4×4的網格就可以準確仿真。為便于分析,本文采用8×8的網格。放置好電容后。

在0-266MHz之間,波形大部分都在目標阻抗以下,超出目標阻抗的波形所代表的網孔都在電路板的邊緣,對電路影響不大,因此電容分布滿足要求。

4 總結

通過電路的實際測量,發現各電源分配系統均能很好的工作,與仿真結果基本一致。為了進一步提高仿真精度,可以通過頻域測試,建立基于S參數或SPICE等效電路的電容模型庫,也有利于提高電源完整性仿真的效率。

本文討論的系統是FPGA的IC設計驗證平臺,其電源完整性的分析方法對于其他類型的電子產品設計也有一定的借鑒意義。隨著系統頻率的提高,電源分配系統越來越復雜,PCB的電源地阻抗諧振現象變得更加突出,直接影響到系統的穩定工作以及產品級的EMI/EMC認證,因此在IC或產品設計早期,應該在系統層面進行電源完整性仿真,模擬真實系統的行為,提前發現系統中潛在的電源問題,從而有利于提高產品系統工作的穩定性,加快產品的開發上市。

-

FPGA

+關注

關注

1629文章

21746瀏覽量

603757 -

pcb

+關注

關注

4319文章

23108瀏覽量

398187 -

IC

+關注

關注

36文章

5954瀏覽量

175698

發布評論請先 登錄

相關推薦

基于FPGA的IC設計驗證平臺的的PCB PI軟件的仿真分析方法

基于FPGA的IC設計驗證平臺的的PCB PI軟件的仿真分析方法

評論