Abstract

在Verilog中,always block可以用來代表Flip-Flop, Combination Logic與Latch,本文比較在不寫else下,always block所代表的電路。

Introduction

在C語言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。

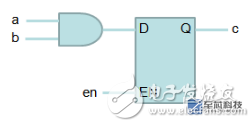

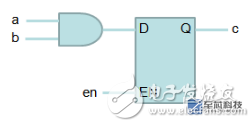

always@(a or b or en)

if (en)

c = a & b;

在combination logic中省略else,由於必須在~en保留原本的值,所以會產生latch。

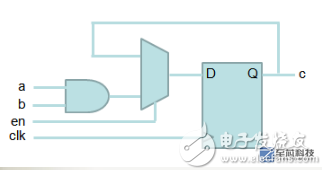

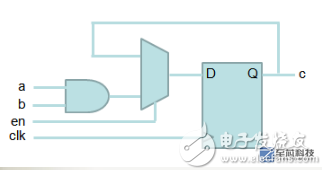

always@(posedge clk)

if (en)

c <= a & b;

雖然也必須在~en保留原本的值,但由於flip-flop就有記憶的功能,所以不會產生latch。if將產生mux,並將flip-flop的值拉回給mux。

Conclusion

在Verilog中,雖然只是小小的差異,但結果卻有天大的差異。

全文完。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

相關推薦

Verilog與ASIC設計的關系 Verilog作為一種硬件描述語言(HDL),在ASIC設計中扮演著至關重要的角色。ASIC(Application Specific Integrated

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:52

?173次閱讀

Verilog測試平臺設計方法是Verilog FPGA開發(fā)中的重要環(huán)節(jié),它用于驗證Verilog設計的正確性和性能。以下是一個詳細的Verilog測試平臺設計方法及

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:50

?340次閱讀

Verilog 與 VHDL 比較 1. 語法和風格 Verilog :Verilog 的語法更接近于 C 語言,對于有 C 語言背景的工程師來說,學習曲線較平緩。它支持結構化編程,代碼更直觀,易于

![的頭像]() 發(fā)表于

發(fā)表于 12-17 09:44

?247次閱讀

OPA380的pspice模型只有5個管腳標號,但是未標明各個管腳所代表的含義,如哪個輸入,哪個輸出,電源之類的。這個怎么辦呢?

發(fā)表于 09-18 06:19

;

else

block_read_valid <= 1\'b0;

end

always@(posedge sys_clk or posedge rst)

begin

if(rst == 1

發(fā)表于 06-21 17:58

endmodule

五、條件判斷語句

條件判斷語句有if else 和 case endcase這兩種,這兩種語句的賦值都必須放在always語句中。

①、if else語句的注意事項

A

發(fā)表于 05-31 18:31

SOC(System on Chip,片上系統(tǒng))設計中,時鐘信號的控制對于整個系統(tǒng)的性能和功耗至關重要。本文將帶您了解SOC設計中的一種時鐘控制技術——Clock Gating,通過Verilog代碼實例的講解,讓您對其有更深入

![的頭像]() 發(fā)表于

發(fā)表于 04-28 09:12

?2382次閱讀

平時工作生活中我們會看到各種顏色的USB口,但是大多數人都不知道不同顏色的USB口代表什么含義?

發(fā)表于 04-09 09:49

?4196次閱讀

;// Output parity bit.

else

tx <= tsr[0];//Shift out data bit.

end

end

always @(posedge mclkx16

發(fā)表于 04-01 14:41

8b/10b編碼是一種用于減少數據線上的低效能時鐘信號傳輸的技術,通過在數據流中插入特殊的控制字符,來同步數據和時鐘。在Verilog中實現(xiàn)8b/10b編碼器可以通過以下步驟完成:

定義8b/10b

發(fā)表于 03-26 07:55

else begin

data_a_reg <= data_in_a;

data_b_reg <= data_in_b;

end

end

// 執(zhí)行卷積運算

always

發(fā)表于 03-26 07:51

在Verilog中實現(xiàn)一個簡單的電子時鐘,你可以使用一個計數器來周期性地遞增一個計數值,然后根據這個計數值來顯示時鐘的不同時刻。以下是一個簡單的例子:

module clock_display

發(fā)表于 03-26 07:48

Verilog可以通過使用IEEE標準的浮點數表示來實現(xiàn)浮點運算。下面是一個基本的Verilog模塊示例,展示了如何進行加法、乘法和除法等常見的浮點運算操作:

module

發(fā)表于 03-25 21:49

Assign語句和Always語句是在硬件描述語言(HDL)中常用的兩種語句,用于對數字電路建模和設計。Assign語句用于連續(xù)賦值,而Always語句用于時序邏輯建模。本文將詳細探討這兩種語句

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:24

?2709次閱讀

Verilog是一種硬件描述語言(HDL),用于設計和模擬數字電路。在Verilog中,關鍵字initial和always都是用于描述電路行為的特殊語句。它們被用來生成仿真模型,并控制模擬器的啟動

![的頭像]() 發(fā)表于

發(fā)表于 02-22 16:09

?3051次閱讀

always block內省略else所代表的電路 (SOC) (Verilog)

always block內省略else所代表的電路 (SOC) (Verilog)

評論