摘要

本設(shè)計是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的雙路低頻信號發(fā)生器。系統(tǒng)應(yīng)用FPGA內(nèi)部特有的可配置IP核和鎖相環(huán)等設(shè)計信號發(fā)生器。整個系統(tǒng)由觸摸屏人機操控界面、紅外操控、信號發(fā)生器、疊加電路組成。信號發(fā)生器可輸出兩路相互獨立的信號,信號類型有矩形波、三角波以及正弦波。兩路信號的頻率、幅值、相位、占空比等參數(shù)都可通過紅外遙控以及觸摸屏調(diào)節(jié)和預(yù)置。頻率的預(yù)置范圍為1000赫茲到2000赫茲,步進值為1赫茲。幅值的預(yù)置范圍為0V~5V,相位的預(yù)置范圍為0°~360°,占空比預(yù)置范圍為0~100%,且步進值都小于1。當兩路波形都為正弦信號時,可以通過疊加電路對兩路正弦信號進行疊加。

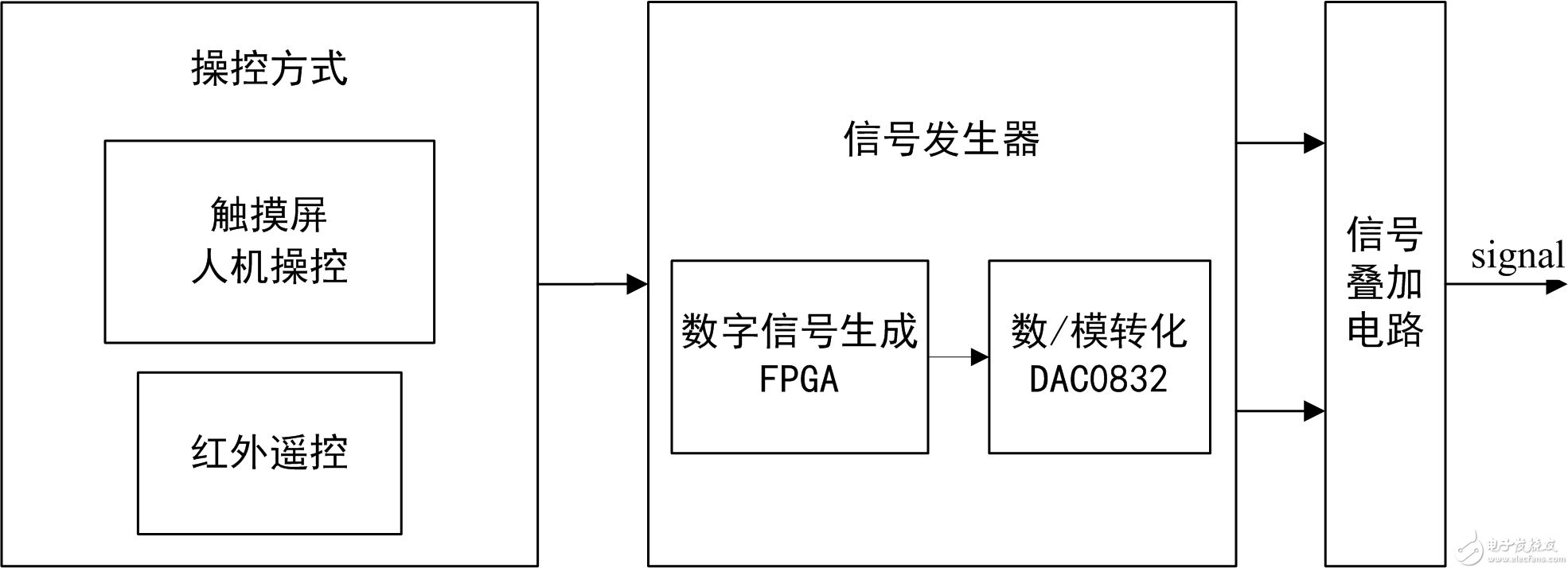

系統(tǒng)結(jié)構(gòu)框

本設(shè)計是以Altera公司的可編程芯片做載體,運用Verilog作為軟件設(shè)計工具,從而實現(xiàn)DDS原理,即信號發(fā)生器的核心思想。再加上信號發(fā)生器的硬件電路就可以輸出特定的信號,也就是本設(shè)計中的數(shù)/模轉(zhuǎn)換電路。從電池兼容EMC考慮,該電路的布局要緊湊的硬件,使導(dǎo)線長度盡可能短。這樣即可以避免內(nèi)部自身線路時間的干擾,也可以避免外界的干擾,適當增加濾波器來屏蔽干擾。這樣就可以提高輸出信號的質(zhì)量。所有信號的參數(shù)可以通過兩種方式程控調(diào)節(jié),即人機操控方式和紅外遙控方式。從圖中可以看出系統(tǒng)主要由觸摸屏人機操控界面、紅外操控、信號發(fā)生器、疊加電路等組成。

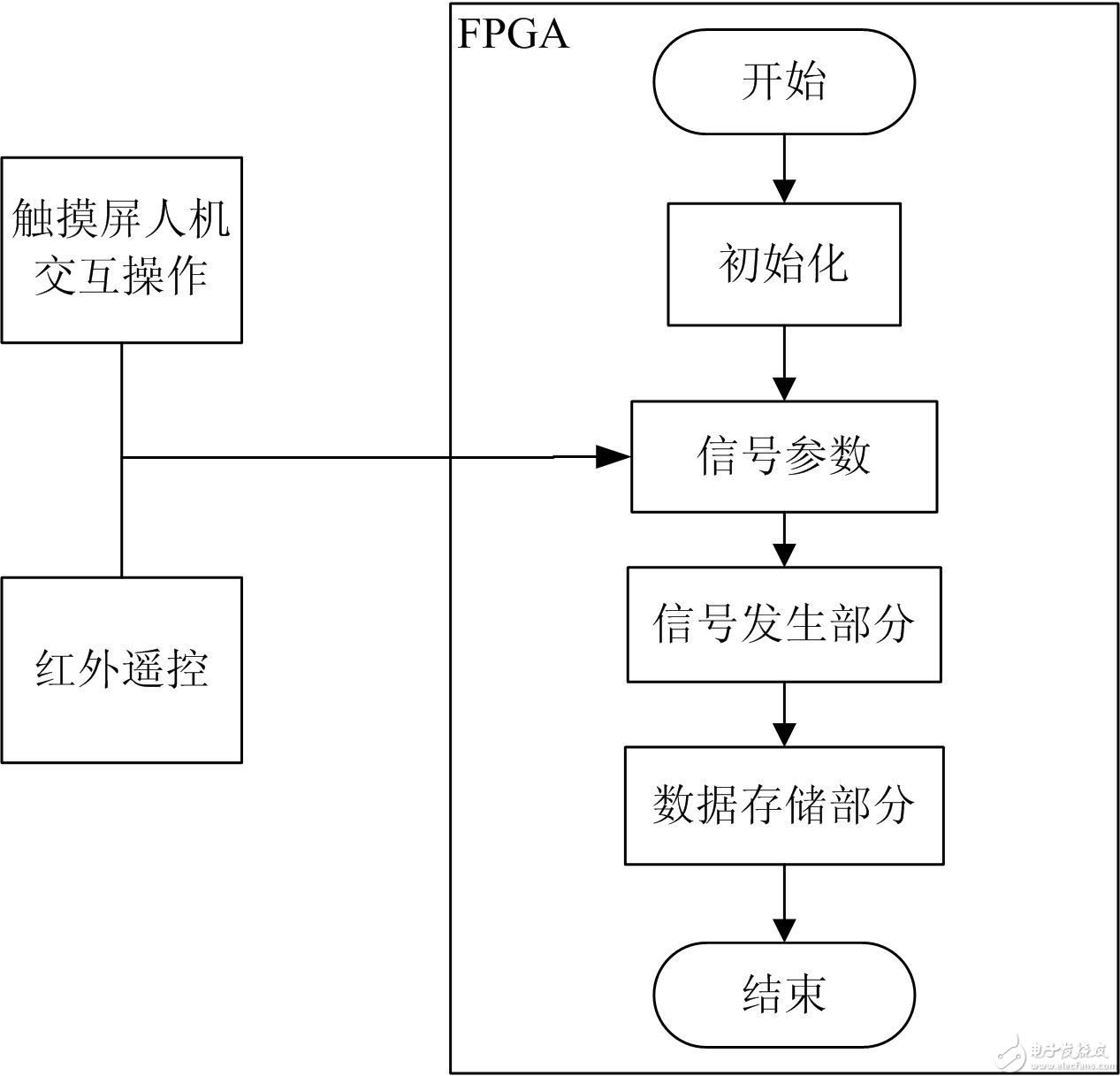

軟件設(shè)計

軟件設(shè)計包括三個部分,控制部分、信號發(fā)生部分、數(shù)據(jù)存儲部分。FPGA的具體程序是采用頂層原理圖分塊編程的方式。控制部分實現(xiàn)觸摸屏和紅外遙控對信號參數(shù)設(shè)置的功能,信號發(fā)生部分產(chǎn)生三種信號,正弦波、方波、三角波,數(shù)據(jù)存儲部分存儲三種信號的波形數(shù)據(jù)。

FPGA軟件設(shè)計采用頂層原理圖模式,正弦波、三角波、矩形波信號發(fā)生器的頂層模塊原理圖,塊內(nèi)是用Verilog語言編寫的程序。

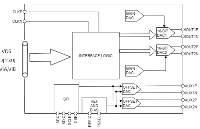

系統(tǒng)電路圖

這是我大學(xué)期間第一次將所做的設(shè)計做出PCB,并且真正打樣焊接出來,這個過程讓我明白設(shè)計文件和打樣出的實物的區(qū)別,需要注意的點。大家能看出來我這次PCB上有哪些錯誤嗎?請留言哦。

實測輸出波形

輸出兩路獨立的方波、正弦波、三角波。

視頻演示

發(fā)布評論請先 登錄

相關(guān)推薦

labview控制示波器與信號發(fā)生器

信號發(fā)生器頻率怎么調(diào)

信號發(fā)生器的sync什么意思

信號發(fā)生器的使用方法 信號發(fā)生器的幅值是有效值嗎

射頻信號發(fā)生器的使用說明、功能設(shè)置和操作方法

射頻信號發(fā)生器的使用方法

射頻信號發(fā)生器的工作原理和應(yīng)用

函數(shù)發(fā)生器、信號發(fā)生器和波形發(fā)生器的區(qū)別

低頻信號發(fā)生器如何調(diào)節(jié)電壓?

TH1312系列音頻掃頻信號發(fā)生器操作說明

基于FPGA 的DDS正弦信號發(fā)生器的設(shè)計和實現(xiàn)

4分鐘選型|怎么快速選擇適合自己的信號發(fā)生器?#信號源 #射頻信號源 #信號發(fā)生器 #調(diào)制信號 #電路知識

信號發(fā)生器是干什么用的 信號發(fā)生器和示波器怎么連接

適用于射頻信號發(fā)生器的雙通道16位500MSPS DAC SC3363

我的畢業(yè)設(shè)計——基于FPGA的雙路低頻信號發(fā)生器

我的畢業(yè)設(shè)計——基于FPGA的雙路低頻信號發(fā)生器

評論