testbench就是對寫的FPGA文件進行測試的文件,可以是verilog也可以是VHDL。verilog和VHDL的國際標準里面有很多不能被綜合實現的語句,比如initial,forever,repeat,延時語句#1等等,這些語句就是用來測試的時候使用的。運行環境一般是ise或者vivado或者quartus自帶的仿真工具,或者如modelsim一樣的第三方仿真工具。

測試機制

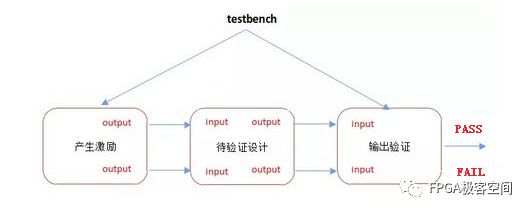

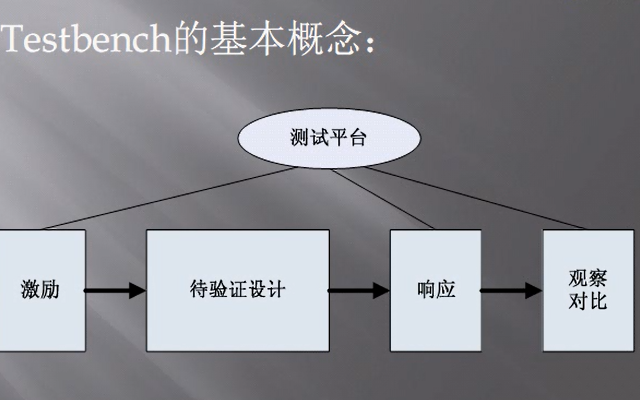

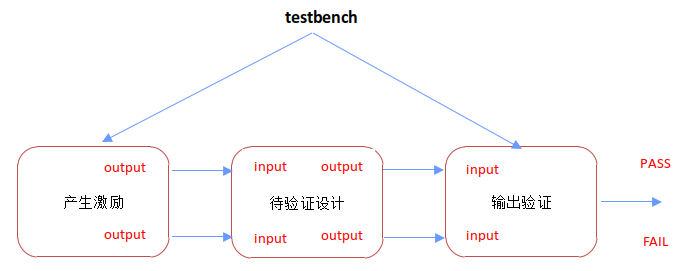

任何一個設計好的模塊,都有輸入和輸出,此模塊是否滿足要求就是看給定滿足要求的輸入,是否能夠得到滿足要求的輸出。所以testbench的測試機制就是:用各種verilog或者VHDL語法,產生滿足條件的激勵信號(也就是對被模塊的輸入),同時對模塊的輸出進行捕捉,測試輸出是否滿足要求。如下圖,產生激勵輸出驗證模塊兩個模塊都屬于testbench,最好的輸出驗證模塊最終只需要給一個pass和fail的答案出來就可以了。不管是用一個信號表示pass和fail還是用$display()函數打印,最終簡單明了的給出過或者不過的信息就好了。請大家寫仿真文件的時候盡量做到這點。

運行順序

跟大家解釋一點,所有testbench本質上都是串行執行,因為在CPU環境下,沒有可靠并行執行的能力。所有并行的語句,比如兩個always模塊,fork join語句塊,都是軟件模擬并行執行的。所以老一點的編譯器,信號定義要在initial語句前面,initial的信號要先有初始值后面的語句才能從給定初值開始執行。所以大家寫testbench的時候,要注意,最好先定義信號,再寫initial語句,后面的語句交換順序不影響,軟件可以識別并按照IEEE標準的順序去執行。

如果一個模塊里面想用并行執行語句用fork join語句,順序執行用begin end語句。initial語句可以寫多個,都是并行執行的,當兩個信號在initial沖突的時候,會先執行前面的initial的值。

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603427 -

Verilog

+關注

關注

28文章

1351瀏覽量

110102

原文標題:FPGA中的testbench

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LFSR testbench V1.2

testbench怎么寫_testbench經典教程VHDL

簡單的Testbench設計

FPGA視頻教程:簡單的Testbench設計

關于testbench在FPGA編程中的技巧

介紹FPGA中testbench的編寫技巧

在模塊化設計過程中編寫testbench并仿真的方法

FPGA驗證簡介之FPGA開發分析一個testbench

Verilog Testbench怎么寫 Verilog Testbench文件的編寫要點

編寫高效Testbench的指南和示例

FPGA中的testbench介紹

FPGA中的testbench介紹

評論