近期,全球第一大代工廠臺積電官方發布公告宣布了兩項重要進展:其一,7nm EUV工藝流片首次成功;其二,將在明年4月份進行5nm工藝試產。5nm芯片預計將在2020年第二季度量產,屆時將滿足蘋果等各家旗艦手機新平臺。

近日,臺積電發布了兩項關于其在極紫外光刻(EUVL)方面取得重要進展的公告。

首先,這家全球一號代工廠已經成功使用其第二代7nm工藝技術完成了首個客戶芯片的流片工作,該技術采用了有限的EUVL技術;其次,臺積電透露計劃于2019年4月開始試產5nm工藝技術。

臺積電推出首款7nmEUV芯片

臺積電于今年4月開始采用第一代7nm制造工藝(CLN7FF/N7)大批量生產芯片。N7仍在采用ArF準分子激光的深紫外(DUV)光刻技術。

相比之下,臺積電的第二代7NM制造技術(CLN7FF +/N7 +)將對四個非關鍵層使用極紫外光刻(EUVL),主要是為了加速生產并學習如何熟練掌握ASML的新光刻機Twinscan NXE。

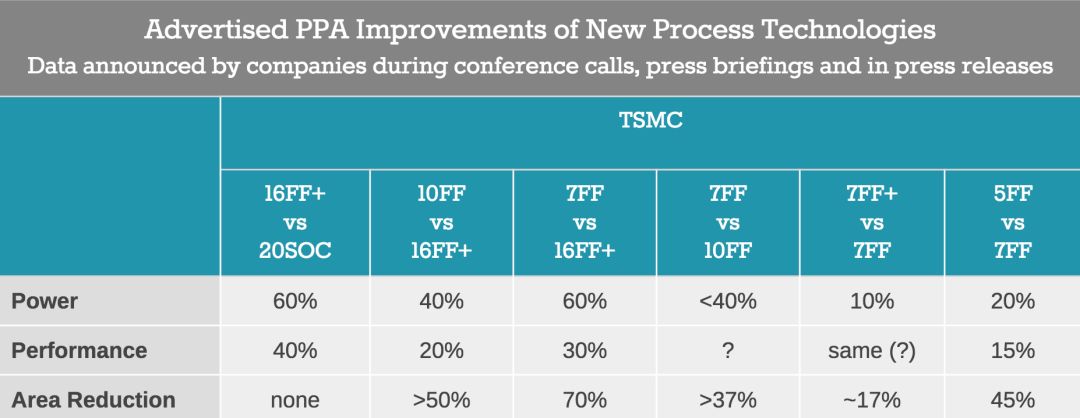

有關從N7到N7 +的改進信息相當有限,臺積電只表示:新技術將提供高出20%的晶體管密度(因為金屬間距更緊),并且在同等頻率下功耗可降低6-12%(更準確講約為8%)。

雖然N7 +優于其前代產品的優勢并不顯著(例如,臺積電從未提及預期新技術帶來多少性能提升),但幾乎可以肯定的是,移動SoC的開發人員仍會全心全意地接受它們,他們需要每年都發布新的芯片。也就是說,臺積電已使用N7+技術淘汰了第一款芯片也就不足為奇了。此外,該公司正在為汽車行業準備一個專門的流程版本。

臺積電并未透露這次流片成功的芯片出自哪家客戶,但考慮到近年來這家代工廠和各家的合作關系,答案也是顯而易見的。

5nm芯片,下一站等你

臺積電預計接下來將推出第一代5nm(CLN5FF,N5)工藝,將最多在14個層上應用EUV。這將實現密度方面的切實改善,但需要臺積電廣泛使用EUV設備。與臺初代7nm相比,5nm工藝將使芯片面積縮小約45%(即5nm芯片的晶體管密度比7nm芯片高出約1.8倍),同功耗頻率提升15%,同頻功耗降低20%(在頻率和復雜度相同的情況下)。

明年4月,臺積電將準備開始5nm EUV工藝芯片進行風險性市場。請記住,通常代工廠及其客戶從風險性試產到量產大約需要一年的時間。臺積電現在可能打算在2020年Q2大規模生產5納米芯片,以及時滿足屆時各家旗艦智能手機新平臺。

臺積電5nm的工藝的EDA設計工具將在今年11月提供,因此芯片設計現在可能就正在進行中。

雖然5nm工藝的許多基礎IP模塊現已準備就緒,但仍缺失一些重要部分,例如PCIe Gen 4和USB 3.1 PHY,它們可能要到明年6月才能就緒。對于臺積電的一些客戶而言,缺少這些產品并不是問題,但卻也不得不等待。

阻止小型公司開發FinFET芯片的一大重要因素是開發成本。制定SoC的平均成本(人工成本和知識產權許可證)約為1.5億美元。根據EETAsia的數據,5nm時代將增加到2億至2.5億美元,這將不少本抱有興趣的工廠拒之門外。

-

芯片

+關注

關注

456文章

51121瀏覽量

426089 -

臺積電

+關注

關注

44文章

5676瀏覽量

166836

原文標題:臺積電7納米極紫外光EUV芯片首次流片成功,5納米明年試產!

文章出處:【微信號:AI_era,微信公眾號:新智元】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電推出首款7nmEUV芯片,5nm芯片下一站等你

臺積電推出首款7nmEUV芯片,5nm芯片下一站等你

評論