大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來聊一聊使用matlab和ISE 創(chuàng)建并仿真ROM IP核。本人想使用簡單的中值濾波進(jìn)行verilog相關(guān)算法的硬件實(shí)現(xiàn),由于HDL設(shè)計(jì)軟件不能直接處理圖像,大部分過程都是可以將圖像按照一定的順序保存到TXT文檔中,經(jīng)過Modelsim仿真后,處理的數(shù)據(jù)再經(jīng)過matlab顯示圖像;圖像首先通過matlab或者C語言保存在TXT文檔中,生成測試向量文件,然后在仿真軟件中進(jìn)行仿真處理,把處理后的數(shù)據(jù)保存為TXT格式,最后用matlab顯示,觀察結(jié)果。一般都是先創(chuàng)建MIF文件,將圖像中的像素信息用一個(gè)ROM儲(chǔ)存起來,然后調(diào)用ROM里面的地址進(jìn)行處理,相當(dāng)于制作了一個(gè)ROM查找表。

用Quartus II創(chuàng)建并仿真ROM的步驟:

1.在Quatus工程下生成一個(gè)ROM

2.編寫.mif文件,作為ROM的初始化文件

3.將.mif文件拷貝到Modelsim工程下

4.進(jìn)行Modelsim仿真

圖像保存的步驟:

1.使用matlab將圖像生成txt文。

2.創(chuàng)建mif文件(Memory Initialization File):使用mif生成器、C語言或者matlab語言來生成;選擇直接使用matlab生成mif文件gray_image.mif;

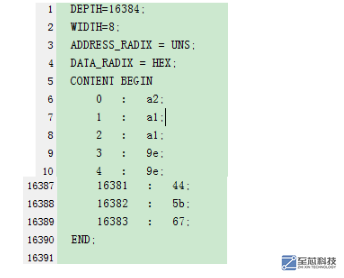

生成的mif文件如下圖所示:

3.調(diào)用mif文件生成ROM(verilog文件即.v文件)

使用Xilinx創(chuàng)建并仿真ROM的步驟:

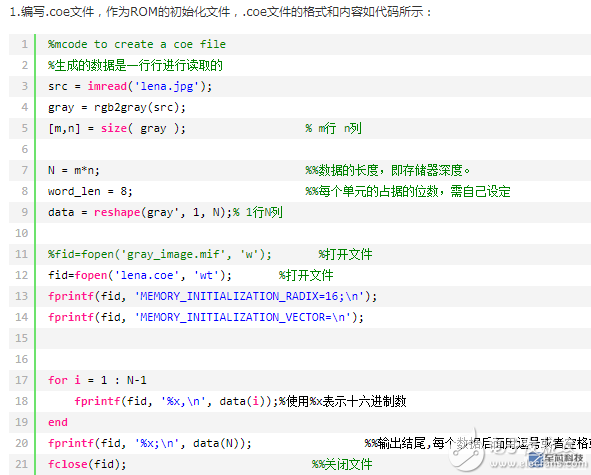

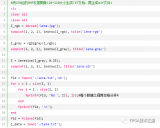

1.編寫.coe文件,作為ROM的初始化文件,.coe文件的格式和內(nèi)容如代碼所示:

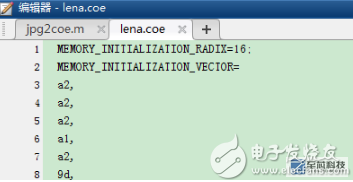

2.生成的.coe文件格式如下圖所示:

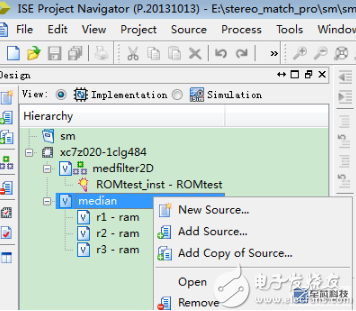

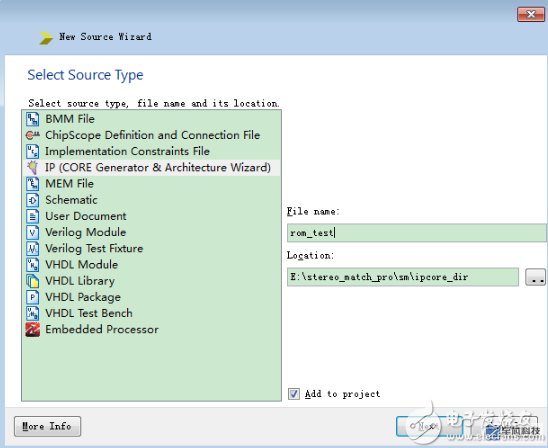

3.使用Xilinx中的Core Generator完成ROM的例化(生成的.coe文件的圖像數(shù)據(jù)是一行行進(jìn)行讀取的)。打開ISE,右鍵單擊New Source,如下圖所示:

單擊之后選擇IP_Core_Generator,

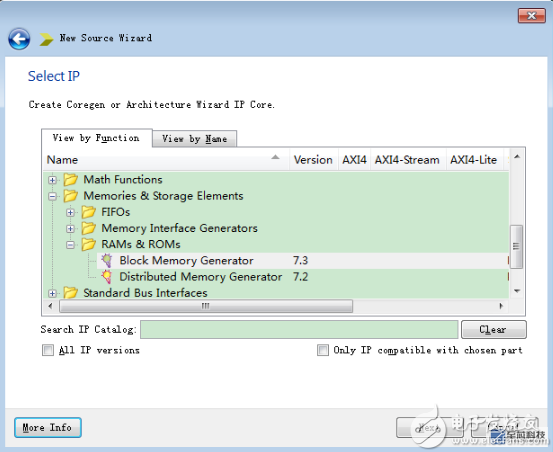

單擊Next選項(xiàng),選擇Memories&Storage Elements->RAMs&ROMs->,選擇塊式存儲(chǔ)或者分布式存儲(chǔ)(這里根據(jù)存儲(chǔ)數(shù)據(jù)的大小進(jìn)行選擇,較小的可以選擇塊式存儲(chǔ))。

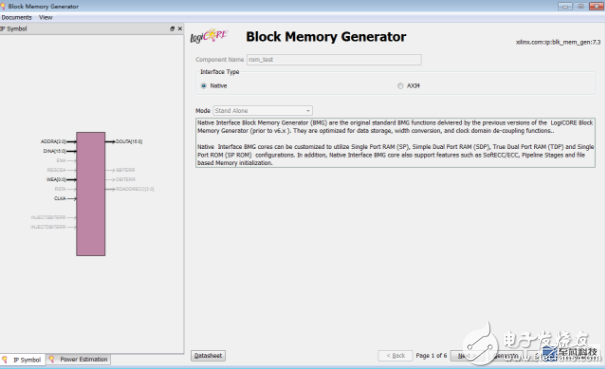

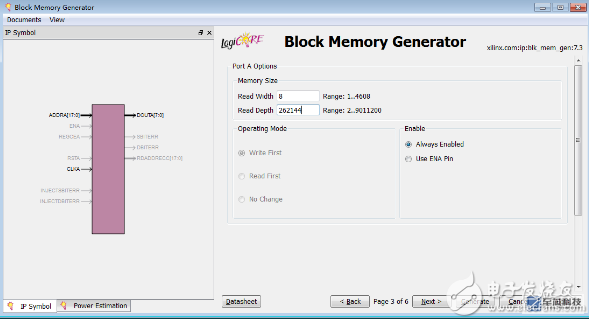

點(diǎn)擊Next,然后Finish。然后就出現(xiàn)了下面的界面,一直點(diǎn)擊Next進(jìn)行ROM屬性的一些設(shè)置,直至完成:

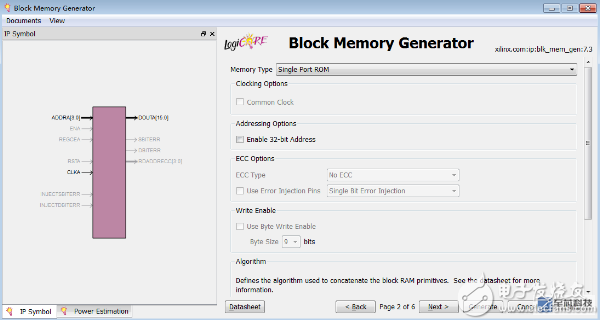

然后就要選擇所需要的ROM的大小:

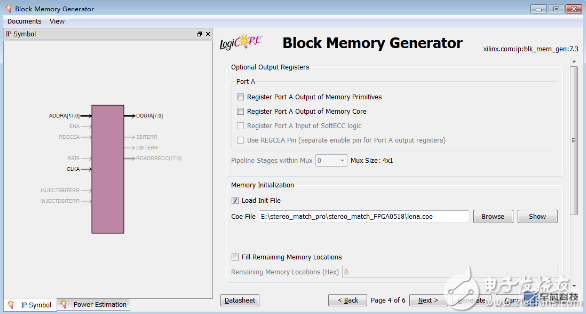

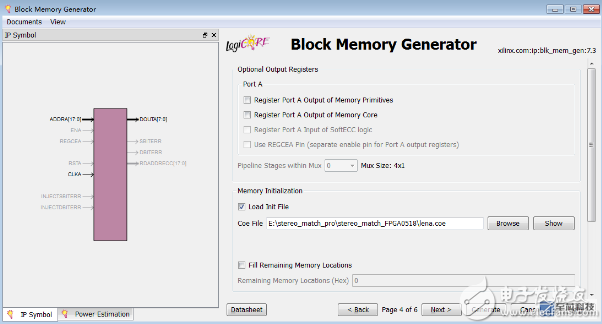

portA 表示輸出要不要時(shí)鐘打拍輸出,這個(gè)是在mux里實(shí)現(xiàn)的; 在添加初始化文件的時(shí)候,將之前matlab生成的.coe文件添加到ROM IP核中去。

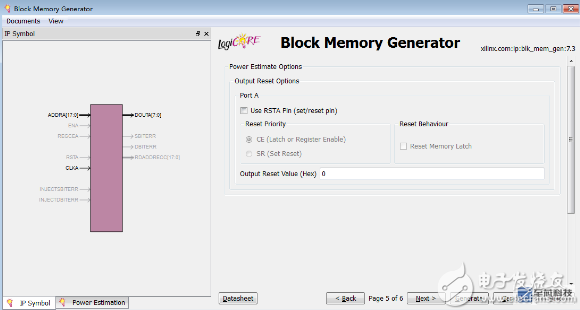

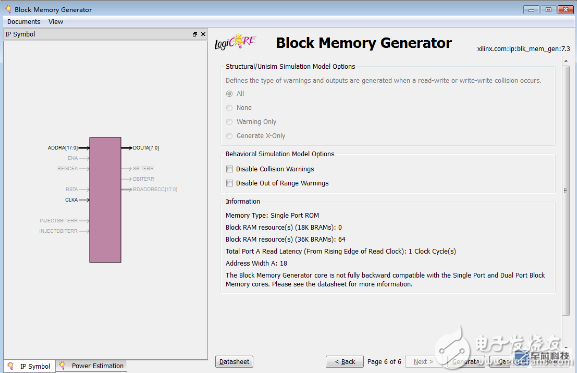

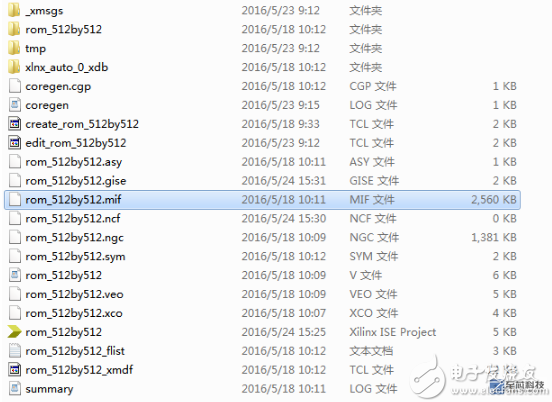

一直next下去,就可以得到初始化好的ROM IP核,可以在./ipcore_dir目錄下查看ROM文件,從而可以在頂層模塊中對ROM進(jìn)行例化。

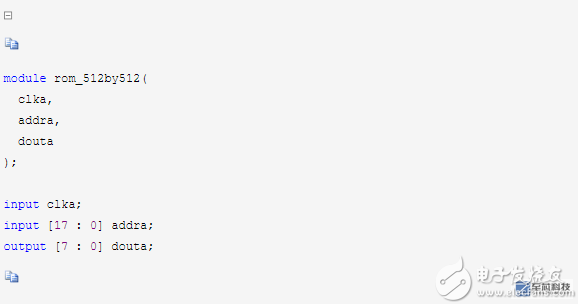

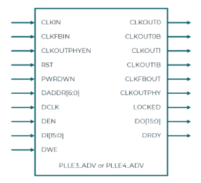

生成的ROM文件的輸入輸出變量如下:

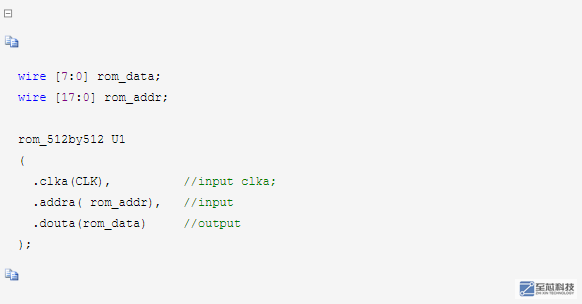

在頂層模塊中對ROM進(jìn)行例化如下:

4.使用CoreGenerator完成ROM的例化后會(huì)生成一個(gè).mif文件,這是Modelsim進(jìn)行ROM仿真時(shí)需要的初始化文件,將.mif文件復(fù)制到Modelsim工程下進(jìn)行仿真。

5.查看ROM模塊中的初始化數(shù)據(jù),雙擊Rom模塊,出現(xiàn)如下圖的界面,點(diǎn)擊show按鈕,即可查看數(shù)據(jù);

完

各位,加油!

-

FPGA

+關(guān)注

關(guān)注

1630文章

21777瀏覽量

604679

發(fā)布評論請先 登錄

相關(guān)推薦

使用IP核和開源庫減少FPGA設(shè)計(jì)周期

ALINX發(fā)布100G以太網(wǎng)UDP/IP協(xié)議棧IP核

芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線,覆蓋 TCP/UDP/NVMe AXI IP 核

將ASIC IP核移植到FPGA上——更新概念并推動(dòng)改變以完成充滿挑戰(zhàn)的任務(wù)!

如何使用MATLAB創(chuàng)建預(yù)測模型

如何在ModelSim中添加Xilinx仿真庫

FPGA | Xilinx ISE14.7 LVDS應(yīng)用

FPGA的IP軟核使用技巧

關(guān)于FPGA IP核

利用ISE與Matlab創(chuàng)建并仿真FPGA設(shè)計(jì)中的ROM IP核

FPGA學(xué)習(xí):使用matlab和ISE 創(chuàng)建并仿真ROM IP核

FPGA學(xué)習(xí):使用matlab和ISE 創(chuàng)建并仿真ROM IP核

評論