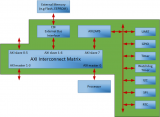

Virtex?-7 2000T擁有 68 億個晶體管, 200 萬個邏輯單元,相當于 2,000 萬個 ASIC 門。這也是首款采用賽靈思獨特的堆疊硅片互聯(SSI)技術的FPGA。Virtex-7 2000T將使其無需借助并行或者串行I/O, 或者通過片外的 PCB連線與相鄰的 FPGA 互聯, 即可充分享受到FPGA芯片內高帶寬、低時延、低功耗互聯機制的優勢。

了解如何將復雜的SoC平臺映射到單個Virtex?-7 2000T FPGA

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21781瀏覽量

604912 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131410 -

soc

+關注

關注

38文章

4193瀏覽量

218692

發布評論請先 登錄

相關推薦

如何設置內網IP的端口映射到公網

在現代網絡環境中,端口映射(Port Mapping)是一項非常實用的技術,它允許用戶將內網設備的服務端口映射到公網,使外網用戶可以訪問內網中的服務。這項技術在遠程辦公、設備遠程控制、游戲

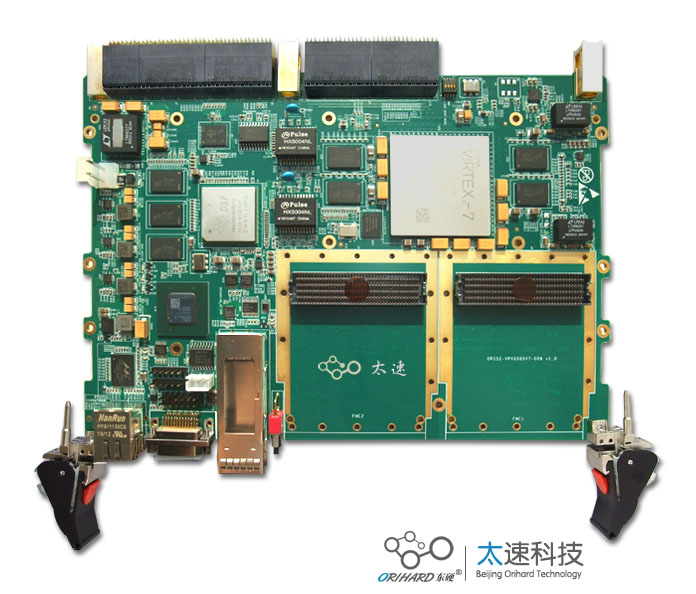

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡

本板卡基于標準6U VPX 架構,為通用高性能信號處理平臺,系我公司自主研發。板卡采用一片TI DSP TMS320C6678和一片Xilinx公司Virtex 7系列的FPGA

如何將自定義邏輯從FPGA/CPLD遷移到C2000?微控制器

電子發燒友網站提供《如何將自定義邏輯從FPGA/CPLD遷移到C2000?微控制器.pdf》資料免費下載

發表于 09-23 12:36

?0次下載

兼容7A100T和PG2L100H雙芯核心板,米爾FPGA平臺

不同需求

MYIR推出FPGA 開發平臺具有極高的靈活性,用戶可以根據項目需求自由選擇AMD XC7A100T 和紫光同創 PG2L100H 這兩款核心板,共享同一底板平臺,可以實現無

發表于 09-14 16:08

在單個C2000?MCU上使用FCL和SFRA進行雙軸電機控制

電子發燒友網站提供《在單個C2000?MCU上使用FCL和SFRA進行雙軸電機控制.pdf》資料免費下載

發表于 09-14 09:40

?0次下載

FPGA核心板 Xilinx Artix-7系列XC7A100T開發平臺,米爾FPGA工業開發板

MYC-J7A100T核心板及開發板Xilinx Artix-7系列XC7A100T開發平臺,FPGA工業芯XC

發表于 05-31 15:12

?9次下載

能否建議通過內存映射提高aur性能?

我們使用英飛凌 Aurix TC364 作為平臺。 我們試圖通過將 ISR 映射到不同的內存單元來提高 ISR 函數的性能,具體方法是使用 #pragma section code

發表于 05-29 07:39

STM8S105的TIM1_CH4重映射到了PD7之后,為什么PC4仍然有PWM輸出呢?

STM8S105的TIM1_CH4重映射到了PD7之后,為什么PC4仍然有PWM輸出

發表于 04-29 06:16

中高端FPGA如何選擇

為了使數據傳輸更加高效,Achronix FPGA上的Memory資源也是非常給力,不管是片上Ram還是DDR接口,都比Virtex Ultrascale+有很大優勢。

發表于 04-24 15:09

TC33X將dCache映射到RAM會導致存儲總線錯誤是為什么?如何解決?

我嘗試通過以下(簡化的)順序使用 TC33X 將數據緩存映射到 RAM 區域:

CPU_DCON0 = 2

MTU_CLC = 0 MTU_MEMMAP |= 1

在軟件閃爍且調試器保持連接

發表于 01-25 06:23

如何將共享代碼映射到DSPR5以及將其映射到其他RAM區域?

Scratch-Pad Sram(CPU5 DSPR)相關聯。 在鏈接器腳本中,我已經映射了每個.text 部分移至其各自的 PSPR 內核。 我想知道如何將共享代碼映射到 DSPR5 以及

發表于 01-24 07:26

如何將復雜的SoC平臺映射到單個Virtex-7 2000T FPGA上

如何將復雜的SoC平臺映射到單個Virtex-7 2000T FPGA上

評論