電磁兼容的一般概念

考慮電磁兼容的根本原因在于電磁干擾的存在。電磁干擾(Electromagnetic Interference,簡稱EMI)是破壞性電磁能從一個電子設備通過輻射或傳導傳到另一個電子設備的過程。一般來說,EMI特指射頻信號(RF),但電磁干擾可以在所有的頻率范圍內(nèi)發(fā)生。

電磁兼容性(Electromagnetic Compatibility,簡稱EMC)是指電氣和電子系統(tǒng)、設備和裝置在設定的電磁環(huán)境中,在規(guī)定的安全界限內(nèi)以設計的等級或性能運行,而不會由于電磁干擾引起損壞或不可接受到性能惡化的能力。這里所說的電磁環(huán)境是指存在于給定場所的所有電磁現(xiàn)象的總和。這表明電磁兼容性一方面指電子產(chǎn)品應具有抑制外部電磁干擾的能力;另一方面,該電子產(chǎn)品所產(chǎn)生的電磁干擾應低于限度,不得影響同一電磁環(huán)境中其他電子設備的正常工作。

現(xiàn)今的電子產(chǎn)品已經(jīng)由模擬設計轉為數(shù)字設計。隨著數(shù)字邏輯設備的發(fā)展,與EMI和EMC相關的問題開始成為產(chǎn)品的焦點,并得到設計者和使用者很大的關注。美國通信委員會(FCC)在20世紀70年代中后期公布了個人電腦和類似設備的輻射標準,歐共體在其89/336/EEC電磁兼容指導性文件中提出輻射和抗干擾的強制性要求。我國也陸續(xù)制定了有關電磁兼容的國家標準和國家軍用標準,例如“電磁兼容術語”(GB/T4365-1995),“電磁干擾和電磁兼容性術語”(GJB72-85),“無線電干擾和抗擾度測量設備規(guī)范”(GB/T6113-1995),“電動工具、家用電器和類似器具無線電干擾特性的測量方法和允許值”(GB4343-84)。這些電磁兼容性規(guī)范大大推動了電子設計技術并提高了電子產(chǎn)品的可靠性和適用性。

EMC在PCB設計中的重要性

隨著電子設備的靈敏度越來越高,并且接受微弱信號的能力越來越強,電子產(chǎn)品頻帶也越來越寬,尺寸越來越小,并且要求電子設備抗干擾能力越來越強。一些電器、電子設備工作時所產(chǎn)生的電磁波,容易對周圍的其他電氣、電子設備形成電磁干擾,引發(fā)故障或者影響信號的傳輸。另外,過度的電磁干擾會形成電磁污染,危害人們的身體健康,破壞生態(tài)環(huán)境。

如果在一個系統(tǒng)中各種用電設備能夠正常工作而不致相互發(fā)生電磁干擾造成性能改變和設備的損壞,人們就稱這個系統(tǒng)中的用電設備是相互兼容的。但是隨著設備功能的多樣化、結構的復雜化、功率的加大和頻率的提高,同時它們的靈敏度也越來越高,這種相互兼容的狀態(tài)越來越難獲得。為了使系統(tǒng)達到電磁兼容,必須以系統(tǒng)的電磁環(huán)境為依據(jù),要求每個用電設備不產(chǎn)生超過一定限度的電磁發(fā)射,同時又要求它本身要具備一定的抗干擾能力。只有對每一個設備都作出這兩個方面的約束和改進,才能保證系統(tǒng)達到完全兼容。

通常認為電磁干擾的傳輸有兩種方式:一種是傳導方式;另一種是輻射方式。在實際工程中,兩個設備之間發(fā)生干擾通常包含著許多種途徑的耦合。正因為多種途徑的耦合同時存在,反復交叉,共同產(chǎn)生干擾,才使得電磁干擾變得難以控制。

常見的電磁干擾主要有以下幾種:

(1)射頻干擾。由于現(xiàn)有的無線電發(fā)射機的激增,射頻干擾給電子系統(tǒng)造成了很大的威脅。蜂窩電話、手持無線電、無線電遙控單元、尋呼機和其他類似設備現(xiàn)在非常普遍。造成有害的干擾并不需要很大的發(fā)生功率。典型的故障出現(xiàn)在射頻場強為1~10V/m的范圍內(nèi)。在歐洲、北美和很多亞洲國家,避免射頻干擾損壞其他設備已經(jīng)成為對所有產(chǎn)品在法律上的強制性規(guī)定。

(2)靜電放電(ESD)。現(xiàn)代芯片工藝已經(jīng)有了很大的進步,在很小的幾何尺寸(0.18um)上元件已經(jīng)變得非常密集。這些高速的、數(shù)以百萬計的晶體管微處理器的靈敏性很高,很容易受到外界靜電放電影響而損壞。放電可以是直接或輻射的方式引起。直接接觸放電一般引起設備永久性的損壞。輻射引起的靜電放電可能引起設備紊亂,工作不正常。

(3)電力干擾。隨著越來越多的電子設備接入電力主干網(wǎng),系統(tǒng)會出現(xiàn)一些潛在地干擾。這些干擾包括電力線干擾、電快速瞬變、電涌、電壓變化、閃電瞬變和電力線諧波等。對于高頻開關電源來說,這些干擾變得很顯著。

(4)自兼容性。一個系統(tǒng)的數(shù)字部分或電路可能干擾模擬設備,在導線之間產(chǎn)生串繞(Crosstalk),或者一個電機可以引起數(shù)字電路的紊亂。

另外,一個在低頻可以正常工作的電子產(chǎn)品,當頻率升高時會遇到一些低頻所沒有的問題。比如反射、串繞、地彈、高頻噪聲等。

一個不符合EMC規(guī)范的電子產(chǎn)品不是合格的電子設計。設計產(chǎn)品除了滿足市場功能性要求外,還必須采用適當?shù)脑O計技術來預防或解除EMI的影響。

PCB設計的EMC考慮

對于高速PCB(Printed Circuit Board,印制電路板)設計中EMI問題,通常有兩種方法解決:一種是抑制EMI的影響,另一種是屏蔽EMI的影響。這兩種方式有很多不同的表現(xiàn)形式,特別是屏蔽系統(tǒng)使得EMI影響電子產(chǎn)品的可能性降到了最低。

射頻(RF)能量是由印制電路板(PCB)內(nèi)的開關電流產(chǎn)生的,這些電流是數(shù)字元件產(chǎn)生的副產(chǎn)品。在一個電源分配系統(tǒng)中每一個邏輯狀態(tài)的改變都會產(chǎn)生一個瞬間的電涌,大多數(shù)情況下,這些邏輯狀態(tài)的改變不會產(chǎn)生足夠的接地噪聲電壓造成任何功能性的影響,但當一個元件的邊沿速率(上升時間和下降時間)變得相當快的時候便會產(chǎn)生足夠的射頻能量影響其他的電子元件的正常工作。

一、 PCB上電磁干擾產(chǎn)生的原因

不適當?shù)淖龇ㄍǔ赑CB上引起超出規(guī)范的EMI。結合高頻信號的特性,與PCB級的EMI相關的主要包括以下幾個方面:(1)封裝措施使用不適當。如應該用金屬封裝的器件卻用塑料封裝。

(2)PCB設計不佳,完成質(zhì)量不高,電纜與接頭的接地不良。

(3)不適當甚至錯誤的PCB布局。

包括時鐘和周期信號走線設定不當;PCB的分層排列及信號布線層設置不當;對于帶有高頻RF能量分布成分的選擇不當;共模與差模濾波考慮不足;接地環(huán)路引起RF和地彈;旁路和去耦不足等等。

要實現(xiàn)系統(tǒng)級的EMI抑制,通常需要一些適當?shù)姆椒ǎ哼@主要包括屏蔽、襯墊、接地、濾波、去耦、適當布線、電路阻抗控制等。

二、電磁兼容的屏蔽設計

現(xiàn)今的電子產(chǎn)業(yè)界已愈來愈注意到SE/EMC(Shielding Effectiveness,SE,隔離室屏蔽效益)的需求,而隨著更多電子組件的使用,電磁兼容性亦更受到關切。電磁屏蔽就是以金屬隔離的原理來控制電磁干擾由一個區(qū)域向另一個區(qū)域感應和輻射傳播電方法。通常包括兩種:一種是靜電屏蔽,主要用于防止靜電場和恒定磁場的影響;另一種是電磁屏蔽,主要用于防止交變電場、交變磁場以及交變電磁場的影響。

EMI屏蔽可使產(chǎn)品簡單且有效的符合EMC的規(guī)范,當頻率在10MHz以下時電磁波大多為傳導的形式,而較高頻率的電磁波則多為輻射的形式。設計時可以采用單層實心屏蔽材料、多層實心屏蔽材料、雙重屏蔽或者雙重以上屏蔽等新型材料進行EMI屏蔽。對于低頻的電磁干擾需要用厚的屏蔽層,最合適的是使用磁導率高的材料或磁性材料,如鎳銅合金等,以獲得最大的電磁吸收損耗,而對于高頻電磁波可使用金屬屏蔽材料。

在實際的EMI屏蔽中,電磁屏蔽效能很大程度上取決于機箱的物理結構,即導電的連續(xù)性。機箱上的接縫以及開口都是電磁波的泄漏源。而且,穿過機箱的電纜也是造成屏蔽效能下降到主要原因。機箱上開口的電磁泄漏與開口的形狀、輻射源的特性和輻射源到開口處的距離相關。通過適當?shù)卦O計開口尺寸和輻射源到開口的距離能夠改善屏蔽效能。通常解決機箱縫隙電磁泄漏的方式是在縫隙處用電磁密封襯墊。電磁密封襯墊是一種導電的彈性材料,它能夠保持縫隙處的導電連續(xù)性。常見的電磁密封襯墊有:導電橡膠(在橡膠中摻入導電顆粒,使這種復合材料既具有橡膠的彈性,又具有金屬的導電性。)、雙重導電橡膠(它不是在橡膠所有部分摻入導電顆粒,這樣獲得的好處是既最大限度地保持了橡膠的彈性,又保證了導電性)、金屬編織網(wǎng)套(以橡膠為芯的金屬編織網(wǎng)套)、螺旋管襯墊(用不銹鋼、鈹銅或鍍錫鈹銅卷成的螺旋管)等。另外,當對通風量要求比較高時,必須使用截至波導通風板,這種板相當于一個高通濾波器,對高于某一頻率的電磁波不衰減通過,但對于低于這一頻率的電磁波則進行很大的衰減,合理應用截至波導的這種特性可以很好的屏蔽EMI的干擾。

三、 電磁兼容的合理PCB設計

隨著系統(tǒng)設計復雜性和集成度的大規(guī)模提高,電子系統(tǒng)設計師們正在從事100MHZ以上的電路設計,總線的工作頻率也已經(jīng)達到或者超過50MHZ,有的甚至超過100MHZ。當系統(tǒng)工作在50MHz時,將產(chǎn)生傳輸線效應和信號的完整性問題;而當系統(tǒng)時鐘達到120MHz時,除非使用高速電路設計知識,否則基于傳統(tǒng)方法設計的PCB將無法工作。因此,高速電路設計技術已經(jīng)成為電子系統(tǒng)設計師必須采取的設計手段。只有通過使用高速電路設計師的設計技術,才能實現(xiàn)設計過程的可控性。

通常認為如果數(shù)字邏輯電路的頻率達到或者超過45MHZ~50MHZ,而且工作在這個頻率之上的電路已經(jīng)占到了整個電子系統(tǒng)一定的份量(比如說1/3),就稱為高速電路。實際上,信號邊沿的諧波頻率比信號本身的頻率高,是信號快速變化的上升沿與下降沿(或稱信號的跳變)引發(fā)了信號傳輸?shù)姆穷A期結果。要實現(xiàn)符合EMC標準的高頻PCB設計,通常需要采用以下技術:包括旁路與去耦、接地控制、傳輸線控制、走線終端匹配等。

(1)旁路與去耦

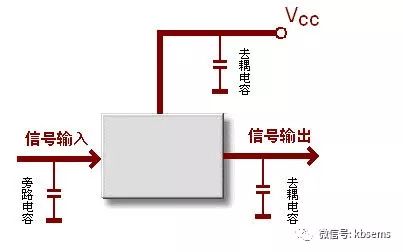

去耦是指去除在器件切換時從高頻器件進入到配電網(wǎng)絡中的RF能量,而旁路則是從元件或電纜中轉移不想要的共模RF能量。

所有的電容器都是由LCR電路組成,其中L是電感,它與導線長度有關,R是導線中的電阻,C是指電容。在某一頻率上,該LC串聯(lián)組合將產(chǎn)生諧振。在諧振狀態(tài)下,LCR電路將有非常小的阻抗和有效的RF旁路。當頻率高于電容的自諧振時,電容器漸變?yōu)楦行宰杩梗瑫r旁路或去藕效果下降。因此,電容器實現(xiàn)旁路與去耦的效果受引線長度,以及電容器與器件間的走線、介質(zhì)填料等的影響。理想的去耦電容器還可以提供邏輯裝置狀態(tài)切換時所需的所有電流,實際上是電源和接地層間的阻抗決定電容器能夠提供的電流的多少。

當選擇旁路和去耦電容時,可通過邏輯系列和所使用的時鐘速度來計算所需電容器的自諧振頻率,根據(jù)頻率以及電路中的容抗來選擇電容值。在選擇封裝尺度是盡量選擇更低引線電感的電容,這通常表現(xiàn)為SMT(Surface Mount Technology)電容器,而不選擇通孔式電容器(如DIP封裝的電容器)。另外在產(chǎn)品設計中,也常常采用并聯(lián)去耦電容來提供更大的工作頻帶,減少接地不平衡。在并聯(lián)電容系統(tǒng)中,當高于自諧振頻率時,大電容表現(xiàn)感性阻抗并隨頻率增大而增加;而小電容則表現(xiàn)為容性阻抗并隨頻率增加而減少,而且此時整個電容電路的阻抗比單獨一個電容時的阻抗要小。

(2)接地系統(tǒng)

大多數(shù)電子產(chǎn)品都要求接地。接地是使噪聲干擾最小化并對電路進行劃分的一個重要方法。接地主要表現(xiàn)在為模擬與數(shù)字電路之間提供參考連接以及在PCB的地層和金屬外殼之間提供高頻連接。

PCB經(jīng)常包含著危險電壓。它包括在電源組件、通信電路、延遲驅(qū)動儀表控制、功率交換模塊以及類似的器件中。要使產(chǎn)品符合安全規(guī)則,并符合電磁兼容性,必須去掉這些危險電壓,通常的策略就是采用地線或地平面系統(tǒng)。地線(或地平面)實質(zhì)是信號回流源的低阻抗路徑。由于地線的這種作用,使得地線中可能會有很大的電流存在。因為地線的阻抗不會是零,因而這種電流會產(chǎn)生電位差。當?shù)鼐€中有電位差存在時,對系統(tǒng)的影響就很明顯了:地電位差能夠造成電路的誤動作,使系統(tǒng)工作不正常。

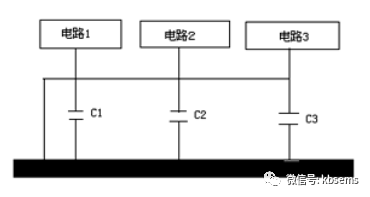

由于接地系統(tǒng)存在地電位差的問題,在設計產(chǎn)品的接地過程中必須針對PCB的特點選擇相應的接地方法,而不能隨意使用。通常采用的接地方法包括單點接地、多點接地、混合接地等。單點接地是指在產(chǎn)品設計中,接地線路與單獨一個參考點相連,這種接地設置目的是為了防止來自兩個不同的參考電平的子系統(tǒng)中的電流與射頻電流經(jīng)過同樣的返回路徑而導致共阻抗耦合。這種接地方法用在低頻PCB中比較合適,可以減小分布傳輸阻抗的影響。但在高頻PCB中,返回路徑的電感在高頻下成為線路阻抗的主要部分,因而在高頻PCB中為使接地阻抗最小,通常采用多點接地法。多點接地中最重要的一點就是要求接地引線的長度最小,因為更長的引線代表更大的電感,從而增加地阻抗,引起地電位差。混合接地結構是單點接地和多點接地的復合。當在PCB中存在高低混合頻率時常用這種結構,即在低頻處呈現(xiàn)單點接地,而在高頻處則呈現(xiàn)多點接地。如下圖1為容性耦合混合接地。相對應的感性耦合混合接地模型中把C1~C3改為適合的電感即可。

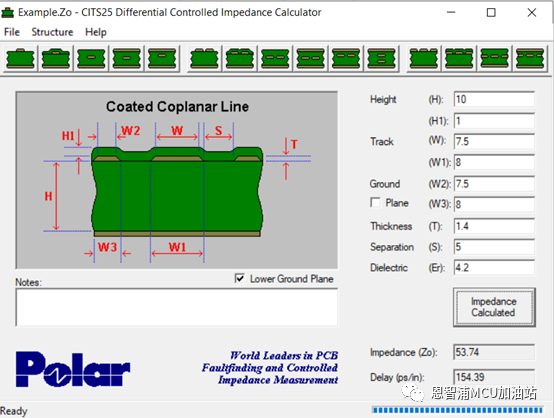

(3)傳輸線效應以及終端匹配

傳輸線就是一個適合在兩個或多個終端間有效傳播電功率或電信號的傳輸系統(tǒng),如金屬導線、波導、同軸電纜和PCB走線。如果傳輸線終端不匹配,或者信號在阻抗不連續(xù)的PCB走線上傳送,電路就會出現(xiàn)功能性問題和EMI干擾,這包括電壓下降、沖擊激勵產(chǎn)生的振蕩等。在處理傳輸線效應過程中,線路阻抗影響著產(chǎn)品的最終性能,當且僅當電路終接的負載等于線路的特性阻抗時,在PCB走線上傳輸?shù)男盘柌艜谧銐蜻h處被完全吸收而不會產(chǎn)生反射現(xiàn)象。若終端不匹配,大部分信號會反射回來,并且容易引起電路的過沖或欠沖甚至電路振蕩。

通常所說的電氣長線是指線路長度大于信號波長的1/20(頻域),或傳播延時大于信號上升沿時間的1/4(時域)的走線。信號線是否為電氣長線決定該電路是集總參數(shù)還是分布參數(shù)結構。對分布參數(shù)電路,為了較好保持信號的波形,必須考慮調(diào)節(jié)傳輸線的特性阻抗和終端匹配問題。傳輸線終端反射電壓可以通過下式表示:

Vr=Vi(Rt-Z0)/ (Rt+Z0)=ρVi

其中Vr是終端電壓,Vi是初始電壓,Rt是終端阻抗,Z0是線路的特性阻抗,ρ為反射率。當Rt=Z0時,反射率為0,即沒有反射,電壓保持不變;當Rt為無窮大,即終端開路,此時反射率為1,電壓100%反射,此時的電壓為原來電壓值得兩倍;如果Rt=0,即終端短路,反射率為-1,則總電壓為零。從中可以看出失配越大,則反射電壓就越大,傳輸線若兩端都不匹配,就會產(chǎn)生電路振蕩。

針對傳輸線效應,通常采用控制走線的長度以及調(diào)節(jié)走線寬度改變特制阻抗來抑制傳輸線效應。例如:則:如果采用CMOS或TTL電路進行設計,工作頻率小于10MHz,布線長度應不大于7.5英寸。工作頻率在50MHz布線長度應不大于2英寸。如果工作頻率達到或超過75MHz布線長度應在1.5英寸。對于GaAs芯片最大的布線長度應為0.3英寸。如果超過這個標準,就存在傳輸線的問題。解決傳輸線效應的另一個方法是選擇正確的布線路徑和終端拓撲結構。走線的拓撲結構是指電路網(wǎng)線的布線順序及布線結構。當使用高速邏輯器件時,除非走線分支長度保持很短,否則邊沿快速變化的信號將被信號主干走線上的分支走線所扭曲。通常情形下,PCB走線采用兩種基本拓撲結構,即菊花鏈(Daisy Chain)布線和星形(Star)分布。當需要不同的阻抗時,最容易的方法就是改變線寬。

四、電磁兼容設計中的電源問題

在PCB設計中,電源系統(tǒng)(包括相對高電位于相對低電位)主要可能引起兩個問題:一個是電源(或高電位)噪聲,即在該數(shù)字電路系統(tǒng)中,CPU電路、動態(tài)存儲器件和其他數(shù)字邏輯電路在工作過程中邏輯狀態(tài)高速變換,造成系統(tǒng)電流和電壓變化而產(chǎn)生的噪聲,溫度變化時的直流噪聲以及供電電源本身產(chǎn)生的噪聲等。另一個是地線(或低電位)噪聲,即在系統(tǒng)內(nèi)各個部分的地線之間出現(xiàn)電位差或因存在接地阻抗而引起接地噪聲。

PCB上的電源電壓波動和地電平波動容易導致信號波形產(chǎn)生尖峰過沖或衰減振蕩,造成數(shù)字IC電路的噪聲容限,進而引起誤操作。其原因主要是數(shù)字IC的開關電流和電源線、地線的電阻所造成的電壓降,以及元器件引腳的分布電感所造成的感應電壓降。分布電感引起的電壓降影響比線路阻抗大,這是設計中必須考慮的一個方面。

當PCB中CMOS部分是數(shù)字模擬混合電路時,如D/A轉換,當數(shù)字部分接電源VDD后,VDD的電能會耦合到模擬部分,部分VDD電壓出現(xiàn)在模擬電源的管腳上,對整個系統(tǒng)性能有很大的破壞,甚至導致系統(tǒng)不能工作。

由于以上的原因,PCB上電源布線應該根據(jù)電流的大小,盡量加大電源線線寬,以期減少環(huán)路阻抗。在多層PCB中采用電源層和地層,同時減少電源線到電源層或地層的線長。另外,電源線和地線的走向應該和數(shù)據(jù)線或地址線傳遞的方向一致,這樣可以減少干擾,增強系統(tǒng)的抗噪聲能力。

展望

隨著電子科技的發(fā)展,系統(tǒng)時鐘和速度不斷提高。現(xiàn)在的計算機系統(tǒng)中時鐘工作頻率經(jīng)常達到上GHz。當元件工作在高頻時,為適應更小的時鐘脈沖間隔,信號跳變沿速率加快,因此RF頻譜分散加重了,產(chǎn)生EMI干擾的可能性增加了,要設計符合EMC的產(chǎn)品難度提高了。但是只要根據(jù)產(chǎn)品的特性以及頻率特性總可以找到相應的設計方案。

一個簡單的電磁干擾模型包括三個因素:必要的能量源、必要的接收器、在接收器和能量源之間必須有能量傳輸?shù)鸟詈下窂健V挥羞@三方面都存在時干擾才可能產(chǎn)生。工程師的任務就是決定系統(tǒng)設計中哪個要素是最容易消除的,并通過相應的PCB設計來實現(xiàn)這種消除EMI的思想 另外,在設計中盡量使用盡可能慢的邏輯系統(tǒng)。比如在大多數(shù)應用中,一個74HCT器件足以作為一個74ACT器件的臨時替代品,同時具有產(chǎn)生更小RF能量的優(yōu)點。一個總的設計思想就是不要使用比功能上所要求的或電路實際要求的更快的元件。

-

pcb

+關注

關注

4319文章

23099瀏覽量

397889 -

電磁兼容

+關注

關注

54文章

1879瀏覽量

97873

原文標題:PCB設計中的電磁兼容性考慮

文章出處:【微信號:ruziniubbs,微信公眾號:PCB行業(yè)工程師技術交流】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

如何在PCB設計中考慮電磁兼容性

如何在PCB設計中考慮電磁兼容性

評論