自己動手做一個信號發(fā)生器和示波器非常重要,不僅可以深刻理解測量儀器的工作原理、關(guān)鍵技術(shù)指標,還可以將書本上學過的模擬電路、數(shù)字邏輯乃至嵌入式系統(tǒng)全部串起來,從系統(tǒng)層面對各個部分的功能以及構(gòu)成有更真切的認識,因此蘇老師覺得這兩個項目應(yīng)該是所有電子工程師都要動手做一遍的基礎(chǔ)入門項目。

高速ADC是數(shù)字示波器的核心部件,今天關(guān)于ADC應(yīng)用的文章就結(jié)合我們摩爾吧/硬禾實戰(zhàn)營的一個實際項目 - 100Msps的數(shù)字示波器的制作來做一個簡單的案例分析,數(shù)字和處理部分將在將來的文章中具體分析,今天集中在模擬部分:

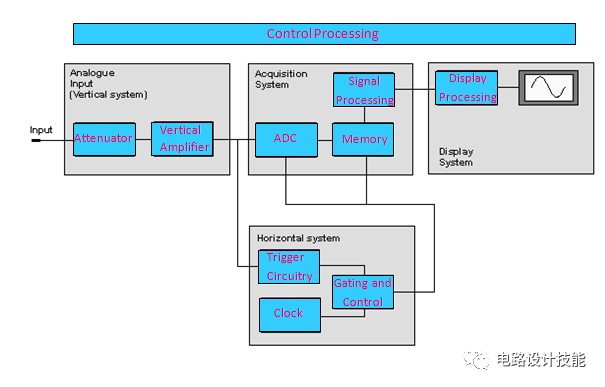

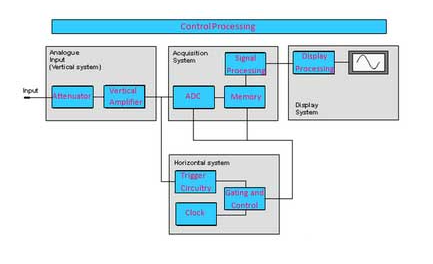

數(shù)字示波器的構(gòu)成框圖

我們的項目對模擬部分的主要指標要求如下:

單通道、100Msps采樣率

模擬帶寬20MHz,輸入電壓的范圍 - -10V ~ +10V

最小分辨電壓 10mV

經(jīng)過高速ADC以后的數(shù)據(jù)通過FPGA(當時就用Lattice的FPGA)進行處理以后送到后面的Cortex M4控制器,再在LCD顯示屏上顯示出來,觸發(fā)、測量電壓、頻率等參數(shù)都在FPGA內(nèi)實現(xiàn)。

用Lattice FPGA + NXP的M4開發(fā)板以及自制的模擬鏈路/ADC構(gòu)建的數(shù)字示波器

今天我們就以這個項目為例,簡單分析一下數(shù)字示波器模擬鏈路部分的設(shè)計要點。

首先我們基于給出的指標需求分析一下:

單通道- 需要一顆單路的ADC

100Msps- 需要一顆采樣率在100Msps以上的ADC

20MHz的模擬帶寬 -意味著最高頻率20MHz的模擬信號,如果用100Msps的采樣率,每個周期會有5個采樣點,留給學員通過FPGA邏輯進行內(nèi)插的空間

+/-10V的最大輸入電壓范圍和最小10mV的電壓分辨率意味著整個模擬鏈路以及ADC能夠處理的信號的動態(tài)范圍為20Vpp/10mV ~ 2000 ~ 63dB

第一個問題:選用多少位數(shù)的ADC?8、10、12、14、16位?ADC的精度的選用要和前面的模擬信號調(diào)理電路共同對付63dB的動態(tài)范圍。理想狀態(tài)下8位的ADC可以提供48dB的動態(tài)范圍、10bit ~ 60dB、12bits ~ 72dB,14bits ~ 84dB,但由于存在著量化噪聲,導致ADC的有效位數(shù)要低于實際使用的位數(shù),也就是12位的ADC,有效的位數(shù)小于12(數(shù)據(jù)手冊顯示 - AD9628在采集20MHz的模擬信號的時候相當于11.6bits). 從這個分析上看,選用一顆12bits/100Msps的ADC就可以滿足系統(tǒng)對動態(tài)范圍的要求。

但,ADC的精度越高,意味著器件內(nèi)部的資源大幅增加,器件的成本以及價格也就大幅增加,在同樣的轉(zhuǎn)換率的情況下,一顆12位的雙通道ADC(AD9628-105)的價格比10位的雙通道ADC(AD9608-105)要高出一倍(以其官網(wǎng)上1000+片的價格做參考),見下面的表格。這多花的十幾美元是否可以通過10bit ADC + 可變增益運放甚至8bit ADC +可變增益運放來實現(xiàn)呢?

ADI公司的高速ADC,可以通過參數(shù)過濾選用最適合自己的器件

這就需要權(quán)衡,需要從系統(tǒng)層面來綜合考慮,引入可變增益放大器可以提供幾十個dB的可調(diào)增益范圍,帶來的挑戰(zhàn)就是:

運放器件本身的價錢、多出來的電路板空間的成本

運放電路設(shè)計(需要仿真)和調(diào)試的難度 - 可調(diào)增益、要保證線性范圍工作、周邊器件的合理選用

最難的可能是運放電路的供電 - 一般都是雙軌、低噪聲的電壓,比如+/-5v或+/-10V,模擬電路的雙軌供電可是難煞了很多工程師,做不好性能會達不到要求。

放大電路的增益要可調(diào)節(jié),如何調(diào)節(jié)?總不能用手擰電位計調(diào)節(jié)吧?需要VGA(電壓控制增益)或模擬開關(guān)切換。電可調(diào)的電路會帶來額外的復雜度以及成本。

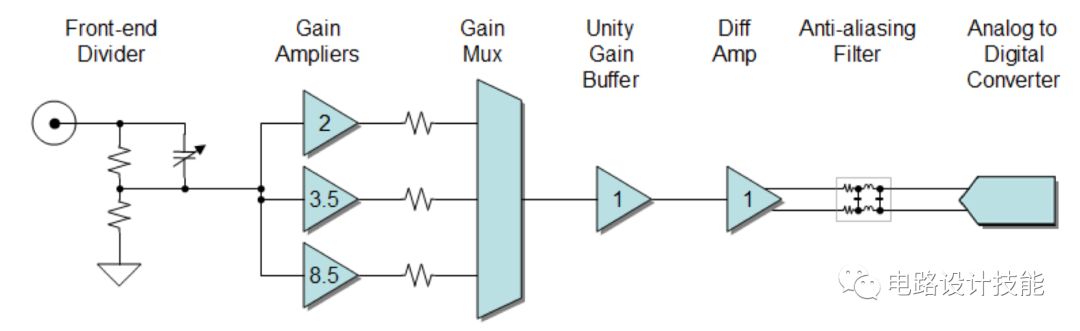

實現(xiàn)數(shù)字示波器模擬前端的方式之一,通過模擬開關(guān)來實現(xiàn)鏈路增益的調(diào)節(jié)

說到這里是不是覺得頭大了?是不是覺得自己的知識量不夠了?這還僅僅是信號的幅度方面的要求,信號的頻率呢,也就是對頻帶的要求呢?即便20MHz以內(nèi)的模擬信號,你需要低通濾波器(防混疊),選用的模擬器件要考慮到增益帶寬積是否滿足要求、瞬間的響應(yīng)速度是不是夠、電壓控制增益的范圍內(nèi)線性度如何?

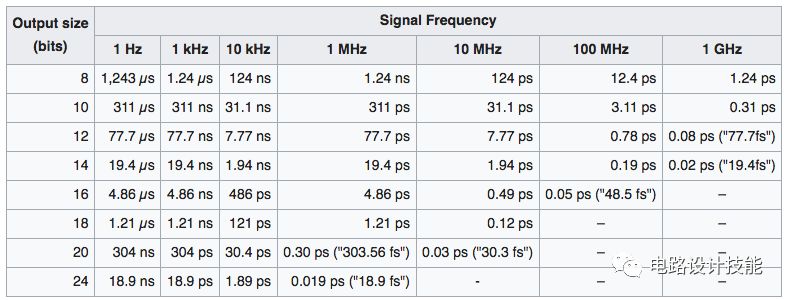

從降低系統(tǒng)復雜度的角度出發(fā),我們希望用一顆高速的ADC,比如14、16bit全部搞定最好,但殺雞用牛刀顯然也是不對的,畢竟要考慮到系統(tǒng)的成本,更重要的是即便從理論分析上14bit的ADC能夠滿足你的要求,但實際的電路中會由于電源噪聲、時鐘抖動等使得你使用更高分辨率的ADC沒有意義。上篇文章中我們講過(下面的表格),即便對于10MHz的模擬信號,用14bit的ADC,采樣時鐘邊沿的抖動必須小于2ps,100MHz(10ns周期)的時鐘抖動要小于2ps,你自己測一下你自己板子上用FPGA產(chǎn)生的100MHz的時鐘的邊沿抖動有多大?是否能小于2ps?

針對不同的模擬信號,采用不同位數(shù)的ADC對時鐘邊沿抖動的要求

所以,如果你用14bits的ADC,那必須給你的ADC提供極小邊沿抖動的采樣時鐘信號,意味著你的時鐘源(一般PLL產(chǎn)生)要非常好,最好采用差分時鐘信號傳輸、時鐘以及ADC的電源去偶要格外注意、PCB的設(shè)計要很講究。所以挑戰(zhàn)會比較大。

越是采樣頻率高的示波器,高分辨率的ADC器件成本會更高,對時鐘抖動的要求越高,成本也會大幅增加,比如500Msps的數(shù)字示波器,如果你做的產(chǎn)品不能賣到非常高的價格讓你有足夠的成本空間采用更好的器件,最好采用8bits的ADC。

因此在學員的實際項目制作中我們也盡量讓學員選用8bit、10bit的ADC配合前端可調(diào)增益的放大器來實現(xiàn)63dB的動態(tài)范圍,下面是幾款當時我們推薦給學員選用的ADC的型號,具體型號的選用還要考慮到供電電壓、功耗、數(shù)據(jù)接口方式、價格等要素。

幾款可用于100Msps數(shù)字示波器的高速ADC

在我們100Msps的項目中我們選用8位的AD9283作為ADC,63dB-48dB ~ 15dB的動態(tài)范圍就通過可控增益的運放來實現(xiàn)。

由于輸入的信號是+/-10V,而ADC一般的輸入電壓范圍是2Vpp,所以需要對輸入的電壓信號先進行10:1衰減(-20dB),得到+/-1V的模擬信號,再通過0-20dB的可變增益控制來滿足ADC的輸入電平要求。

在ADC之前有一個低通濾波器用于對20MHz以上的信號做過濾,主要目的是防止20MHz以上的噪聲通過采樣混疊在被測信號的采樣結(jié)果中。關(guān)于這部分的理論分析大家可以看一下抗混疊采樣相關(guān)的技術(shù)文章。

以上我們簡單分析了一下如何根據(jù)被采集信號的幅度范圍來選取適當分辨率的ADC + 可變增益調(diào)理電路的組合,原則是考慮到電路的性能、可實現(xiàn)性、設(shè)計難度、系統(tǒng)成本等各因素后的綜合折衷。

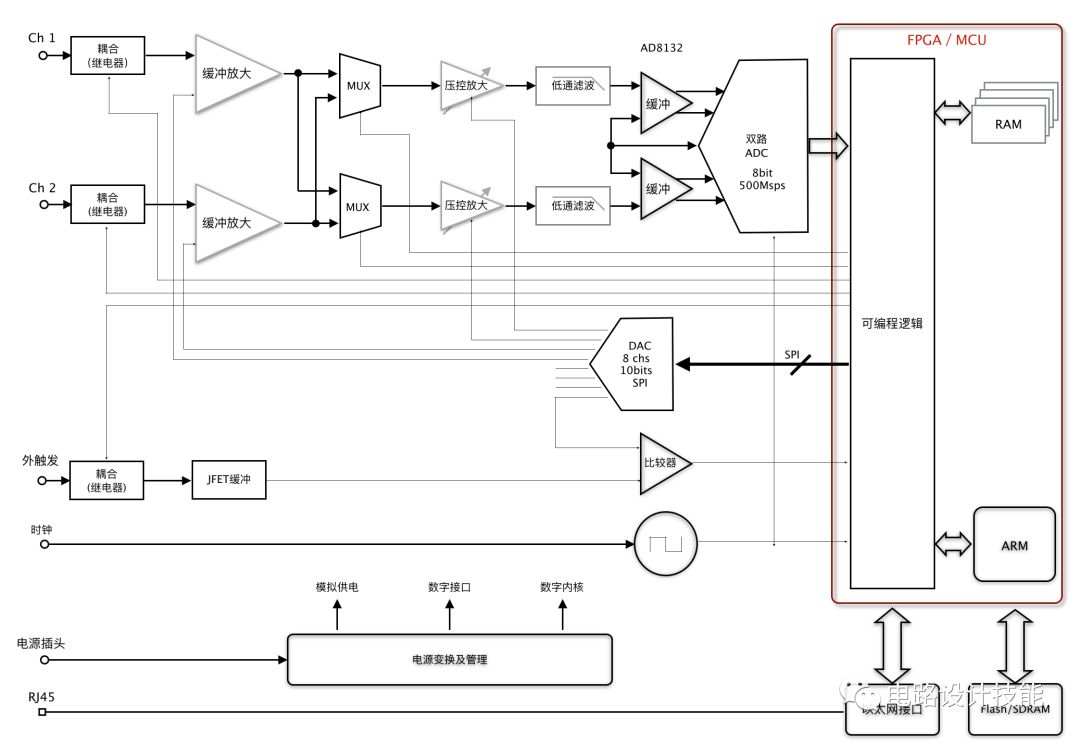

下面的這個圖是我們設(shè)計的一款產(chǎn)品 - 500Msps的雙通道高速數(shù)據(jù)采集系統(tǒng)的框圖,使用的是8位、500Msps的ADC以及ZYNQ FPGA器件,可以通過以太網(wǎng)同上位機PC進行數(shù)據(jù)傳輸。壓控放大器的增益控制電壓是靠低速串行DAC實現(xiàn)。每一級電路的增益、帶寬的設(shè)定原理同上。

限于篇幅,不能對細節(jié)做詳細說明,如有對此有興趣的朋友可以通過留言的方式做進一步的溝通。

-

模擬電路

+關(guān)注

關(guān)注

125文章

1557瀏覽量

102741 -

adc

+關(guān)注

關(guān)注

98文章

6498瀏覽量

544661 -

數(shù)字示波器

+關(guān)注

關(guān)注

6文章

523瀏覽量

33574

原文標題:ADC/DAC(3)- 數(shù)字示波器中ADC的選用

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

關(guān)于ADC應(yīng)用100Msps的數(shù)字示波器的案例分析

ADC芯片的采樣率為100MSPS,位寬16位,那么吞吐量是多少?

【FPGA設(shè)計實例】基于FPGA的數(shù)字示波器設(shè)計

制做一個數(shù)字采樣示波器

MAX19506 雙通道、8位、100Msps ADC

面向醫(yī)療與工業(yè),TI推出8通道100MSPS ADC

數(shù)字存儲示波器制作參數(shù)

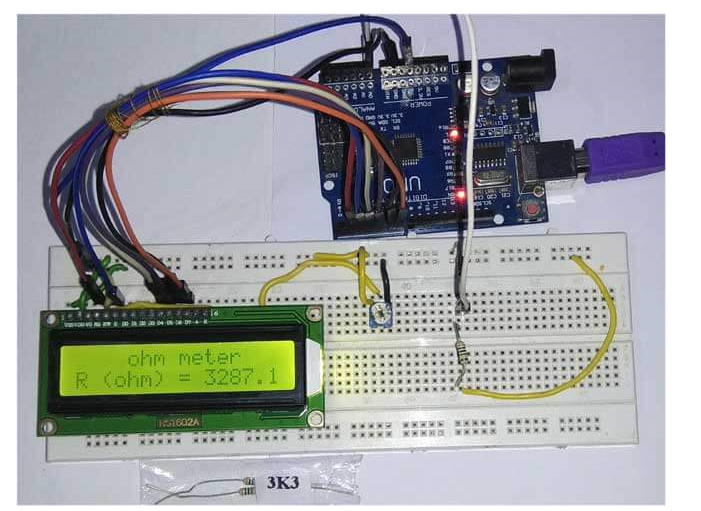

如何使用Arduino來制作一個簡單的歐姆表

DS100 Mini數(shù)字示波器

ADS5263四通道、16位、100MSPS高SNR ADC數(shù)據(jù)表

ADS5295低功耗,12位,100MSPS,8通道模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

100Msps的數(shù)字示波器的制作來做一個簡單的案例分析

100Msps的數(shù)字示波器的制作來做一個簡單的案例分析

評論