FPGA的設(shè)計(jì)就是將自己想要實(shí)現(xiàn)的邏輯通過計(jì)算機(jī)能夠理解的語(yǔ)言描述出來,并讓計(jì)算機(jī)根據(jù)FPGA內(nèi)部的資源生成可以進(jìn)行資源配置并在加電以后能夠執(zhí)行的過程。

人的邏輯和計(jì)算機(jī)之間的橋梁就是HDL - 硬件描述語(yǔ)言,目前有兩個(gè)比較流行的語(yǔ)言Verilog和VHDL,其中Verilog用的更多,在我們的小腳丫FPGA平臺(tái)上也選用了Verilog。

語(yǔ)言就是一個(gè)工具,不同的語(yǔ)言只是語(yǔ)法、規(guī)則不同而已,稍加了解這些語(yǔ)法、規(guī)則應(yīng)該就可以方便地切換到不同語(yǔ)言上。因此在FPGA設(shè)計(jì)時(shí),無論是Verilog、VHDL還是其它更高級(jí)的語(yǔ)言,這都不是FPGA的實(shí)質(zhì),我們?cè)谑褂玫臅r(shí)候也沒有必要糾結(jié)用的是何種語(yǔ)言。

很多做FPGA設(shè)計(jì)的工程師都買過某著名教授的Verilog的教程,非常厚,但普遍反應(yīng)看不懂,從頭到尾看了好幾遍,仍然不會(huì)做FPGA設(shè)計(jì)。

我翻看過基本英文版的FPGA設(shè)計(jì)的教程,沒有一本是專門講Verilog的語(yǔ)言的,多數(shù)是將Verilog的語(yǔ)法和規(guī)則作為附錄放在書的后面供查閱。

因?yàn)閂erilog實(shí)在太簡(jiǎn)單,所有的語(yǔ)法和規(guī)則匯總起來也就兩個(gè)頁(yè)面,對(duì)于學(xué)習(xí)FPGA的初學(xué)者來講了解這些已經(jīng)足夠,更重要的是在實(shí)際的項(xiàng)目中通過具體的使用和調(diào)試來深刻掌握。

Verilog看起來跟C++比較像,但由于它是一門用于描述硬件的語(yǔ)言,因此它跟MCU上運(yùn)行的程序不同,它有一些跟硬件高度相關(guān)的特性需要格外注意。如果把FPGA的邏輯用MCU程序的思路去寫,那就大錯(cuò)特錯(cuò)了。

下面是我們www.stepfpga.com的Wiki系統(tǒng)里對(duì)Verilog的簡(jiǎn)要介紹(詳細(xì)的語(yǔ)法和規(guī)則可以點(diǎn)擊左下角的“閱讀原文”指向的頁(yè)面):

Verilog 是 Verilog HDL 的簡(jiǎn)稱,Verilog HDL 是一種硬件描述語(yǔ)言(HDL:Hardware Description Language),硬件描述語(yǔ)言是電子系統(tǒng)硬件行為描述、結(jié)構(gòu)描述、數(shù)據(jù)流描述的語(yǔ)言。利用這種語(yǔ)言,數(shù)字電路系統(tǒng)的設(shè)計(jì)可以從頂層到底層(從抽象到具體)逐層描述自己的設(shè)計(jì)思想,用一系列分層次的模塊來表示極其復(fù)雜的數(shù)字系統(tǒng)。然后,利用電子設(shè)計(jì)自動(dòng)化(EDA)工具,逐層進(jìn)行仿真驗(yàn)證,再把其中需要變?yōu)閷?shí)際電路的模塊組合,經(jīng)過自動(dòng)綜合工具轉(zhuǎn)換到門級(jí)電路網(wǎng)表。接下去,再用專用集成電路 ASIC 或現(xiàn)場(chǎng)可編程門陣列 FPGA 自動(dòng)布局布線工具,把網(wǎng)表轉(zhuǎn)換為要實(shí)現(xiàn)的具體電路布線結(jié)構(gòu)。

在 FPGA 的設(shè)計(jì)中,我們有多種設(shè)計(jì)方式,如繪制原理圖、編寫描述語(yǔ)言代碼等。早期的工程師對(duì)原理圖的設(shè)計(jì)方式情有獨(dú)鐘,這種輸入方式能夠很直觀的看出電路的結(jié)構(gòu)并快速理解電路。隨著邏輯規(guī)模的不斷攀升,邏輯電路也越來越復(fù)雜,這種輸入方式就會(huì)顯得力不從心,應(yīng)付簡(jiǎn)單的邏輯電路還算實(shí)用,應(yīng)付起復(fù)雜的邏輯電路就不行了。因此取而代之的便是編寫描述語(yǔ)言代碼的方式,現(xiàn)今的絕大多數(shù)設(shè)計(jì)都是采用代碼來完成的。

簡(jiǎn)單地講在Verilog編程中需要注意以下幾點(diǎn):

所有的Verilog程序都以Module(模塊、組件)的方式存在,一個(gè)簡(jiǎn)單的邏輯可以由一個(gè)Module組成,復(fù)雜的邏輯可以包含多個(gè)Modules,每個(gè)Module有獨(dú)立的功能,并由輸入、輸出端口被其它module調(diào)用。通過Module的方式可以將一些比較獨(dú)立、可以復(fù)用的功能進(jìn)行模塊化,代碼閱讀起來也比較直觀;

Verilog的信號(hào)分為wire和register兩種類型,wire可以看成直接的連接,而register具有對(duì)某一個(gè)時(shí)間點(diǎn)狀態(tài)進(jìn)行保持的功能,因此在設(shè)計(jì)邏輯的時(shí)候要明確定義每個(gè)信號(hào)是wire還是reg屬性;

并行執(zhí)行:Verilog描述的主要是硬件而不是軟件,因此也就意味著其描述的各個(gè)功能之間可以并行執(zhí)行,比如在你的設(shè)計(jì)中你有3個(gè)計(jì)數(shù)器,每一個(gè)計(jì)數(shù)器都連接到不同的時(shí)鐘上,這是沒有問題的,每一個(gè)時(shí)鐘都干自己的事。不像MCU,只有一個(gè)線程按照順序執(zhí)行。

由于篇幅所限,我們就不對(duì)這個(gè)語(yǔ)言的具體語(yǔ)法、規(guī)則進(jìn)行展開,在此借用Stanford大學(xué)的Paul Hartke教授的Verilog課程的PPT頁(yè)面來對(duì)Verilog的語(yǔ)法和規(guī)則做個(gè)簡(jiǎn)單的介紹(正好可以借此提升一下自己的專業(yè)英語(yǔ)閱讀能力),可以看到斯坦福大學(xué)的學(xué)生學(xué)習(xí)Verilog也就十幾個(gè)頁(yè)面的內(nèi)容。

使用Verilog設(shè)計(jì)FPGA的流程

Module是Verilog最基本構(gòu)成方式

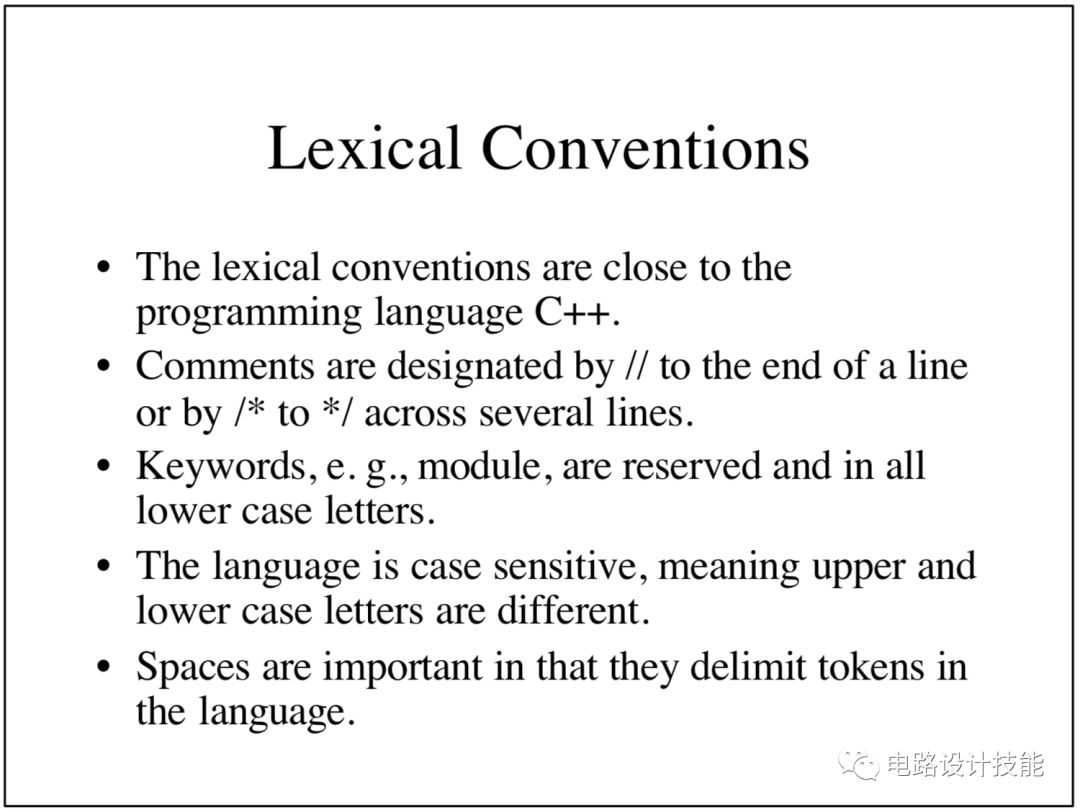

Verilog的語(yǔ)法規(guī)定跟C++比較接近

數(shù)值規(guī)范

按位/邏輯操作符

混合操作符

一元減數(shù)操作符(教授說它從來沒有在實(shí)際的應(yīng)用中看到過、用過)

連續(xù)賦值

過程賦值

if-else條件過程賦值

邏輯操作符

關(guān)系操作符

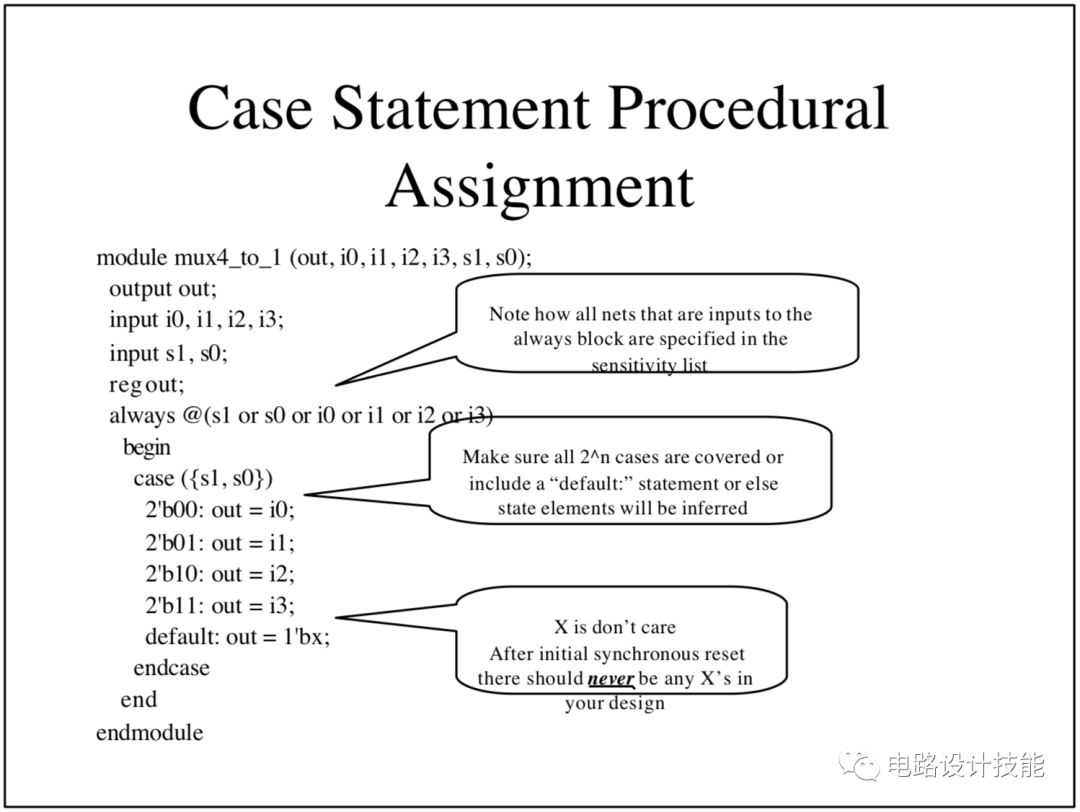

Case Statement過程賦值

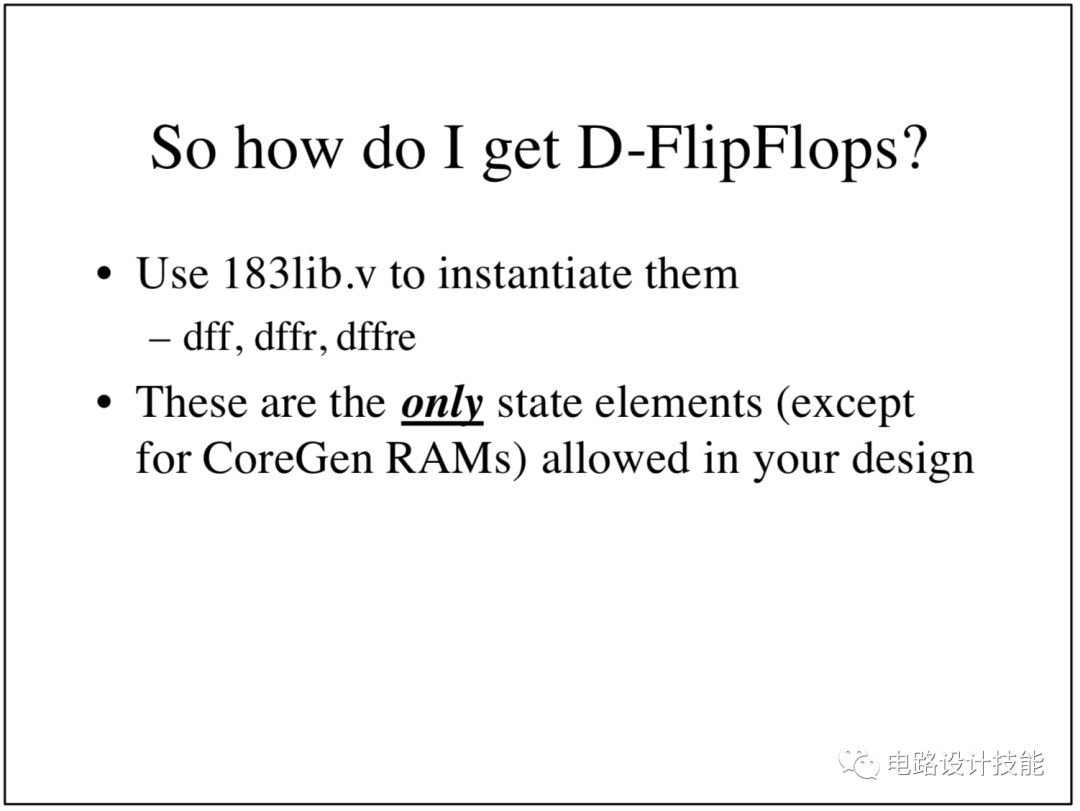

如何得到一個(gè)D觸發(fā)器?

在有限狀態(tài)機(jī)(FSM)中使用Case Statement

-

FPGA

+關(guān)注

關(guān)注

1630文章

21769瀏覽量

604648 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110187 -

編程

+關(guān)注

關(guān)注

88文章

3633瀏覽量

93853

原文標(biāo)題:Verilog編程的要點(diǎn)

文章出處:【微信號(hào):xiaojiaoyafpga,微信公眾號(hào):電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

哪有FPGA的verilog編程基礎(chǔ)知識(shí)?

【信盈達(dá)】C語(yǔ)言知識(shí)點(diǎn)的總結(jié)

《Verilog HDL數(shù)字系統(tǒng)設(shè)計(jì)教程》(第四版)學(xué)習(xí)筆記 part1 Verilog數(shù)字設(shè)計(jì)基礎(chǔ)——第一章知識(shí)點(diǎn)總結(jié)

高一數(shù)學(xué)知識(shí)點(diǎn)總結(jié)

高二數(shù)學(xué)知識(shí)點(diǎn)總結(jié)

Verilog編程語(yǔ)言界面入門知識(shí)簡(jiǎn)介

使用C語(yǔ)言進(jìn)行單片機(jī)編程的基本知識(shí)點(diǎn)和編程規(guī)范資料總結(jié)

嵌入式知識(shí)點(diǎn)總結(jié)

Verilog是編程語(yǔ)言嗎

開關(guān)電源模塊知識(shí)點(diǎn)總結(jié)

Verilog如何編程?Verilog編程知識(shí)點(diǎn)總結(jié)

Verilog如何編程?Verilog編程知識(shí)點(diǎn)總結(jié)

評(píng)論