據麥姆斯咨詢介紹,為了降低成本,半導體行業一直在致力于開發創新的解決方案。而終端客戶則一直在尋求具有更高性能的低成本封裝解決方案。

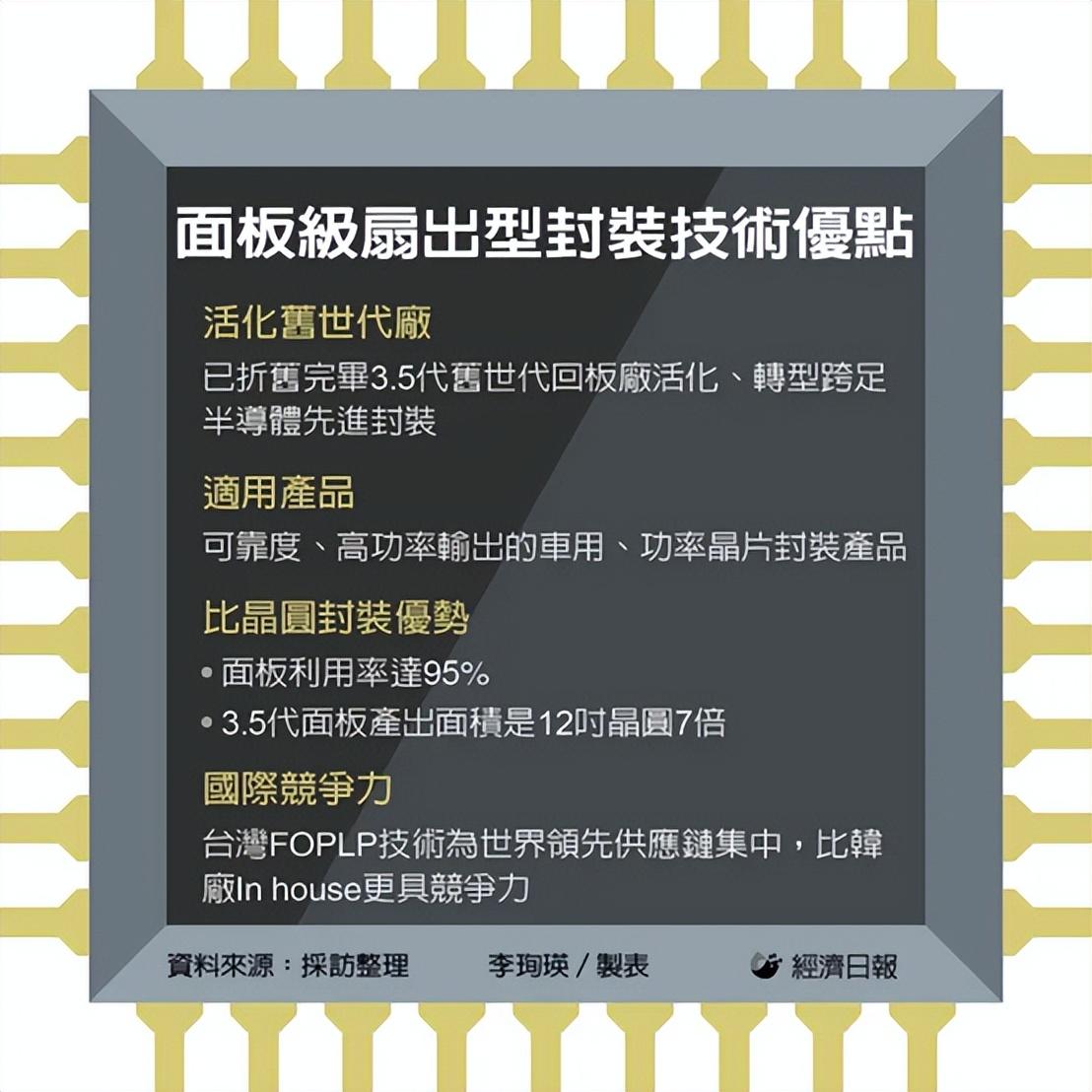

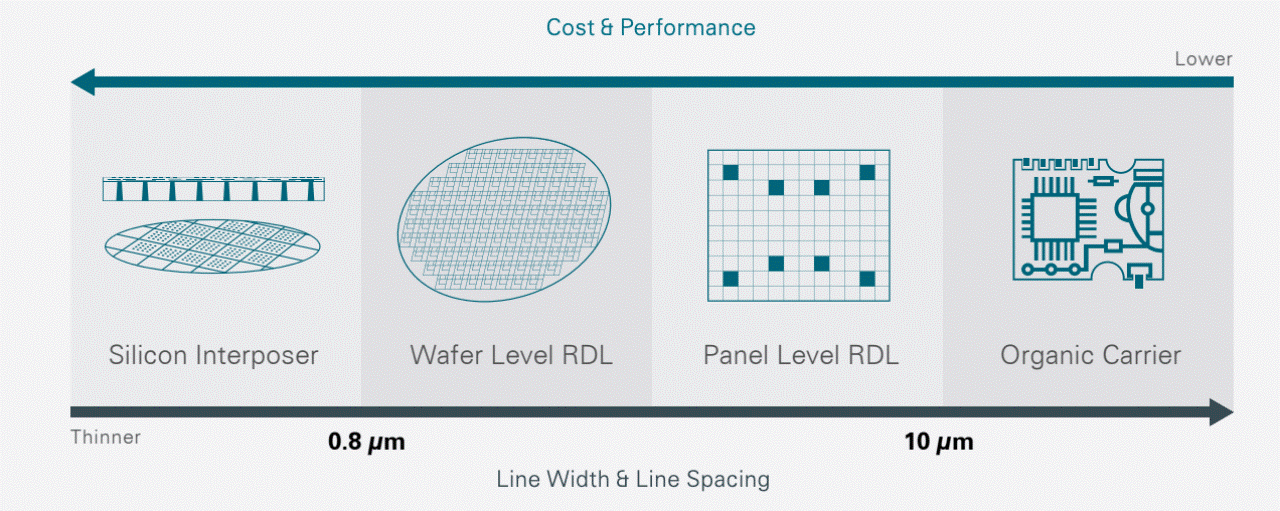

面板級封裝(PLP)就是一種從晶圓和條帶級向更大尺寸面板級轉換的方案。由于其潛在的成本效益和更高的制造效率,吸引了市場的廣泛關注。由于面板的大尺寸和更高的載具使用率(95%),它還帶來了遠高于晶圓級尺寸扇出型晶圓級封裝(FOWLP)的規模經濟效益,并且能夠實現大型封裝的批量生產。

在應用和市場方面,許多封裝技術可以被視為PLP,但由于FOWLP的成功和市場認識,使FOPLP吸引了更多關注,包括許多不同商業模式的廠商,例如外包半導體組裝和測試廠商(OSAT)、集成器件制造商(IDM)、代工廠、基板制造商和平板顯示(FPD)廠商。它們感覺有機會通過扇出型技術涉足先進封裝業務。

經過多年的發展,FOPLP已經成功開發,2018年至2020年期間將有多家廠商開始量產。FOPLP將成為增長最快的封裝平臺之一:根據Yole在2018年發布的《板級封裝(PLP)技術及市場趨勢-2018版》報告,FOPLP市場將在2017~2023年期間以驚人的79%復合年增長率(CAGR)在2023年增長至約2.79億美元。

板級封裝平臺的市場驅動因素

眾多涉足FOPLP業務的廠商中,三星電機(SEMCO)可能是最激進的:這家領先的公司過去兩年來在該領域投資超過4億美元,并最終利用該技術為其新款消費類產品——Galaxy Watch智能手表生產集成應用處理器單元(APU)。

憑借這一高密度FOPLP的首次亮相,SEMCO率先宣布了FOPLP的到來。利用這項技術,三星Galaxy Watch將電源管理集成電路(PMIC)、應用處理器和動態隨機存取存儲(DRAM)都集成在了同一個大型封裝中(稱為SiP-ePoP)。PMIC和應用處理器芯片并排放置,利用一個嵌入式PCB基板實現封裝中頂部/底部的連接。

針對這款產品,麥姆斯咨詢合作伙伴——System Plus Consulting近期發布了一份題為《Exynos 9110:三星第一代扇出型面板級封裝(FOPLP)》的報告。

隨著FOPLP在智能手表中的應用,三星顯然正準備在消費領域大展拳腳。除了智能手表,移動市場應該很快會受到FOPLP應用的影響。憑借這一戰略性技術選擇,SEMCO明確瞄準了臺積電(TSMC)在高密度扇出封裝領域的領導地位,并為FOPLP的技術開發制定了積極的發展路線圖。現在,巨頭之間在高端扇出型封裝領域的較量即將上演。

在此背景下,Yole韓國分部負責人兼首席分析師Santosh Kumar最近采訪了SEMCO副總裁兼企業戰略與規劃團隊負責人Richard(KwangWook)Bae,了解了SEMCO近期的FOPLP發展情況,以及他們對FOPLP業務的愿景和未來趨勢的看法。

Santosh Kumar(以下簡稱SK):請您簡要介紹一下SEMCO及其業務。

Richard(KwangWook)Bae(以下簡稱RB):SEMCO成立于1973年,是三星集團的附屬子公司。SEMCO的全稱是Samsung Electro-Mechanics,是電子元件行業的領導者之一。

我們的總部位于韓國水原。海外工廠位于中國、泰國、菲律賓和越南。我們還在美國、歐洲、日本、中國和東南亞設有銷售辦事處。

SEMCO現在主要由三個業務部門組成:

元件解決方案,生產無源元件,如多層陶瓷電容(MLCC)和電感;

基板解決方案,生產高密度互連板(HDI)、封裝基板和RFPCB;

模組解決方案,生產攝像頭模組、WiFi模組。

2016年,我們成立了新的FOPLP部門,并建設了生產線。我們開始為2018年8月發布的Galaxy Watch制造用于應用處理器(AP)的FOPLP產品。

SK:恭喜你們成為第一家FOPLP進入量產的廠商。您能否介紹一下SEMCO的FOPLP技術,包括面板尺寸和技術規格。

RB:我們使用510 x 415mm尺寸的面板制造FOPLP,但我們已經開發出了高達800 x 600mm規格的面板。因此,面板尺寸可以根據客戶要求更改。

我們用于Galaxy Watch的FOPLP有3個重布線層(RDL)和1個背面RDL(Backside RDL)。我們將標準的層疊(PoP)結構應用于AP和PMIC的多芯片封裝。通過應用FOPLP,我們可以將封裝的厚度減少20%以上,從而提高了電氣和熱性能,并有助于擴大產品的電池容量。

SK:涉足扇出型封裝業務,SEMCO進入了由OSAT和一家大型代工廠主導的領域。您如何看待面臨的挑戰?您認為誰將是你們在扇出型封裝領域更大的競爭對手:代工廠還是OSAT?未來,你們是否計劃擴展封裝服務組合?

RB:我認為半導體行業未來將劃分為兩大板塊:

獨特的業務仍然存在:代工廠、OSAT、基板公司將維持自己的業務;

供應鏈的分工將逐漸變得模糊,前端和后端之間的邊界將不再那么分明。

從根本上來說,我們認為未來代工廠、OSAT、基板公司自己的業務將繼續維持。但是,在前端和后端整合的部分,我認為需要三個條件:

1、大規模投資;

2、克服技術障礙;

3、克服先進節點晶圓的供應問題。

SK:從經濟角度來看,產業對于面板級扇出封裝的可行性存在一些疑慮。大多數廠商認為,由于市場規模還不足以滿足產線的滿產運行,因此,行業仍然沒有做好迎接扇出型面板級封裝的準備。您對這種觀點有什么看法?

RB:首先,AP、PMIC等單芯片封裝需要大規模生產,因此需求量預計已經足夠了。我們正在與客戶合作以響應它們的要求。此外,對于異構集成和扇出型系統級封裝(FOSiP),多個芯片將被封裝到一個大型封裝中。

面板級比晶圓級更具競爭力。隨著封裝尺寸的增長,晶圓面積的利用率正在降低。因此,對于FOSiP,來自面板的封裝數量多于來自晶圓的封裝數量。由于這些原因,FOPLP應該有利于異構集成或FOSiP。此外,各種應用的市場需求也將繼續增長。

SK:就芯片/封裝尺寸方面,扇出型面板封裝的優勢在哪里體現?對于此類封裝尺寸,轉換到面板級封裝,您預計可以降低多少成本?

RB:目前FOPLP主要用于移動應用。但在不久的將來,FOPLP將擴展到尺寸超過15 x 15的異構集成。

到2020年或2021年,由于5G、人工智能(AI)、自動駕駛和服務器需求,對模塊化和高速數據處理的需求將急劇增長。FOPLP可以滿足這些需求,因此在多芯片封裝方面,FOPLP將成為主流。

FOPLP和FOWLP之間的比較,僅在成本方面進行了討論。但是,我認為FOPLP有兩種類型的應用,一種是成本驅動型,另一種是性能驅動型。在成本驅動的領域,FOPLP在生產方面具有優勢。然而,就性能驅動的應用而言,由于SEMCO設計的架構,FOPLP在精細間距方面更勝一籌,同時改善了熱性能和電氣性能。因此,對于扇出系統級封裝和異構集成它都能勝任。

Galaxy手表及Exynos 9110拆解與逆向分析

SK:SEMCO是主要的基板供應商之一。您如何看待扇出型封裝的廣泛應用對基板業務產生的不利影響?SEMCO的應對策略是什么?

RB:SEMCO已經為無源和有源器件的嵌入技術準備了10余年。由于半導體節點在不斷縮小,我們認為封裝基板應該做出改變。

基于這些準備,我們及時開發出了FOPLP,并積極響應需要扇出封裝的市場,例如高階AP、內存和小型IC等。

我們專注于無源元件(包括MLCC、基板和模組)等電子元件。因此,我們可以通過其他組件的定制化來優化FOSiP。

此外,還有一些應用需要繼續使用現有的封裝基板。并非所有應用都會從基板轉向PLP。因此,這不是一場零和游戲。此外,基板業務將支持FOPLP業務。

基于基板和PLP技術,我們可以更好地響應客戶需求和技術的變化。

SK:你們的FOPLP面向哪些細分應用和器件?

RB:SEMCO為Galaxy Watch實現了FOPLP的全球首次量產。此外,我們期望將FOPLP不僅應用于小型IC,還包括AI、5G、汽車和服務器等高性能計算(HPC)應用。特別是,我們為各種應用開發了下一代扇出型系統級封裝模組(FOSiP)。

SK:許多設備供應商已經開發了應用于面板級扇出技術的機臺。在您看來,設備供應鏈中存在哪些差距需要解決?

RB:SEMCO自2015年以來一直與全球設備公司共同開發FOPLP。我們得到了這些公司的充分支持,因此未來不會出現問題。

SK:面板尺寸的標準化是面板級扇出應用的瓶頸之一。許多廠商正在研究不同的面板尺寸。您認為這個問題將如何解決?

RB:我們使用415 x 510面板,因為它是我們當前應用的最高效的尺寸。此外,在市場上,我們的面板尺寸被認為足以滿足當前的應用。

由于SEMCO擁有基板業務,我們已經擁有更大面板的批量生產經驗。我們可以將這些積累用于FOPLP業務。我們可以靈活地響應面板尺寸的變化,不會有任何問題。

對于成本驅動的應用,目前有幾家供應商正在開發FOPLP。在這種情況下,如果面板尺寸、載具和材料是標準化的,我認為這對FOPLP生態系統是有利的。

SK:與FOWLP相比,您是否看到FOPLP對模塑料、介電材料、電鍍化學等材料的特殊要求?

RB:基本上,FOWLP和FOPLP使用類似的PID材料、設備和條件。不同之處在于形狀和材料不同的載具類型。

SK:FOPLP面臨的主要技術挑戰是什么?你們如何應對這些挑戰?

RB:FOPLP中的技術問題主要包括大面積RDL形成、焦深裕度(DoF margin)、芯片位移、翹曲處理和微粒控制。SEMCO已經解決了這些挑戰,掌握了控制技術。

SK:您認為FOPLP市場將如何發展?更廣泛應用的主要障礙是什么?

RB:到2020年或2021年,由于5G、AI、自動駕駛和服務器等高性能計算需求,半導體器件將變得更加復雜。同時,還將需要在存儲器和邏輯芯片之間進行高速數據傳輸。由于FOPLP能夠通過多芯片封裝實現高速數據傳輸,因而將促進FOPLP的更廣泛應用。

SK:對于異構集成和2/2 L/S或以下的封裝能力,您是否認為面板級扇出路線圖和晶圓級扇出路線圖一致(甚至超過)?SEMCO未來5年的FOPLP路線圖(在封裝設計參數方面,如RDL L / S和層數、間距、厚度、尺寸等)將如何規劃?

RB:如前所述,FOWLP和FOPLP是類似的技術。所以路線圖和目標應用基本相似。

不過,PoP堆疊的間距規格有差異。由于結構上的差異,我們的PLP可以獲得更好的間距。此外,PLP具有不需要芯片凸點的優勢。

作為電子器件工程聯合委員會(JEDEC)標準, 2/2 L/S足以滿足未來高性能計算或FOSiP等高端應用的需求。很少需要低于2/2的L/S,那些僅是一些特殊產品的利基市場。

-

三星電子

+關注

關注

34文章

15868瀏覽量

181123 -

封裝

+關注

關注

127文章

7962瀏覽量

143160

原文標題:三星先進封裝戰略:扇出型面板級封裝(FOPLP)

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星與臺積電在FOPLP材料上產生分歧

整合為王,先進封裝「面板化」!臺積電、日月光、群創搶攻FOPLP,如何重塑封裝新格局?

三星扇出型面板級封裝FOPLP戰略性技術選擇

三星扇出型面板級封裝FOPLP戰略性技術選擇

評論