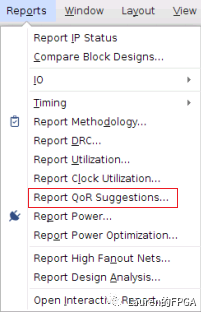

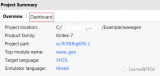

從Vivado 2018.3開始,可以通過圖形界面方式使用命令report_qor_suggestions,如圖1所示。從Tcl角度而言,就是多了一個-name選項。

圖1

report_qor_suggestions的功能是在分析設計的基礎上給出改善設計的建議,這些建議可以用.xdc或.tcl文件的形式體現出來,無論是Project模式還是Non-Project模式,這些文件均可加入工程中使用最終達到優化設計的目的。本質上,這些建議是與UFDM(UltraFast Design Methodology)保持一致的。

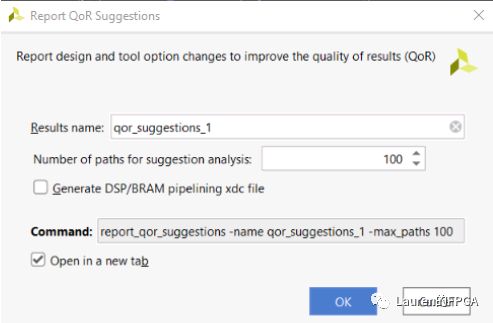

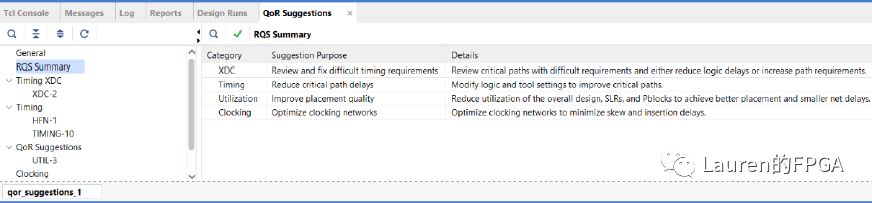

在圖形界面方式下使用report_qor_suggestions會顯示如圖2所示界面,最終生成如圖3所示的Summary。

圖2

圖3

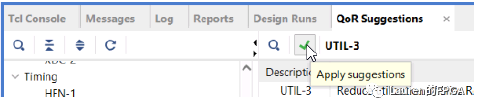

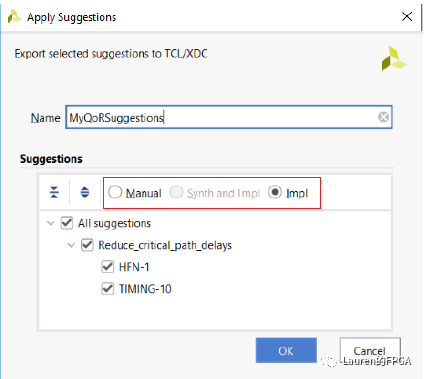

點擊Apply Suggestions按鈕,如圖4所示,會彈出圖5所示界面。最終會生成針對設計的優化建議,也就是前文所述的.xdc或.tcl文件。

圖4

圖5

在圖5中,Manual用于顯示無法以.xdc或.tcl形式提供的建議。Synth and Impl用于生成可應用于Synthesis和Implementation階段的建議,而Impl用于生成僅適用于Implementation階段的建議。

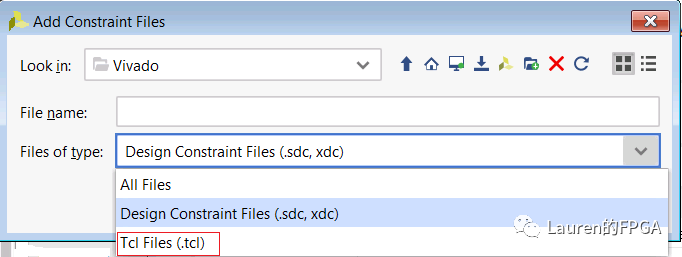

如果選擇Synth and Impl,會生成兩個文件:RQSPreSynth.tcl和RQSImplCommon.tcl。Project模式下,RQSPreSynth.tcl可作為約束文件直接添加到Constraint Set里(Vivado支持.tcl文件作為約束文件,添加時將文件類型切換為.tcl即可,如圖6所示)。

圖6

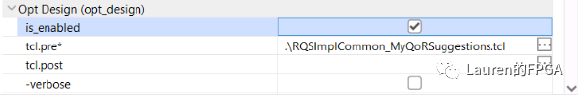

RQSImplCommon.tcl則應作為Hook Script在Opt Design階段添加,如圖7所示。

圖7

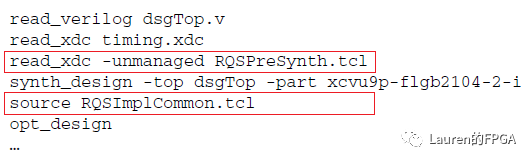

Non-Project模式下,這兩個文件的添加方式如圖8所示。

圖8

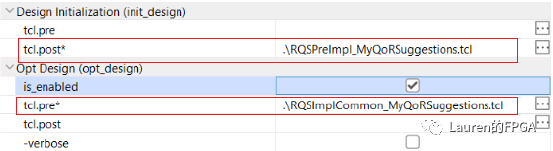

如果選擇Impl,則會生成兩個文件RQSPreImpl.tcl和RQSImplCommon.tcl。兩者添加位置如圖9所示。

圖9

Non-Project模式下,這兩個文件的添加方式如圖10所示。

圖10

對于Vivado 2018.3之前的版本,盡管沒有圖形界面方式,但可直接通過Tcl命令執行。添加-output_dir選項,指定文件生成目錄,可在指定位置生成上述文件。需要注意的是RQSPreSynth.tcl和RQSPreImpl.tcl兩者是不能同時使用的。

對于一些以DSP、BRAM或URAM為起點或終點的路徑,如果這些模塊自帶的一些流水寄存器沒有使能,可通過選項-evaluate_pipelining生成額外的約束使能這些流水寄存器。但要特別注意,這時設計的功能已經被修改,生成的約束只能用于評估這些流水寄存器被使能的情況下對設計時序的影響。就時序評估而言,相比于通過修改RTL代碼使能這些寄存器,采用選項-evaluate_pipelining更快捷。如果使能這些寄存器能改善時序,那么可以再返回修改RTL代碼,保證設計功能正確。

常見問題:

Q: 什么階段使用report_qor_suggestions?

A: 該命令可在Synthesis和Implementation的任意階段使用,但從Baselining的角度而言,最先在哪個階段發現時序違例,就在那個階段使用。

Q: 該命令生成的.tcl文件在哪里?

A: 如果直接在Tcl Console中輸入該命令,相應的.tcl文件生成目錄由選項-output_dir確定;如果是通過圖形界面方式使用,相應的.tcl文件在當前工作目錄下。當前工作目錄可通過命令pwd查詢。

結論

report_qor_suggestions會在分析關鍵路徑的基礎上給出優化建議,生成相應的.tcl文件,而這些文件可加入工程中執行達到優化的目的。

-

寄存器

+關注

關注

31文章

5343瀏覽量

120377 -

Vivado

+關注

關注

19文章

812瀏覽量

66539

原文標題:Vivado 2018.3 report_qor_suggestions怎么用

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么不用2017.4或者2018.3呢?最穩定的vivado版本是哪一種?

Vivado 2018.3這個Gadget你用了嗎?

關于Vivado 2019.1的Dashboard功能詳解

Report QoR Suggestions助力解決Vivado設計問題

解決方法論問題可提升實現的一致性

FPGA設計:關于Report QoR Assessment 命令的使用

基于Vivado/SDK 2018.3的XIP參考設計

【Vivado那些事】Vivado下怎么查看各子模塊的資源占用?

賽靈思Vivado ML版優化應用設計

如何建立Vivado工程以及硬件配置

Vivado使用進階:讀懂用好Timing Report

在Vivado中利用Report QoR Suggestions提升QoR

Vivado 2018.3 report_qor_suggestions怎么用

Vivado 2018.3 report_qor_suggestions怎么用

評論