與任何電子電路一樣,當瞬態電壓浪涌超過元件額定值時,能量收集設計可能會發生災難性故障。隨著人們越來越關注在極低電壓可穿戴設備和物聯網中利用能量收集,設計人員需要敏銳地意識到破壞性電壓浪涌的來源及其緩解方法。通過在設計過程早期認識到對瞬態電壓抑制(TVS)器件的需求,工程師可以構建更強大的設計,能夠在許多瞬態電壓浪涌源中存活。

突然釋放導致瞬態電壓浪涌與電源波動,突然負載變化,耦合效應,閃電和靜電放電(ESD)等相關的能量。對于電路設計者來說,瞬態下的能量突發通常起源于位置,并且由于遠離受影響電路的情況。例如,遠距離雷擊的強電場和磁場可以耦合到數據線和電源線中,從而可以很好地從雷擊本身中消除大的浪涌電壓。

ESD是由允許帶電的條件造成的通過接觸和分離兩種非導電材料,直到帶電體與另一種低電位物體接觸為止。例如,在特別干燥的一天穿過地毯可能導致35kV的電荷(表1)。如果應用于未受保護的可穿戴設備或物聯網系統,ESD瞬態可能會永久性地損壞敏感數字電路。

生成方式10-25%RH 65-90%RH走過地毯35,000 V 1,500 V走路乙烯基瓷磚12,000 V 250 V <! - 重復以下tr以獲得更多行 - >工作人員在工作臺6,000 V 100 V聚乙烯袋從工作臺上取出20,000 V 1,200 V椅子與聚氨酯泡沫18,000 V 1,500 V

表1:在特別干燥的日子里在地毯上輕松走動會導致ESD瞬態大到足以永久性地損壞電子設備,而電子設備的保護不足以防止瞬態電壓浪涌。

當電荷作為電源或電源構建時會出現類似的問題。 USB電纜拖過地毯或由已經產生靜電的個人處理。當個人將電纜接觸到可穿戴設備的電源端口或物聯網設備的通信端口時,突然放電的瞬態可能會對電子系統造成永久性損壞。

內部保護

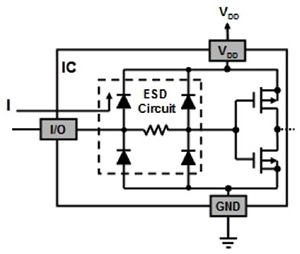

大多數IC都包含內部保護電路,旨在防止因制造和組裝過程中可能發生的ESD沖擊而導致的故障。 I/O線路內部保護的常用方法依賴于二極管陣列,該陣列設計用于將浪涌電流引導到電源軌中,其中瞬態電壓脈沖的能量被消散。正浪涌脈沖將被鉗位到一個電壓,該電壓等于高于電源電壓的正向二極管電壓降(V <小> DD )。由于V SS 引腳通常接地,負脈沖將被鉗位到地下一個二極管壓降。

圖1:半導體制造商使用各種專有方法提供器件級保護,包括使用內部二極管陣列將電流引導遠離IC內的敏感電路。 (由安森美半導體提供)

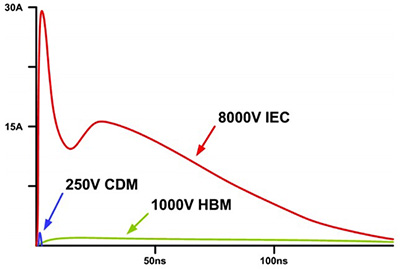

內部保護電路通常能夠防止組裝中發生的ESD故障,但通常不足以防止在正常產品使用中發生的浪涌事件。半導體行業反映了使用器件級和系統級模型來表征ESD保護的這種差異。人體模型(HBM)或充電設備模型(CDM)是設備級規范,旨在在制造和組裝期間提供對隔離設備的保護。 HBM測試在ANSI/ESDA/JEDEC JS-001標準中正式規定。 IEC 61000-4-2和ISO 10605用于表示系統級使用情況,反映更高,更快的電壓浪涌波形(圖2)。

圖2:設備級保護標準指定的電流水平明顯低于系統級標準 - 分別代表組裝和使用過程中可能出現的瞬態浪涌。雖然不同半導體器件的數據表可能提供HBM ESD額定值,但系統級額定值通常僅包括保護IC或針對惡劣環境的IC。 (德州儀器公司提供)

大多數半導體器件缺乏系統級額定值是成本和效率的問題。二極管的浪涌抑制能力與其結區直接相關,并且隨著技術節點的不斷縮小,強大的系統級ESD保護的集成變得更加昂貴和困難。因此,內部保護不僅受到保護水平的限制,而且還受到浪涌數量的限制。相比之下,外部TVS設備能夠分配足夠的芯片空間來提供系統級保護,并為無限量的浪涌提供免疫力。

外部TVS設備旨在限制通過電流的電流。通過降低浪涌電壓的大小來保護IC。理想的外部TVS器件將在IC的內部保護電路之前導通,并消除浪涌的所有能量。實際上,外部和內部保護電路通常在浪涌事件期間開啟。只要流經IC內部保護電路的電流仍然限制在較低值,IC的可靠性將基本不受影響。

外部瞬態保護器件的替代方案中,TVS二極管通常提供較低的工作電壓與其他瞬態抑制設備(如壓敏電阻和晶閘管)相比,電容值更低,動態電阻值更低。此外,TVS器件能夠非常快速地恢復到高阻態,從而實現高ESD多擊吸收能力。

關鍵布局

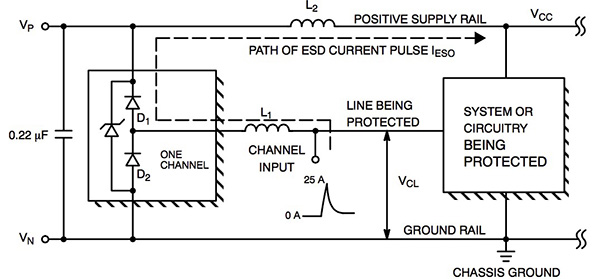

即使使用高效的TVS器件也是如此,有效的保護主要取決于設計的物理布局。作為一般規則,ESD器件應盡可能靠近預期的靜電放電點,電源旁路電容應盡可能靠近器件的正電源軌(VP)引腳放置。同時,設計人員需要最大限度地減少電源,接地層以及信號輸入和ESD器件之間的PCB走線長度,以減少電源軌上的雜散串聯電感和受保護器件的輸入線(圖3) 。

圖3:高效的PCB布局對于降低瞬態電壓至關重要,而較新的TVS器件如安森美半導體CM1293A-02SO則結合了一對二極管(D1和D2)帶有集成齊納二極管,可降低電源軌上的寄生串聯電感L2。 (由安森美半導體提供)

即使PCB走線上的小寄生串聯電感也會導致鉗位電壓顯著增加。為了幫助降低寄生電感,安森美半導體CM1293A-02SO在VP和VN(負電源軌)(圖3左側)上集成了一個齊納二極管。該集成齊納二極管通過將齊納二極管的擊穿電壓鉗位電壓,大大降低了電源軌電感(圖3中的L2)的影響。

對于可穿戴設備甚至物理空間非常寶貴的物聯網設備等設計,工程師可以找到緊湊型封裝的TVS設備。例如,安森美半導體提供0.3 V ESD7381MUT5G TVS,采用0.60 mm x 0.30 mm XFDFN封裝,高度為0.3 mm,CM1205-08CP TVS采用8個TVS器件集成在一個1.3 mm x 0.65 mm晶圓級芯片級封裝中(WLCSP)高度僅為0.4 mm。

設備特性

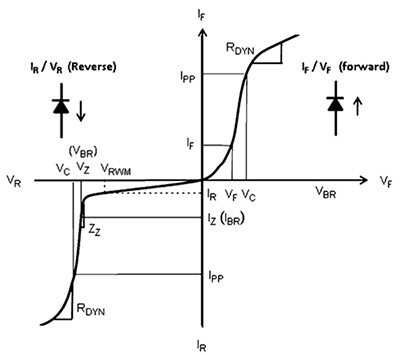

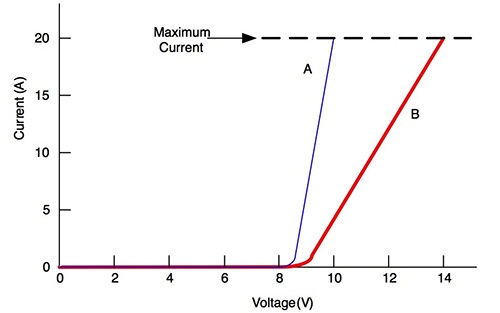

工程師可以找到各種可用的TVS設備,但找到最符合設計要求的部件取決于仔細查看特定設備的特性。典型的TVS器件I-V曲線表現出熟悉的擊穿效應,但高于和低于該擊穿電壓(VBR)的電壓電平對于理解TVS性能非常重要(圖4)。與齊納二極管不同,隨著PN結溫度的升高,擊穿電壓降低,TVS器件是雪崩器件,隨著PN結溫度的升高,擊穿電壓也會增加。因此,工程師可能需要在確定環境溫度下與標準25°C顯著不同的特定特性時考慮溫度。

圖4:典型單向TVS器件的IV曲線關鍵規格的相對電壓電平:工作峰值反向電壓(VRWM),擊穿電壓(VBR)和鉗位電壓(VC)。理想的雙向TVS設備將顯示相同的正向和反向特性。 (由Toshiba提供)

在最低閾值,反向工作電壓VRWM(也稱為隔離電壓,Vst-off)時,器件顯示為關閉,只有其寄生效應和漏電流影響電路。 VRWM通常比反向擊穿電壓VBR(也稱為齊納電壓,VZ,用于基于齊納的器件)低10%至15%,其中TVS器件開始導通,進入其雪崩區域。最后,鉗位電壓VC通常比VBR高35%到40%,代表器件在指定峰值沖擊電流IP下的最大鉗位電壓。

峰值功耗(PPP)當然是一個非常重要的特征。制造商通過在監控設備電壓和電流的同時強制通過TVS的指定電流波形來測量PPP。峰值功率測量中使用的最常見波形是8/20μs和10/1000μs電流波形。 (在此表示法中,第一個值以μs為單位描述波形的上升時間,第二個值以μs為單位描述波形下降到其峰值一半的時間。)盡管PPP并未始終明確列在器件數據表中,但工程師可以簡單地通過將峰值脈沖電流(IPP)乘以鉗位電壓(VC)得出它:

PPP = VC x IPP

動態電阻(RDYN)是確定適用性的另一個重要特性特別保護IC。當電流在瞬態浪涌期間流過保護裝置時,RDYN將導致進一步的電壓降。

對于特定應用,最合適的TVS裝置是具有等于最大連續DC或VRWM的裝置。應用電路在正常工作時將經歷的峰值 - 交流電壓。同時,工程師需要確保VC不超過電路中其他組件安全工作條件可接受的瞬時電壓水平。最后,RDYN必須足夠低,以確保在峰值電流時器件自身的動態電阻不會導致鉗位電壓超過可接受的限值(圖5)。

圖5:即使兩個器件A和B指定相同的擊穿電壓和峰值電流,如果器件B具有比器件A更高的動態電阻(RDYN),器件B可能是一種效率較低的保護裝置,因為它達到了更高的鉗位電壓(紅線)。 (安森美半導體提供)

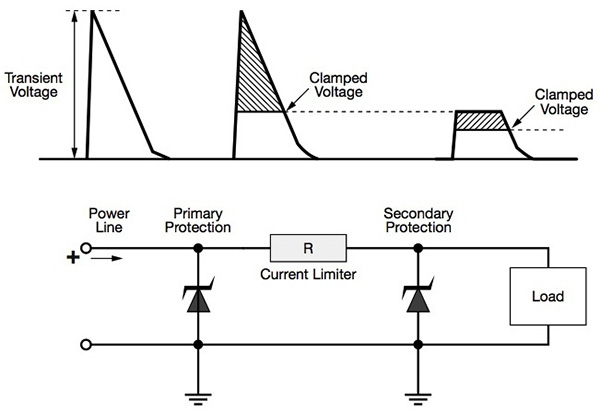

最后,工程師可以利用具有不同工作電壓的器件組合,為太陽能收集等高壓應用提供額外保護。對于此類應用,設計人員可以使用具有不同VRWM規格的多個TVS器件,以降低單個TVS器件在高壓瞬態事件中可能必須消耗的總能量(圖6)。在這里,諸如Vishay SMBJ24D(24 V VRWM)之類的設備將提供主要保護。以下串聯電阻可降低電流,如Vishay SMBJ5.0CD(5 V VRWM)。為了進一步減少對受保護IC內部保護電路的影響,工程師可以在第二個TVS器件和IC之間放置另一個串聯電阻。

圖6 :工程師可以通過使用額外的TVS設備來減輕非常大的瞬態電壓浪涌的影響,其中主設備向次級設備提供減少的浪涌以進一步抑制。插入的串聯電阻減小了到達次級設備的電流,并最終降低了負載。 (由Vishay提供)

結論

隨著行業越來越傾向于低壓設計,沒有瞬態電壓浪涌保護的電路面臨性能下降甚至永久性損壞的威脅。 TVS器件具有廣泛的性能特征,可為保護這些敏感設計提供經濟高效的解決方案。通過在設計階段早期安裝TVS器件,工程師可以提供更強大的設計,能夠承受瞬態電壓浪涌的影響。

-

電源

+關注

關注

184文章

17718瀏覽量

250174 -

ESD

+關注

關注

49文章

2031瀏覽量

172995 -

能量采集

+關注

關注

4文章

83瀏覽量

25086

發布評論請先 登錄

相關推薦

接口電路的浪涌沖擊防護和應用TVS的解決方案

介紹能量收集、能量儲存和電源管理解決方案的優點、構建以及發展趨勢

能量采集技術難點和管理方案及應用

計算寬輸入電壓解決方案的價值

能量采集功率轉換的新進展

斷電保持能源存儲解決方案

計算寬輸入電壓解決方案

【NH2D0245】用于低功耗應用的高性能能量采集解決方案

Linear推出完整的能量采集解決方案 LTC3588-1

凌力爾特推出完整的能量采集解決方案,優化低壓能源

能量采集是物聯網解決方案實現完全自主的關鍵因素

信號防浪涌裝置的類型及應用解決方案

能量采集設計中破壞電壓浪涌的解決方案

能量采集設計中破壞電壓浪涌的解決方案

評論