通用微控制器中的休眠模式和空閑模式使嵌入式處理器能夠降低實時能耗,并解決許多電池和低功耗設計問題。然而,隨著嵌入式系統(tǒng)變得越來越復雜,實現(xiàn)更密集,更復雜的微核以及我們期望在今天看到的更高端外設需要額外的邏輯。因此,即使在待機模式下,在嘗試降低能量時靜態(tài)功耗也是一個問題,尤其是在需要長時間睡眠時。

降低能量和延長運行時間的一個因素是工作電壓。雖然許多5 V系統(tǒng)仍在使用和支持,但目前大多數(shù)設計已遷移到3.3,2.5和1.8 V競技場。由于電壓與功耗成正比,您可以看到靜態(tài)5 V系統(tǒng)的功率幾乎是1.8 V系統(tǒng)的三倍。開關電路的情況更是如此,因為功率消耗也與開關頻率成比例。

本文探討了8位微控制器,它具有更簡單的架構和低于平均值的電壓核心,可以在1.8 V以下工作。雖然這些電平可能無法與大多數(shù)外部設備配合使用,但它確實可以實現(xiàn)更低功耗,長期睡眠/休眠模式可以將電池壽命延長到極限。當電池接近完全放電狀態(tài)時,它還允許微型電池保持更長時間。

架構辯論

精心設計的核心與外圍設備專門用于減少能源使用可以對您的設計產(chǎn)生重大影響。您使用的是通用微型機還是選擇了其中一種低功耗架構設備?有一些巧妙設計的8至32位微處理器,具有令人印象深刻的低能耗模式。

對于總線寬度參數(shù)的雙方都可以進行很好的辯論。一方面,您可以說更大的32位架構可以更快地處理。正因為如此,更廣泛的架構不需要保持清醒,并且最終可以節(jié)省電力(即使它保持更廣泛的架構)。

另一方面,較窄的架構,如8位機器,可以完成所需的所有處理,雖然需要更長時間,但在靜態(tài)狀態(tài)下將以更低的功耗睡眠。寄存器,存儲器,指針等等,總線寬度都較窄,這意味著靜態(tài)功耗較小。當你看一些具有豐富外設和功能,混合信號功能和大量I/O的低壓8位器件時,這場辯論會變得很有趣。一個完美的例子來自ROHM及其Lapis系列ML610低功耗處理器。

雖然在某些方面相對較少,但這些具有低壓內(nèi)核的部件具有令人欽佩的外設和口味組合,包括一些典型配置,如120引腳TQFP ML610Q422P,32K閃存和2K RAM以及144-引腳LQFP ML610Q431具有64 K閃存和3K RAM。

ROHM系列由高性能CMOS 8位微控制器組成,內(nèi)置Lapis Semiconductor的原始RISC 8位CPU“U8核心”。 CPU內(nèi)核能夠通過每個周期時鐘操作一個指令執(zhí)行高效的指令。 “610”系列產(chǎn)品廣泛應用于各種領域的電池驅(qū)動,手持式應用。

請注意,這些部件不能以高兆赫時鐘運行。它們通過以低頻(通常為4 MHz)運行處理器并使用RISC內(nèi)核執(zhí)行244μs的大多數(shù)指令來節(jié)省功耗。與其他低能耗處理器一樣,這些處理器也可以使用實時時鐘的32.768 kHz進行操作。雖然較慢(每個指令周期為30.5μs),但它們可以相應地消耗更少的電流。

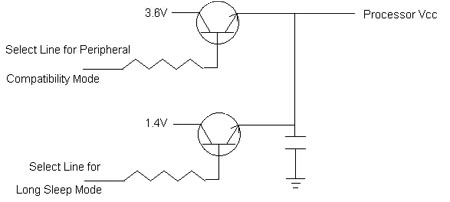

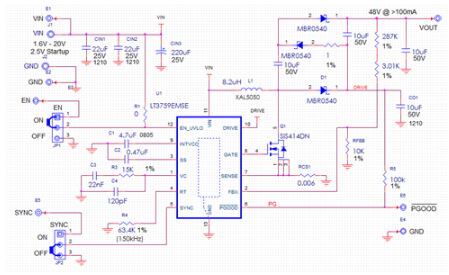

關鍵是這些內(nèi)核具有低至1.1 V的保證工作范圍。這允許一些巧妙的自適應電源設計技術,特別是如果您的處理器將要關閉并長時間休眠。例如,當通過串行端口或標準3.3 V外設與外部接口時,I/O線可以使用I/O驅(qū)動晶體管或偏置D/A電平將VCC設置為3.3 V(圖1)。如果沒有低功耗模式,外圍芯片可以以相同的方式上電和下電。當不需要外部活動時,VCC可以設置為1.8甚至1.1 V.這種動態(tài)電源電壓方法可以應用于任何可以在1.8 V閾值以下可靠工作的內(nèi)核。

圖1:對于沒有單獨I/O VCC控制的處理器,處理器VCC線的動態(tài)控制使其能夠與需要標準電壓的外部外設保持兼容,然后將自身置于低電壓模式,以便在長時間休眠期間節(jié)省功耗周期。實際電壓電平將根據(jù)所用晶體管的正向壓降或RDS(on)而變化。

除了基本的UART,I2C和SPI連接外,還提供各種高端選項,如LCD接口,與GPIO接口的外部總線以及其他不常用的外設,如旋律發(fā)生器。對于低功率分布式傳感器應用特別感興趣的是這些部件包含兩個16位A/D轉(zhuǎn)換器和24位D/A轉(zhuǎn)換器。

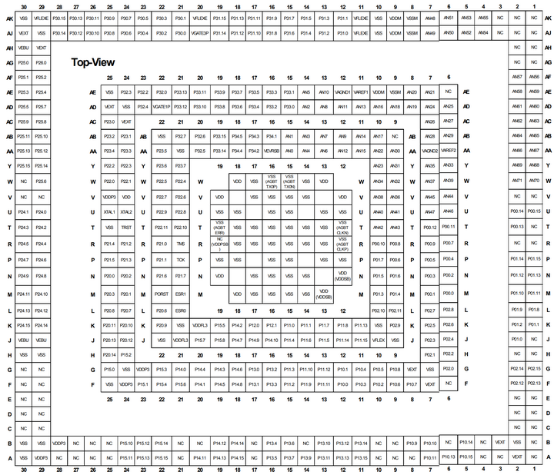

ROHM ML610QX演示板使用插入式子板容納各個ML610系列成員(圖2)。主板包含一個LCD,串行端口,按鈕和一個發(fā)聲器,可幫助測試基本編碼和設計。 UEASE W/COMPILER也可用于編譯器和仿真器/調(diào)試支持。 Rohm還在Digi-Key網(wǎng)站上提供了有關其低功耗微型和A/D使用的產(chǎn)品培訓模塊。

圖2:由于Lapis系列中有如此多的系列成員,開發(fā)系統(tǒng)使用子板來設計每個部件自身的外圍設備和功能組合。

另一個有趣的部分來自意法半導體;他們的STM8L101G2U6A工作電壓低至1.62 V.該器件是ST的EnergyLite系列之一,具有高達68個I/O和高達64 K的閃存和8K的RAM。 8位內(nèi)核基于CISC架構,內(nèi)部采用16 MHz R/C振蕩器,在Halt模式下吸收300 nA,在Active-Halt模式下吸收800 nA(保留所有內(nèi)部構件)。

這些不是超快速,超密集的部件,但它們并不打算打破任何速度記錄。支持的外設類似于針對低功耗設計的其他處理器,具有SPI,IIC和UART等基本功能。這些器件針對成本敏感的低功耗應用,可以使用ST的STM8L15LPBOARD進行應用測試和開發(fā),支持該公司的STM8L EnergyLite處理器(圖3)。開發(fā)板的原理圖1也可用,這些處理器由Segger Flasher系列生產(chǎn)工具提供支持。

圖3:支持ST的低壓內(nèi)核包括一個低功耗演示/開發(fā)板,具有基本的通用通信和外設以及所有模式下的電流消耗測量。

這里應該注意的是,雖然功耗可以達到1.62 V與1.8 V沒有顯著差異,但它確實意味著處理器可以在電池或超級電容器放電時運行更長時間,特別是在低頻運行時。

低至0.5 V

眾多先進的8051內(nèi)核中的一款產(chǎn)品來自賽普拉斯,其CY8C32xx系列可編程系統(tǒng)芯片3(PSoC3)。這是一系列系統(tǒng)級芯片,在單芯片上集成了模擬,數(shù)字,外設,存儲器和CPU。

與其他高度精煉的8051內(nèi)核一樣,PSoC3基于熟悉的架構,具有現(xiàn)代單周期速度(本例中為50 MHz)和高端外設(如LCD,DMA,USB 2.0和Touch Sense),以及超越任何遺留部分。在這種情況下,一個特別突出。

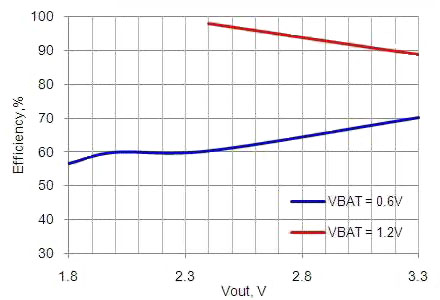

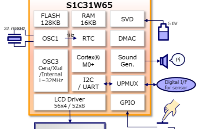

雖然額定運行的最低電壓為1.71 V,但這些器件實際上可以在低至0.5 V的電壓下運行(是的,您可以正確讀取)。內(nèi)部高效升壓調(diào)節(jié)器將低輸入電壓(0.5至1.8 V)升壓至5 V,為片上系統(tǒng)及其外設供電(圖4)。

圖4:內(nèi)部升壓調(diào)節(jié)器在極低電壓下會失效,但會為PSoC的VCC提供低至0.5 V的輸入電壓。

還支持混合信號功能。這些器件有兩個12位A/D轉(zhuǎn)換器。具有8位分辨率的D/A可能會受到限制,但有大量I/O(最多62個)和外圍總線(包括IIC,SPI,UART,LIN和USB) - 用于掛起外部D/A.另一個不錯的功能是它的片上EEPROM(高達2K x 8),可以在軟件控制下寫入非易失性參數(shù)。

典型的中間示例是100引腳LQFP CY8C3245,具有32K閃存,1K RAM和1K EEPROM。該器件具有大量I/O(62),可以實現(xiàn)外部總線接口以擴展存儲器范圍或添加并行外設。

總結(jié)

低功耗和能量敏感設計可以通過降低核心電壓來降低實時功耗。一些制造商意識到這一點并通過提供在其他人耗盡電池時仍能運行的部件來滿足需求。雖然8位器件可以從這種方法中受益,但工程師們不應忽視這樣一個事實,即16位和32位低壓內(nèi)核也提供自己的省電技術。因此,在為下一個項目選擇MCU時要保持開放的態(tài)度。

-

微控制器

+關注

關注

48文章

7576瀏覽量

151727 -

處理器

+關注

關注

68文章

19382瀏覽量

230484 -

嵌入式

+關注

關注

5087文章

19153瀏覽量

306432

發(fā)布評論請先 登錄

相關推薦

ATMEGA168-20AI高性能、低功耗AVR 8位微控制器

ATXMEGA128A4U-AU港定ATMEL原廠原裝8位MCU微控制器

微控制器監(jiān)控器集成電路中的故障保護分析

8位單片微控制器XC866

AT25DF081 1.8V電壓8Mb Serial Fla

低電壓下工作的LED閃爍器原理

富士通推出3個系列18款內(nèi)置閃存、可低壓下工作的8位MCU

單電池微控制器工作的優(yōu)點

新唐科技Arm? Cortex?-M0 微控制器家族(之三)

LT3759 DC/DC控制器可在低至1.6V的電壓下工作

可以在1.8V電壓下工作的8位微控制器的性能分析

可以在1.8V電壓下工作的8位微控制器的性能分析

評論