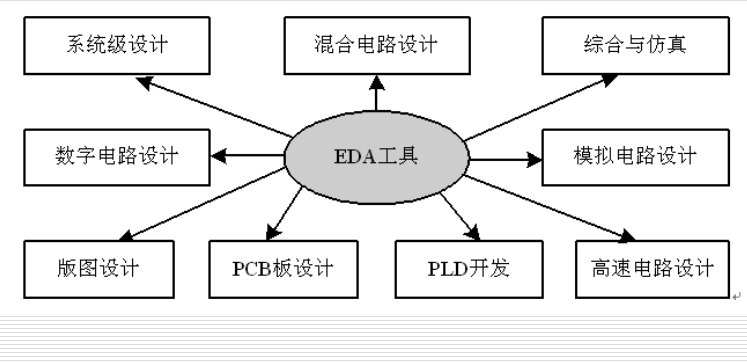

EDA技術是在電子CAD技術基礎上發展起來的計算機軟件系統,是指以計算機為工作平臺,融合了應用電子技術、計算機技術、信息處理及智能化技術的 最新成果,進行電子產品的自動設計。利用EDA工具,可以將電子產品從電路設計、性能分析到設計出IC版圖或PCB版圖的整個過程在計算機上自動處理完 成。

EDA常用軟件EDA 工具層出不窮,目前進入我國并具有廣泛影響的EDA軟件有:EWB、PSPICE、OrCAD、PCAD、Protel、ViewLogic、 Mentor、Graphics、Synopsys、LSIlogic、Cadence、MicroSim等等。按主要功能或主要應用場合,可分為電路設 計與仿真工具、PCB設計軟件、IC設計軟件、PLD設計工具及其它EDA軟件。

電子電路設計與仿真工具電子電路設計與仿真工具包括SPICE/PSPICE;EWB;Matlab;SystemView;MMICAD等。下面簡單介紹前三個軟件。(1)SPICE: 由美國加州大學推出的電路分析仿真軟件,現在用得較多的是PSPICE6.2,在同類產品中是功能最為強大的模擬和數字電路混合仿真 EDA軟件,它可以進行各種各樣的電路仿真、激勵建立、溫度與噪聲分析、模擬控制、波形輸出、數據輸出、并在同一窗口內同時顯示模擬與數字的仿真結果。無 論對哪種器件哪些電路進行仿真,都可以得到精確的仿真結果,并可以自行建立元器件及元器件庫。(2)EWB軟件:20世紀90年代初推出 的電路仿真軟件。相對于其它EDA軟件,它是較小巧的軟件(只有16M)。但它對模數電路的混合仿真功能卻十分強大,幾乎100%地仿真出真實電路的結 果,并且它在桌面上提供了萬用表、示波器、信號發生器、掃頻儀、邏輯分析儀、數字信號發生器、邏輯轉換器和電壓表、電流表等儀器儀表。它的界面直觀,易學 易用。它的很多功能模仿了SPICE的設計,但分析功能比PSPICE稍少一些。(3)文字MATLAB產品族它們的一大特性是有眾多的面向具體應用的工具箱和仿真塊,包含了完整的函數集用來對圖像信號處理、控制系統設計、神經網絡等特殊應用進行分析和設計。它具有數據采集、報告生成和MATLAB語言編程產生獨立C/C++代碼等功能。PCB設計軟件PCB(Printed—Circuit Board)設計軟件種類很多,如Protel;OrCAD;Viewlogic;PowerPCB; Cadence PSD;MentorGraphices的Expedition PCB;Zuken CadStart;Winboard/Windraft/Ivex-SPICE;PCB Studio; TANGO等等。其中Protel是個完整的全方位電路設計系統,包含了電原理圖繪制、模擬電路與數字電路混合信號仿真、多層印刷電路板設計(包含印刷電 路板自動布局布線),可編程邏輯器件設計、圖表生成、電路表格生成、支持宏操作等功能,并具有Client/Server(客戶/服務器體系結構,同時還 兼容一些其它設計軟件的文件格式,如ORCAD、PSPICE、EXCEL等。

IC設計軟件IC設計工具很多,其中按市場所占份額排行為Cadence、Mentor Graphics和Synopsys。(1) 設計輸入工具:像Cadence的composer,viewlogic的viewdraw,硬件描述語言VHDL、Verilog HDL是主要設計語言,許多設計輸入工具都支持HDL。另外像Active—HDL和其它的設計輸入方法,包括原理和狀態機輸入方法,設計 FPGA/CPLD的工具大都可作為IC設計的輸入手段,如Xilinx、Altera等公司提供的開發工具,Modelsim FPGA等。(2) 設計仿真工作:EDA工具的一個最大好處是可以驗證設計是否正確,幾乎每個公司的EDA 產品都有仿真工具。Verilog—XL、NC—verilog用于Verilog仿真,Leapfrog 用于VHDL仿真,Analog Artist用于模擬電路仿真。Viewlogic的仿真器有:viewsim門級電路仿真器,speedwaveVHDL仿真器,VCS— verilog仿真器。Mentor Graphics有其子公司Model Tech 出品的VHDL和Verilog雙仿真器:Model Sim。Cadence、Synopsys用的是VSS(VHDL仿真器)。現在的趨勢是各大EDA公司都逐漸用HDL仿真器作為電路驗證的工具。(3)綜合工具綜 合工具可以把HDL變成門級網表。這方面Synopsys工具占有較大的優勢,它的Design Compile是作綜合的工業標準,它還有另外一個產品叫Behavior Compiler,可以提供更高級的綜合。另外最近美國又出了一家軟件叫Ambit,說是比Synopsys的軟件更有效,可以綜合50萬門的電路,速度 更快。今年初Ambit被Cadence公司收購,為此Cadence放棄了它原來的綜合軟件Synergy。隨著FPGA設計的規模越來越大,各EDA 公司又開發了用于FPGA設計的綜合軟件,比較有名的有:Synopsys的FPGA Express,Cadence的Synplity,Mentor的Leonardo,這三家的FPGA綜合軟件占了市場的絕大部分。(4)布局和布線在 IC設計的布局布線工具中,Cadence軟件是比較強的,它有很多產品,用于標準單元、門陣列已可實現交互布線。最有名的是Cadence spectra,它原來是用于PCB布線的,后來Cadence把它用來作IC的布線。其主要工具有:Cell3,Silicon Ensemble—標準單元布線器;Gate Ensemble—門陣列布線器;Design Planner—布局工具。其它各EDA軟件開發公司也提供各自的布局布線工具。(5)物理驗證工具物理驗證工具包括版圖設計工具、版圖驗證工具、版圖提取工具等等。這方面Cadence也是很強的,其Dracula、Virtuso、Vampire等物理工具有很多的使用者。(6)模擬電路仿真器前 面講的仿真器主要是針對數字電路的,對于模擬電路的仿真工具,普遍使用SPICE,這是唯一的選擇。只不過是選擇不同公司的 SPICE,像MiceoSim的PSPICE、Meta Soft的HSPICE等等。HSPICE現在被Avanti公司收購了。在眾多的SPICE中,最好最準的當數HSPICE,作為IC設計,它的模型最 多,仿真的精度也最高。

PLD設計工具PLD(Programmable Logic Device)是一種由用戶根據需要而自行構造邏輯功能的數字集成電路。目前主要有兩大類型:CPLD(Complex PLD)和FPGA(Field Programmable Gate Array)。它們的基本設計方法是借助于EDA軟件,用原理圖、狀態機、布爾表達式、硬件描述語言等方法,生成相應的目標文件,最后用編程器或下載電 纜,由目標器件實現。生產PLD的廠家很多,但最有代表性的PLD廠家為ALTERA、Xilinx和Lattice公司。PLD的開發工具一般由器件生產廠家提供,但隨著器件規模的不斷增加,軟件的復雜性也隨之提高,目前由專門的軟件公司與器件生產廠家合作,推出功能強大的設計軟件。PLD(可 編程邏輯器件)是一種可以完全替代74系列及GAL、PLA的新型電路,只要有數字電路基礎,會使用計算機,就可以進行PLD的開發。 PLD的在線編程能力和強大的開發軟件,使工程師可以在幾天,甚至幾分鐘內就可完成以往幾周才能完成的工作,并可將數百萬門的復雜設計集成在一顆芯片內。 PLD技術在發達國家已成為電子工程師必備的技術。PLD生產及開發工具:(1)ALTERA 20世紀90年代以后發展很快。主要產品有:MAX3000/7000、FELX6K/10K、APEX20K、ACEX1K、Stratix等。其開發 工具—MAX+PLUS II是較成功的PLD開發平臺,最新又推出了Quartus II開發軟件。Altera公司提供較多形式的設計輸入手段,綁定第三方VHDL綜合工具,如:綜合軟件FPGA Express、Leonard Spectrum,仿真軟件ModelSim。(2)ILINX FPGA的發明者。產品種類較全,主要有;XC9500/4000、Coolrunner(XPLA3)、Spartan、Vertex等系列,其最大的 Vertex—II Pro器件已達到800萬門。開發軟件為Foundation和ISE。通常來說,在歐洲用Xilinx的人多,在***和亞太地區用ALTERA的人 多,在美國則是平分秋色。全球PLD/FPGA產品60%以上是由Altera和Xilinx提供的。可以講Altera和Xilinx共同決定了PLD 技術的發展方向。(3)Lattice—Vantis Lattice是ISP(In—System Programmability)技術的發明者,ISP技術極大地促進了PLD產品的發展,與ALTERA和XILINX相比,其開發工具比Altera 和Xilinx略遜一籌。中小規模PLD比較有特色,大規模PLD的競爭力還不夠強(Lattice沒有基于查找表技術的大規模FPGA),1999年推 出可編程模擬器件,1999年收購Vantis(原AMD子公司),成為第三大可編程邏輯器件供應商。2001年12月收購Agere公司(原 Lucent微電子部)的FPGA部門。主要產品有ispLSI2000/5000/8000,MACH4/5。(4)ACTEL 反熔絲(一次性燒寫)PLD的領導得,由于反熔絲PLD抗輻射、耐高低溫、功耗低、速度快,所以在軍品和宇航級上有較大優勢。ALTERA和XILINX則一般不涉足軍品和宇航級市場。(5)Quicklogic專業PLD/FPGA公司,以一次性反熔絲工藝為主,在中國地區銷售量不大。(6)Lucent 主要特點是有不少用于通訊領域的專用IP核,但PLD/FPGA不是Lucent的主要業務,在中國地區使用的人很少。(7)ATMEL 中小規模PLD做得不錯。ATMEL也做了一些與Altera和Xilinx兼容的片子,但在品質上與原廠家還是有一些差距,在高可*性產品中使用較少,多用在低端產品上。(8)Clear Logic 生產與一些著名PLD/FPGA大公司兼容的芯片,這種芯片可將用戶的設計一次性固化,不可編程,批量生產時的成本較低。(9)WSI 生產PSD(單片機可編程外圍芯片)產品。這是一種特殊的PLD,如最新的PSD8xx、PSD9xx集成了PLD、EPROM、Flash,并支持ISP(在線編程),集成度高,主要用于配合單片機工作。

其它EDA軟件(1)VHDL 語言超高速集成電路硬件描述語言(VHSIC Hardware DeseriptionLanguagt,簡稱VHDL),是IEEE的一項標準設計語言。它源于美國國防部提出的超高速集成電路(Very High Speed Integrated Circuit,簡稱VHSIC)計劃,是ASIC設計和PLD設計的一種主要輸入工具。(2)Veriolg HDL 是Verilog公司推出的硬件描述語言,在ASIC設計方面與VHDL語言平分秋色。(3)其它EDA軟件如專門用于微波電路設計和電力載波工具、PCB制作和工藝流程控制等領域的工具,在此就不作介紹了。saber軟件簡介,我主要應用于開關電源的仿真。Saber 是混合信號、混合技術設計與驗證工具,在電力電子、數模混合仿真、汽車電子及機電一體化領域得到廣泛應用。Saber軟件在技術、理論及新產品開發方面保 持明顯優勢,其大量的器件模型、先進的仿真技術和精確的建模工具為客戶提供了全面的系統解決方案,在并在技術方面不斷地完善創新。Saber 的建模工具運用廣泛,有可用于電源、機電、磁、熱、負載等各種建模工具。Saber也有獨特的設計與驗證方法:“自頂向下”(Top- Down Design)設計與“自下而上”(Bottom-Up)仿真驗證方法。在作了建模方法演示、混合技術設計方法演示、線纜設計(從電氣設計到線纜生產)流 程演示后,Johnson演示了單故障模式仿真調試;關鍵參數與非關鍵參數的多故障模式仿真調試,顯示了Saber仿真器Testify的強大功能。Saber的典型案例是航空器領域的系統設計,其整個設計過程包含了機械技術、電子技術、液壓技術、燃油系統、娛樂系統、雷達無線技術等復雜的混合技術設計與仿真。從航空器、輪船、汽車到消費電子、電源設計都可以通過Saber來完成。在開關電源設計中,如果有變壓器,saber仿真是最好的,變壓器模型比較全。saber仿真現在主要問題就是沒有教材。不方便學習。

-

pcb

+關注

關注

4319文章

23099瀏覽量

397889 -

半導體

+關注

關注

334文章

27363瀏覽量

218712 -

eda

+關注

關注

71文章

2759瀏覽量

173268 -

PLD

+關注

關注

6文章

224瀏覽量

59399

原文標題:精華 | 這些半導體設計工具匯總,你都認識嗎?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常用半導體手冊

常用半導體器件型號命名法

常用的軟件測試工具有哪些_10款常用的軟件測試工具推薦

EDA技術實用教程之EDA技術概述數字設計的流程及常用的EDA軟件工具介紹

常用半導體設計EDA軟件工具匯總說明

常用半導體設計EDA軟件工具匯總說明

評論