全球?qū)?a target="_blank">通信服務(wù)的需求持續(xù)增長,制造商必須不斷降低新安裝的網(wǎng)絡(luò)設(shè)備的規(guī)模和成本,同時堅持高標(biāo)準(zhǔn)的服務(wù)和質(zhì)量。構(gòu)建強大網(wǎng)絡(luò)的一部分是管理時鐘。時鐘和時序要求包括有線和無線網(wǎng)絡(luò)集線器的系統(tǒng)級同步,以及高密度收發(fā)器機柜內(nèi)的本地信號分配。為了應(yīng)對這一系列廣泛的設(shè)計挑戰(zhàn),公司聘請信號完整性專家來解釋規(guī)范,監(jiān)督測試,并推薦保證在整個網(wǎng)絡(luò)中保持干凈,低抖動時鐘的組件。

詢問任何信號完整性專家的時間抖動,他/她可能會概述分布式組件所帶來的挑戰(zhàn),這些挑戰(zhàn)一個接一個地影響系統(tǒng)的總抖動預(yù)算。時鐘上的時間抖動是邊緣不確定性的度量。所有系統(tǒng)都可以容忍一些時鐘邊沿不確定性。但是當(dāng)時鐘邊緣越來越隨機時出現(xiàn)時,系統(tǒng)開始崩潰。缺少一個時鐘周期可能導(dǎo)致發(fā)送器和接收器失去同步。

當(dāng)時間抖動限制系統(tǒng)的總體信噪比或誤碼率時,數(shù)據(jù)可能會丟失。在移動網(wǎng)絡(luò)中,這可能會降低通話質(zhì)量,甚至掉線。

考慮一個需要串聯(lián)四個時鐘功能的系統(tǒng):倍頻,分頻,相位偏移和電平轉(zhuǎn)換。如果每個功能由單獨的組件執(zhí)行,則必須在數(shù)學(xué)上組合每個設(shè)備的時間抖動以計算總時鐘路徑抖動。四個級聯(lián)組件,每個具有1.5皮秒(ps)rms的抖動規(guī)格,產(chǎn)生3 ps rms的總抖動(注意:平方和方法的平方根適用)。

因此,完整的時鐘路徑具有兩倍于各個組件的抖動。

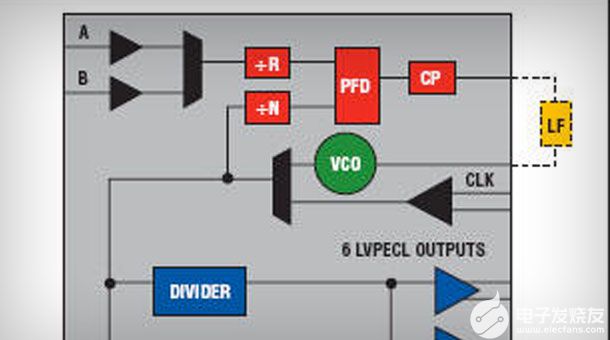

現(xiàn)在將其與所有關(guān)鍵時序功能集成到單個器件中的解決方案進行比較 - 一個完整的鎖相環(huán)(PLL),包括電壓控制用于倍頻的振蕩器(VCO),具有內(nèi)置相位偏移功能的五通道分頻器,以及提供LVPECL,LVDS或CMOS電平選擇的時鐘輸出驅(qū)動器。采用集成方法,可將總時鐘路徑抖動控制在遠低于1 ps rms。

ADI公司的AD9516集成2.8 GHz時鐘發(fā)生器,具有14通道分配,使網(wǎng)絡(luò)設(shè)計人員能夠產(chǎn)生14個干凈,低抖動單芯片時鐘。此外,AD9516在其六個LVPECL輸出之間提供低時間偏移。這種能力意味著設(shè)計人員可以確保所有六個時鐘邊沿都出現(xiàn)在明確定義的時間窗內(nèi)。 LVDS / CMOS通道包括可編程延遲線,可用于補償系統(tǒng)其他部分的延遲。兩個輸入-A和B-功能自動切換,在參考時鐘故障時提供保護。最后,由于獨立振蕩器是網(wǎng)絡(luò)中最可能出現(xiàn)故障的組件之一,因此AD9516通過在片上集成VCO來提高整體系統(tǒng)可靠性。

ADI公司提供各種時鐘和定時解決方案,使信號完整性工程師能夠在降低新設(shè)備尺寸和成本的同時保持性能。有關(guān)數(shù)據(jù)表,免費樣品和更多信息,請訪問www.analog.com/clock-timing/AD9516。

-

芯片

+關(guān)注

關(guān)注

456文章

51157瀏覽量

426673 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1368瀏覽量

61819

發(fā)布評論請先 登錄

相關(guān)推薦

如何在ML507板上使用時鐘發(fā)生器芯片IDT5V9885?

基于有線的時鐘發(fā)生器和分配器技術(shù)注意事項

AD9523時鐘發(fā)生器的性能特點及應(yīng)用分析

如何選擇合適的時鐘發(fā)生器

AD9575:網(wǎng)絡(luò)時鐘發(fā)生器,雙輸出數(shù)據(jù)表

AD9531:3通道時鐘發(fā)生器,24輸出數(shù)據(jù)表

超低抖動時鐘發(fā)生器和分配器最大限度地提高數(shù)據(jù)轉(zhuǎn)換器的信噪比

AD9516-3:14輸出時鐘發(fā)生器,集成2.0 GHz壓控振蕩器數(shù)據(jù)表

Cypress時鐘發(fā)生器的分類,它有哪些應(yīng)用

具有14通道分配功能的單芯片時鐘發(fā)生器解決了網(wǎng)絡(luò)中的時序挑戰(zhàn)

CDCE62005高性能時鐘發(fā)生器和分配器數(shù)據(jù)表

14通道分配的單芯片時鐘發(fā)生器解決了網(wǎng)絡(luò)中的時序挑戰(zhàn)等難題

14通道分配的單芯片時鐘發(fā)生器解決了網(wǎng)絡(luò)中的時序挑戰(zhàn)等難題

評論