隨著移動電話架構的發展,其功耗和成本降低,同時其效率和性能也有所提高。同時,為這些手機提供服務的無線基站也在努力跟上這些改進。超過一半的現代基站的功耗與功率放大器相關聯,因此正在進行持續的系統級努力以提高其能效。在GSM,EDGE和W-CDMA系統中發現的時分多址(TDMA)架構必須能夠在規定的功率限制與時間內上下調整其功率包絡。如果不能最佳地管理臨界斜坡時序,則可能會在發送時隙上丟失信息,或者在接收時隙期間可能會發生干擾。

高速電流輸出DAC可用于單運算放大器可生成符合TDMA RF增益要求的PA斜坡曲線。斜坡應用于可變增益放大器(VGA)的電壓控制引腳,以控制進入PA的RF信號的增益,如圖1所示。指定偏移,上升時間,下降時間,幅度曲線和周期信息允許DAC曲線擬合所需的斜坡。該配置文件信息可以存儲在微處理器的控制邏輯中。

對于每種調制方案而言不同的斜坡形狀取決于所使用的PA。配置文件可以從簡單的斜坡余弦類型波形到更復雜的任意波形。使用電流輸出DAC和合適的高速運算放大器的優勢在于它可以精確復制“慢速”和“快速”斜坡曲線。在斜坡控制應用中,DAC的關鍵要求是快速建立時間。眾多電壓輸出DAC將輕松達到規定的精度,但電流輸出DAC與高速運算放大器相結合仍然是低于100 ns范圍內建立時間的最佳選擇。只要從寬帶低阻抗源(如參考電壓)驅動DAC,DAC就會快速穩定下來。因此,電流輸出DAC的壓擺率和建立時間主要由運算放大器決定。決定運算放大器交流性能的規格包括輸入電容 - 必須保持最小 - 以及小信號帶寬。請注意,DAC的反饋電阻大約為10kΩ,是運算放大器驅動的重要負載,并在確定電路帶寬時設置主導極點。

這帶來了另一個優勢選擇運算放大器和電流輸出DAC的組合來產生斜坡控制電壓:運算放大器可以定制,以最好地滿足電路設計需求,其中噪聲,建立時間和功率要求都可以考慮在內。利用電壓輸出DAC中的內部運算放大器,可以提高帶寬精度,但使用外部運算放大器可以找到適合應用的最佳解決方案。運算放大器的帶寬通常與其直流精度成反比關系。有助于DAC精度的兩個規格是輸入偏置電流和輸入失調電壓。因此,選擇具有足夠帶寬的運算放大器以實現所需的斜坡性能,同時仍保持良好的直流精度非常重要。選擇帶寬過大的運算放大器通常會導致直流性能下降。

在實現所需的建立時間時要考慮的一個重要因素是補償電容。 DAC的輸出電容在開環響應中引入極點,這可能導致閉環斜坡分析電路中的振鈴或不穩定。為了補償這一點,外部反饋電容CF與DAC的內部反饋電阻并聯。值太小會在輸出端產生振鈴,而值太大會增加建立時間。 DAC的輸出電容隨代碼而變化,因此無法確定CF的精確值。

AD5450 / AD5451 / AD5452 / AD5453系列DAC提供8- / 10- / 12- / 14針對此應用的位精確電流輸出解決方案。圖1顯示了一個AD5453 DAC,配置為單極性輸出,并配有定制的高速緩沖器,以最好地適應系統性能。該器件的建立時間約為100 ns,帶寬為12 MHz,是波形發生應用的理想選擇。圖2顯示了通用斜坡配置文件的示例。放大的圖顯示DAC在下一個數據模式寫入SPI接口之前穩定下來。

-

放大器

+關注

關注

143文章

13627瀏覽量

214086 -

dac

+關注

關注

43文章

2309瀏覽量

191476 -

功率

+關注

關注

14文章

2072瀏覽量

70036

發布評論請先 登錄

相關推薦

Aigtek:功率放大器分類怎么分的

Aigtek功率放大器有哪些特性

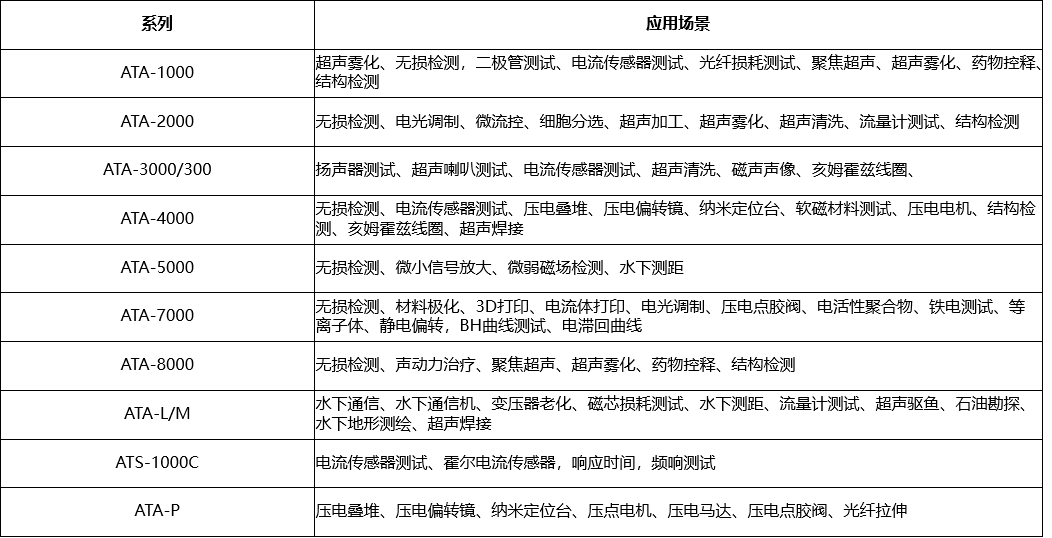

Aigtek功率放大器應用領域指南(功率放大器應用場景介紹)

安泰功率放大器在什么器件上使用

安泰功率放大器參數怎么選型號

安泰功率放大器怎么使用

安泰高壓功率放大器如何設計

高速DAC控制功率放大器的臨界斜坡時序管理

高速DAC控制功率放大器的臨界斜坡時序管理

評論