覆銅板

覆銅板-----又名基材。將補強材料浸以樹脂,一面或兩面覆以銅箔,經熱壓而成的一種板狀材料,稱為覆銅箔層壓板。它是做PCB的基本材料,常叫基材。當它用于多層板生產時,也叫芯板(CORE)。

覆銅板疊層結構

1、基板

高分子合成樹脂和增強材料組成的絕緣層壓板可以作為敷銅板的基板。合成樹脂的種類繁多,常用的有酚醛樹脂、環氧樹脂、聚四氟乙烯等。增強材料一般有紙質和布質兩種,它們決定了基板的機械性能,如耐浸焊性、抗彎強度等。

2、銅箔

它是制造敷銅板的關鍵材料,必須有較高的導電率及良好的焊接性。要求銅箔表面不得有劃痕、砂眼和皺褶,金屬純度不低于99.8%,厚度誤差不大于±5um。按照部頒標準規定,銅箔厚度的標稱系列為18、25、35、70和105um。我國目前正在逐步推廣使用35um厚度的銅箔。銅箔越薄,越容易蝕刻和鉆孔,特別適合于制造線路復雜的高密度的印制板。

3、覆銅板粘合劑

粘合劑是銅箔能否牢固地覆在基板上的重要因素。敷銅板的抗剝強度主要取決于粘合劑的性能。

-

基材

+關注

關注

1文章

19瀏覽量

9179 -

覆銅板

+關注

關注

9文章

265瀏覽量

26383 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

15630 -

華秋DFM

+關注

關注

20文章

3494瀏覽量

4595

發布評論請先 登錄

相關推薦

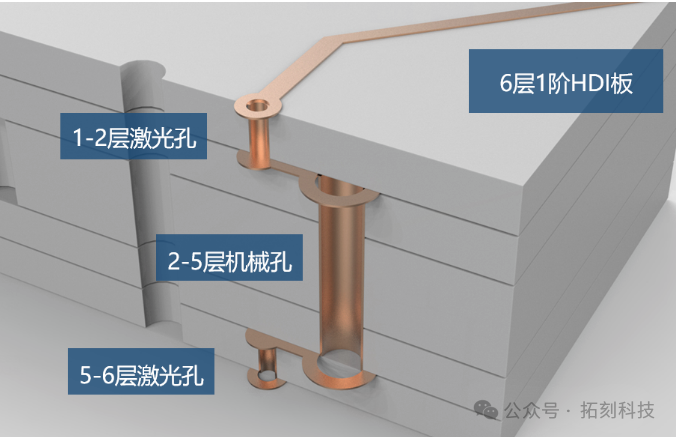

HDI的疊層結構設計

如何根據貼片疊層電感參數進行選型

晶科能源獲批浙江省先進疊層光伏技術重點實驗室認定

金屬基覆銅板中鋁基板材質你了解嗎

繞線電感和疊層電感的區別是什么

PCB多層板為什么都是偶數層?奇數層不行嗎?

5G時代下,無機填料氧化鋁導熱粉在覆銅板市場的發展趨勢與重要性

谷景揭秘貼片疊層電感精度是不是越高越好

設計制作PCB覆銅板的五種種常見方法

鈣鈦礦疊層電池:Topcon與HJT底電池性能對比研究

高頻高速覆銅板結構構成

PCB疊層設計優化ESD性能設計

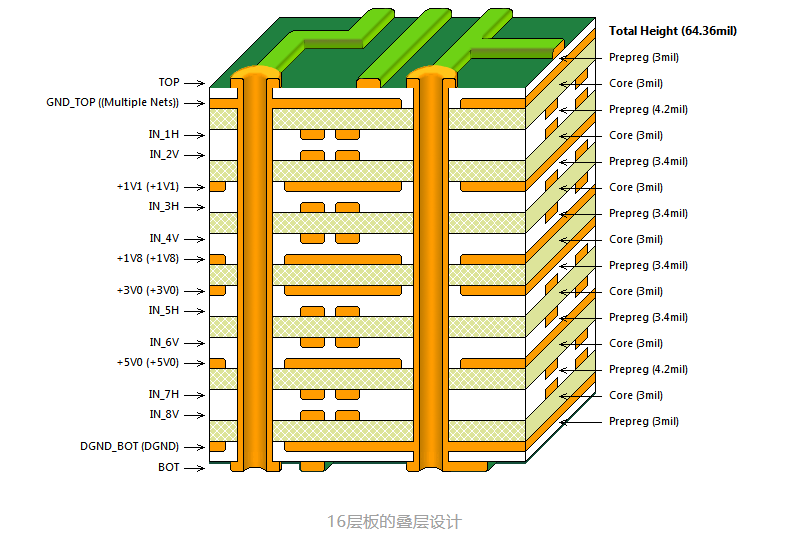

覆銅板疊層結構

覆銅板疊層結構

評論