3nm!昨天,在三星的代工論壇活動中,三星發布了其第一款3nm工藝的產品設計套件(PDK),旨在幫助客戶盡早開始設計工作,提高設計競爭力,同時縮短周轉時間(TAT)。

這一宣布的特別之處在于,3nm是三星打算推出下一代環繞柵極 Gate-All-Around(GAA)技術以取代FinFET的工藝節點。這個被稱為當前FinFET 技術進化版的生產技術,能夠對芯片核心的晶體管進行重新設計和改造,使其更小更快!

三星的3nm工藝節點采用的GAAFET晶體管是什么?

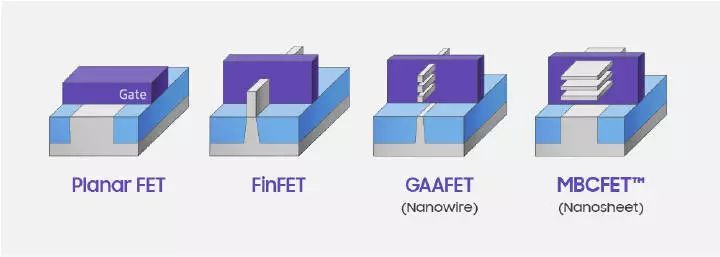

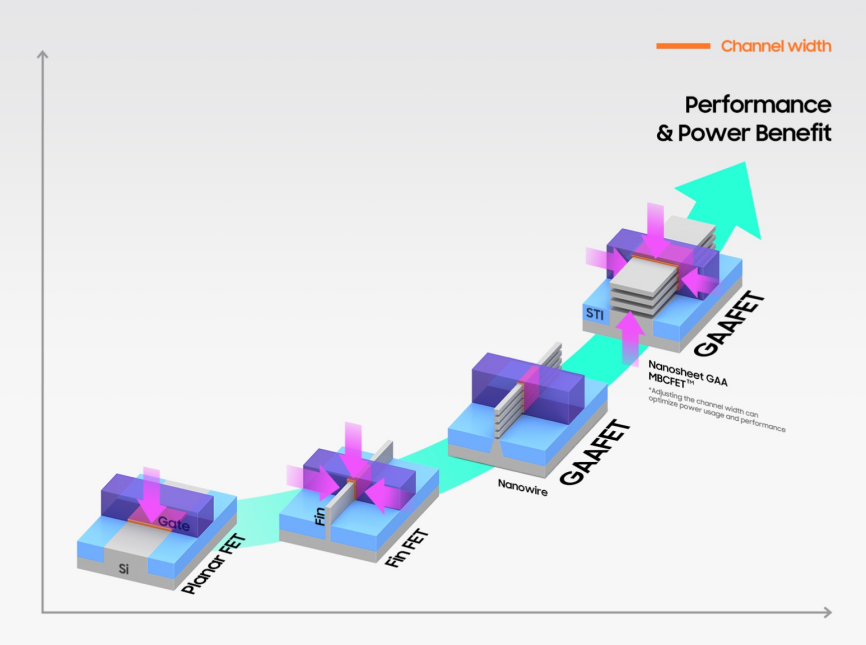

晶體管結構:過去(平面晶體管Planar FET)、現在(鰭式場效應晶體管FinFET)、未來(環繞柵極晶體管GAAFET)。

目前只有三星一家布局了GAAFET結構,應用于3nm,而三星在GAAFET獨創了優化后的版本MBCFET結構。

為了方便理解,介紹下晶體管的發展歷史故事梗概。

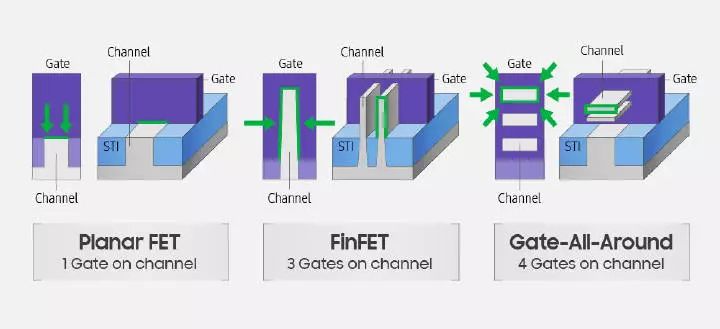

故事大概是這樣的:眾所周知,0和1生萬物,是信息世界(說現實世界也沒毛病)的“道”,而晶體管承載著將0101之類的數字信息轉換成電信號的半導體硬件。晶體管由“溝道”和“柵極”組成,其中電流在半導體的源極和漏極之間流動,“柵極”用于管理流過溝道的電流。 門通過放大電信號并且還用作開關來產生二進制系統數據。 因此,晶體管基本上是半導體芯片的基本元件。

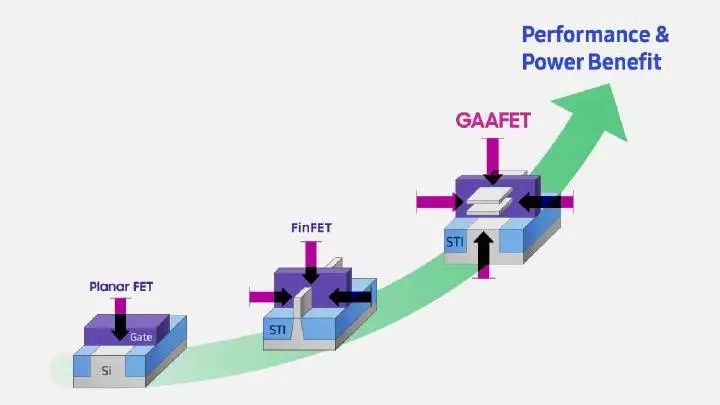

隨著晶體管變小,源極和漏極之間的距離變小,使得晶體管難以作為開關工作。 這被稱為“短溝道效應”,平面晶體管的設計停留在20nm節點。

為了克服短溝道效應,全耗盡晶體管成為下一代晶體管。 該晶體管使用薄硅(Si)溝道,通過增強柵極調整溝道的能力來避免短溝道效應。 其結構格式由傳統晶體管(平面溝道上的柵極)演變而來,變成薄而堅固的結構,具有與三個側面的門互鎖的直立矩形通道。 由于這個薄的站立通道有點像魚的背鰭,它也被稱為'鰭式晶體管'。

平面晶體管僅允許溝道和柵極僅在一個平面中接觸,但是鰭式晶體管具有三維結構,其允許溝道的三個側面(不包括其底部)與柵極接觸。 這種與柵極的增加的接觸改善了半導體性能并且增加了工作電壓的降低,解決了由短溝道效應引起的問題。

然而,在經過幾代開發和工藝轉換之后,鰭式晶體管現在也面臨著局限。 半導體工業越來越需要能夠進一步降低工作電壓的晶體管。 盡管鰭式晶體管的三維結構,四個側面中只有三個與柵極接觸現在正成為限制,所以FinFET晶體管也就只能支撐到4nm節點。

接下來怎么辦,按照剛才的思路,溝道和柵極的接觸面越多越好,那么如何讓它四個面都接觸呢,GAAFET應運而生,這個設計使得溝道的四個截面都和柵極接觸,360度環繞消除短溝道效應。

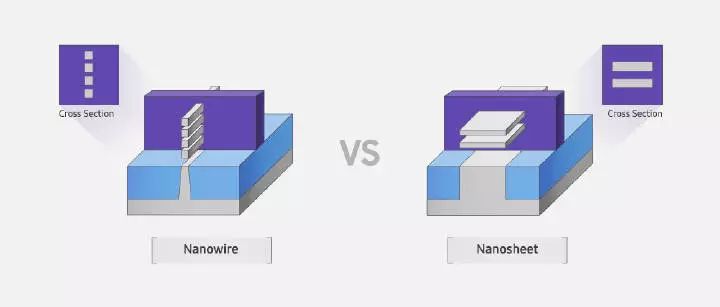

典型的GAA晶體管是納米柱,直徑太小才1nm,但是溝道需要盡可能寬允許大量電流通過,所以三星把這幾根納米柱改成面積大的納米片,被稱為MBCFET晶體管(多橋通道場效應晶體管),這是三星的專利設計,MBCFET?通過將線形通道結構與二維納米片對齊,增加了與柵極接觸的面積,從而實現更簡單的器件集成以及增加電流。 三星的MBCFET?是一種具有競爭力的晶體管結構,它不僅包括通過GAA結構減輕短溝道效應的手段,而且還通過擴展通道面積來提高性能。

與現有的7nm鰭式晶體管工藝技術相比,MBCFET?可將功耗降低50%,性能提高30%,并將晶體管占用面積減少45%。

GAA晶體管的發展,相當于半導體技術的工業革命,是一個艱難的過程,三星是目前唯一提供未來交付計劃的公司。 此外,MBCFET?的成功創造標志著三星全球業界領先的技術實力。 它為改變半導體產業奠定了基礎,否則如果按照FinFET的思路,半導體產業將停留在4nm規模。

三星在這方面搶占了先機,比臺積電和英特爾早了至少一年,三星的3nm Gate-All-Around(GAA)工藝,3GAE,開發正在進行中。該公司今天指出,它的工藝設計套件(PDK)版本0.1 for 3GAE已于4月發布。

上個月24日,三星電子宣布,將在未來10年內(至2030年)在包括代工服務在內的其邏輯芯片業務上投資133兆韓元 (約1158億美元 ),以期超越臺積電,成為全球第一大芯片代工廠,目前看來,布局3nm GAA工藝是一個好開端。

-

三星電子

+關注

關注

34文章

15863瀏覽量

181030 -

晶體管

+關注

關注

77文章

9698瀏覽量

138259

原文標題:三星發布3nm節點工藝!GAAFET!

文章出處:【微信號:BIEIqbs,微信公眾號:北京市電子科技情報研究所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星3nm良率僅20%,仍不放棄Exynos 2500處理器,欲打造“十核怪獸”

三星發布3nm節點工藝!GAAFET!

三星發布3nm節點工藝!GAAFET!

評論