流水線工作方式可節(jié)約工廠生產(chǎn)成本,可一定程度上節(jié)約生產(chǎn)工人數(shù)量,實(shí)現(xiàn)一定程度的自動(dòng)化生產(chǎn),前期投入不大,回報(bào) 率高。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603428 -

流水線

+關(guān)注

關(guān)注

0文章

120瀏覽量

25739 -

自動(dòng)化

+關(guān)注

關(guān)注

29文章

5581瀏覽量

79283

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA中的流水線設(shè)計(jì)

流水線,然后將一條指令分成 5—6 步后再由這些電路單元分別執(zhí)行,這樣就能實(shí)現(xiàn)在一個(gè) CPU 時(shí)鐘周期完成一條指令,因此提高 CPU 的運(yùn)算速度。 一般的 CPU 中,每條整數(shù)

發(fā)表于 10-26 14:38

FPGA重要設(shè)計(jì)思想及工程應(yīng)用之流水線設(shè)

FPGA重要設(shè)計(jì)思想及工程應(yīng)用之流水線設(shè)

流水線設(shè)計(jì)是高速電路設(shè)計(jì)中的一 個(gè)常用設(shè)計(jì)手段。如果某個(gè)設(shè)計(jì)的處理流程分為若干步驟,而且整個(gè)數(shù)據(jù)處理 流程分

發(fā)表于 02-09 11:02

?52次下載

基于Pezaris 算法的流水線陣列乘法器設(shè)計(jì)

介紹了補(bǔ)碼陣列乘法器的Pezaris 算法。為提高運(yùn)算速度,利用流水線技術(shù)進(jìn)行改進(jìn),設(shè)計(jì)出流水線結(jié)構(gòu)陣列乘法器,使用VHDL語(yǔ)言建模,在Qu

發(fā)表于 08-02 16:38

?0次下載

流水線中的相關(guān)培訓(xùn)教程[4]

流水線中的相關(guān)培訓(xùn)教程[4]

下面討論如何利用編譯器技術(shù)來(lái)減少這種必須的暫停,然后論述如何在流水線中實(shí)現(xiàn)數(shù)據(jù)相關(guān)檢測(cè)和定向。

發(fā)表于 04-13 16:09

?4805次閱讀

基于FPGA的高速流水線浮點(diǎn)乘法器設(shè)計(jì)與實(shí)現(xiàn)

設(shè)計(jì)了一種支持IEEE754浮點(diǎn)標(biāo)準(zhǔn)的32位高速流水線結(jié)構(gòu)浮點(diǎn)乘法器。該乘法器采用新型的基4布思算法,改進(jìn)的4:2壓縮結(jié)構(gòu)和部分積求和電路,

發(fā)表于 02-29 11:20

?3595次閱讀

FPGA之流水線練習(xí)5:設(shè)計(jì)思路

流水線的工作方式就象工業(yè)生產(chǎn)上的裝配流水線。在CPU中由5—6個(gè)不同功能的電路單元組成一條指令處理流水線,然后將一條X86指令分成5—6步后

FPGA之流水線練習(xí)(2):設(shè)計(jì)思路

流水線安裝時(shí)工作地的排列要符合工藝路線,當(dāng)工序具有兩個(gè)以上工作地時(shí),要考慮同一工序工作地的排列方法。一般當(dāng)有兩個(gè)或兩個(gè)以上偶數(shù)個(gè)同類工作地時(shí),要考慮采用雙列布置,將它們分列在運(yùn)輸路線的兩例。但當(dāng)一個(gè)工人看管多臺(tái)設(shè)備時(shí),要考慮使工人移動(dòng)的距離盡可能短。

FPGA之流水線練習(xí)4:實(shí)現(xiàn)4輸入的乘法運(yùn)算

流水線是人和機(jī)器的有效組合,最充分體現(xiàn)設(shè)備的靈活性,它將輸送系統(tǒng)、隨行夾具和在線專機(jī)、檢測(cè)設(shè)備有機(jī)的組合,以滿足多品種產(chǎn)品的輸送要求。輸送線的傳輸方式有同步傳輸?shù)?(強(qiáng)制式),也可以是非同步傳輸/(柔性式),根據(jù)配置的選擇,可以實(shí)現(xiàn)裝配和輸送的要求。輸送線在企業(yè)的批量生產(chǎn)

FPGA之流水線練習(xí)(3):設(shè)計(jì)思路

流水線的平面設(shè)計(jì)應(yīng)當(dāng)保證零件的運(yùn)輸路線最短,生產(chǎn)工人操作方便,輔助服務(wù)部門工作便利,最有效地利用生產(chǎn)面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時(shí)應(yīng)考慮流水線

FPGA之流水線練習(xí)3:設(shè)計(jì)思路

流水線主要是一種硬件設(shè)計(jì)的算法,如第一條中表述的流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器,并暫存中間數(shù)據(jù)的方法。

FPGA之流水線練習(xí)1:設(shè)計(jì)思路

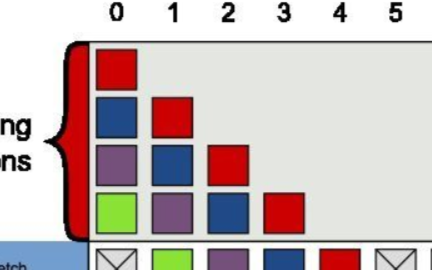

流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器,并暫存中間數(shù)據(jù)的方法。目的是將一個(gè)大操作分解成若干的小操作,每一步小操作的時(shí)間較小,所以能提高頻率,各小操作能并行執(zhí)行,所以能提高數(shù)據(jù)吞吐率(提高處理速度)。

FPGA之流水線練習(xí)4:設(shè)計(jì)思路

流水線設(shè)計(jì)就是將組合邏輯系統(tǒng)地分割,并在各個(gè)部分(分級(jí))之間插入寄存器,并暫存中間數(shù)據(jù)的方法。目的是將一個(gè)大操作分解成若干的小操作,每一步小操作的時(shí)間較小,所以能提高頻率,各小操作能并行執(zhí)行,所以能提高數(shù)據(jù)吞吐率(提高處理速度)。

什么是流水線 Jenkins的流水線詳解

jenkins 有 2 種流水線分為聲明式流水線與腳本化流水線,腳本化流水線是 jenkins 舊版本使用的流水線腳本,新版本 Jenkin

發(fā)表于 05-17 16:57

?1086次閱讀

FPGA之流水線練習(xí)5:實(shí)現(xiàn)4輸入的乘法運(yùn)算

FPGA之流水線練習(xí)5:實(shí)現(xiàn)4輸入的乘法運(yùn)算

評(píng)論