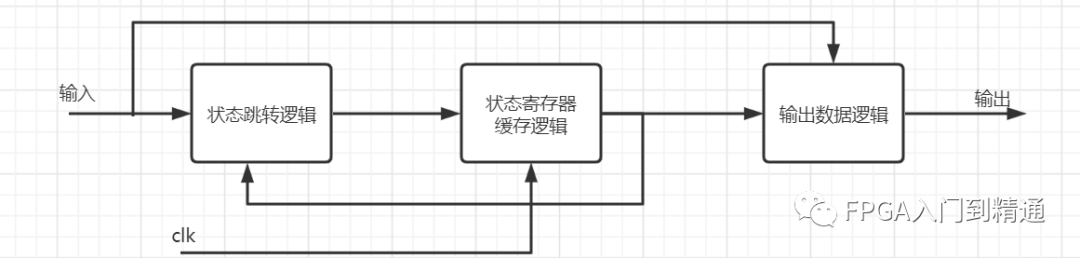

狀態(tài)機(jī)有三種描述方式:一段式狀態(tài)機(jī)、兩段式狀態(tài)機(jī)、三段式狀態(tài)機(jī)。下面就用一個(gè)小例子來(lái)看看三種方式是如何實(shí)現(xiàn)的。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603319 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

492瀏覽量

27539

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA工程師:如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)?

安全高效的狀態(tài)機(jī)設(shè)計(jì)對(duì)于任何使用FPGA的工程師而言都是一項(xiàng)重要技能。選擇Moore狀態(tài)機(jī)、Mealy狀態(tài)機(jī)還是混合機(jī)取決于整個(gè)系統(tǒng)的需求。

發(fā)表于 03-29 15:02

?1.3w次閱讀

Spring狀態(tài)機(jī)的實(shí)現(xiàn)原理和使用方法

說(shuō)起 Spring 狀態(tài)機(jī),大家很容易聯(lián)想到這個(gè)狀態(tài)機(jī)和設(shè)計(jì)模式中狀態(tài)模式的區(qū)別是啥呢?沒錯(cuò),Spring 狀態(tài)機(jī)就是狀態(tài)模式的一種

如何在微型計(jì)算機(jī)中實(shí)現(xiàn)狀態(tài)機(jī)?

實(shí)現(xiàn)基礎(chǔ)的軟件(我后悔沒有跟蹤它們),并且取決于它們是否在(可能)C或Assembly中編寫,它們所做的是在Assembly中實(shí)現(xiàn)長(zhǎng)塊的“開關(guān)盒”鏈或類似的東西:找到實(shí)現(xiàn)它的相當(dāng)粗略的方法。我看不出其他的辦法。我的問(wèn)題是:這是用

發(fā)表于 09-30 09:18

華清遠(yuǎn)見FPGA代碼-狀態(tài)機(jī)

FPGA學(xué)習(xí)資料教程——華清遠(yuǎn)見FPGA代碼-狀態(tài)機(jī)

發(fā)表于 10-27 18:07

?9次下載

利用狀態(tài)機(jī)的狀態(tài)機(jī)實(shí)現(xiàn)層次結(jié)構(gòu)化設(shè)計(jì)

練習(xí)九.利用狀態(tài)機(jī)的嵌套實(shí)現(xiàn)層次結(jié)構(gòu)化設(shè)計(jì)目的:1.運(yùn)用主狀態(tài)機(jī)與子狀態(tài)機(jī)產(chǎn)生層次化的邏輯設(shè)計(jì);

發(fā)表于 02-11 05:52

?3312次閱讀

使用verilog HDL實(shí)現(xiàn)狀態(tài)機(jī)8位流水燈的程序和工程文件免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是使用verilog HDL實(shí)現(xiàn)狀態(tài)機(jī)8位流水燈的程序和工程文件免費(fèi)下載。

發(fā)表于 10-16 16:20

?23次下載

使用函數(shù)指針的方法實(shí)現(xiàn)狀態(tài)機(jī)

之前寫過(guò)一篇狀態(tài)機(jī)的實(shí)用文章,很多朋友說(shuō)有幾個(gè)地方有點(diǎn)難度不易理解,今天給大家換種簡(jiǎn)單寫法,使用函數(shù)指針的方法實(shí)現(xiàn)狀態(tài)機(jī)。 狀態(tài)機(jī)簡(jiǎn)介 有限狀態(tài)機(jī)FSM是有限個(gè)

FPGA:狀態(tài)機(jī)簡(jiǎn)述

是FPGA設(shè)計(jì)中一種非常重要、非常根基的設(shè)計(jì)思想,堪稱FPGA的靈魂,貫穿FPGA設(shè)計(jì)的始終。 02. 狀態(tài)機(jī)簡(jiǎn)介 什么是狀態(tài)機(jī):

經(jīng)典雙進(jìn)程狀態(tài)機(jī)的FPGA實(shí)現(xiàn)(含testbeach)

經(jīng)典雙進(jìn)程狀態(tài)機(jī)的FPGA實(shí)現(xiàn)(含testbeach)(肇慶理士電源技術(shù)有限公司圖片)-該文檔為經(jīng)典雙進(jìn)程狀態(tài)機(jī)的FPGA

發(fā)表于 08-31 13:26

?3次下載

LABVIEW的狀態(tài)機(jī)實(shí)現(xiàn)資料合集

LABVIEW的狀態(tài)機(jī)實(shí)現(xiàn)資料合集

發(fā)表于 01-04 11:18

?47次下載

詳細(xì)介紹FPGA狀態(tài)機(jī)的設(shè)計(jì)和應(yīng)用

FPGA的特點(diǎn)是并行執(zhí)行,但如果需要處理一些具有前后順序的事件,就需要使用狀態(tài)機(jī)。

發(fā)表于 05-22 14:24

?1275次閱讀

如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

狀態(tài)機(jī)往往是FPGA 開發(fā)的主力。選擇合適的架構(gòu)和實(shí)現(xiàn)方法將確保您獲得一款最佳解決方案。 FPGA 常常用于執(zhí)行基于序列和控制的行動(dòng), 比如實(shí)現(xiàn)

基于FPGA的狀態(tài)機(jī)設(shè)計(jì)

狀態(tài)機(jī)的基礎(chǔ)知識(shí)依然強(qiáng)烈推薦mooc上華科的數(shù)字電路與邏輯設(shè)計(jì),yyds!但是數(shù)電基礎(chǔ)一定要和實(shí)際應(yīng)用結(jié)合起來(lái),理論才能發(fā)揮真正的價(jià)值。我們知道FPGA是并行執(zhí)行的,如果我們想要處理具有前后順序的事件就需要引入狀態(tài)機(jī)。

什么是狀態(tài)機(jī)?狀態(tài)機(jī)的種類與實(shí)現(xiàn)

狀態(tài)機(jī),又稱有限狀態(tài)機(jī)(Finite State Machine,F(xiàn)SM)或米利狀態(tài)機(jī)(Mealy Machine),是一種描述系統(tǒng)狀態(tài)變化的模型。在芯片設(shè)計(jì)中,

如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

在FPGA(現(xiàn)場(chǎng)可編程門陣列)中實(shí)現(xiàn)狀態(tài)機(jī)是一種常見的做法,用于控制復(fù)雜的數(shù)字系統(tǒng)行為。狀態(tài)機(jī)能夠根據(jù)當(dāng)前的輸入和系統(tǒng)狀態(tài),決定下一步的動(dòng)作和新的狀

基于FPGA實(shí)現(xiàn)狀態(tài)機(jī)的設(shè)計(jì)

基于FPGA實(shí)現(xiàn)狀態(tài)機(jī)的設(shè)計(jì)

評(píng)論