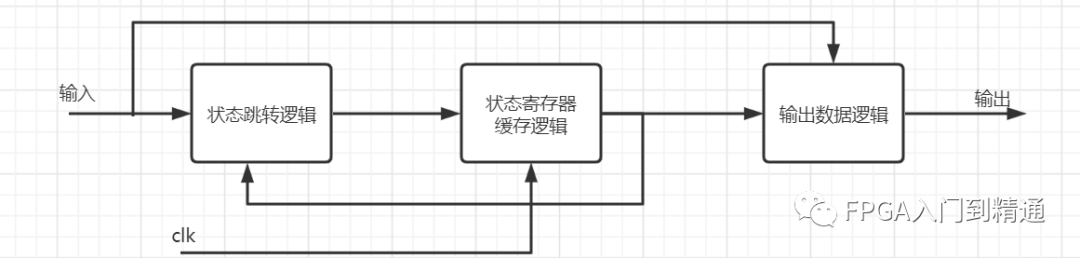

狀態機可歸納為4個要素,即現態、條件、動作、次態。這樣的歸納,主要是出于對狀態機的內在因果關系的考慮。“現態”和“條件”是因,“動作”和“次態”是果。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21767瀏覽量

604615 -

設計

+關注

關注

4文章

818瀏覽量

69915 -

狀態機

+關注

關注

2文章

492瀏覽量

27591

發布評論請先 登錄

相關推薦

FPGA工程師:如何在FPGA中實現狀態機?

安全高效的狀態機設計對于任何使用FPGA的工程師而言都是一項重要技能。選擇Moore狀態機、Mealy狀態機還是混合機取決于整個系統的需求。

發表于 03-29 15:02

?1.3w次閱讀

數字設計FPGA應用:時鐘同步狀態機設計方法構建序列發生器

狀態機由狀態寄存器和組合邏輯電路構成,能夠根據控制信號按照預先設定的狀態進行狀態轉移,是協調相關信號動作,完成特定操作的控制中心。狀態機分為

如何在FPGA中實現狀態機

狀態機往往是FPGA 開發的主力。選擇合適的架構和實現方法將確保您獲得一款最佳解決方案。 FPGA 常常用于執行基于序列和控制的行動, 比如實現一個簡單的通信協議。對于設計人員來說,滿足這些行動

基于FPGA的狀態機設計

狀態機的基礎知識依然強烈推薦mooc上華科的數字電路與邏輯設計,yyds!但是數電基礎一定要和實際應用結合起來,理論才能發揮真正的價值。我們知道FPGA是并行執行的,如果我們想要處理具有前后順序的事件就需要引入

如何在FPGA中實現狀態機

在FPGA(現場可編程門陣列)中實現狀態機是一種常見的做法,用于控制復雜的數字系統行為。狀態機能夠根據當前的輸入和系統狀態,決定下一步的動作

數字設計FPGA應用:時鐘同步狀態機及其設計流程

數字設計FPGA應用:時鐘同步狀態機及其設計流程

評論