在異步設(shè)計中,完全避免亞穩(wěn)態(tài)是不可能的。因此,設(shè)計的基本思路應(yīng)該是:首先盡可能減少出現(xiàn)亞穩(wěn)態(tài)的可能性,其次是盡可能減少出現(xiàn)亞穩(wěn)態(tài)并給系統(tǒng)帶來危害的可能性。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603660 -

設(shè)計

+關(guān)注

關(guān)注

4文章

818瀏覽量

69905 -

異步

+關(guān)注

關(guān)注

0文章

62瀏覽量

18062

發(fā)布評論請先 登錄

相關(guān)推薦

明德?lián)P點撥FPGA在線培訓(xùn)課程下載 很實用的資料

課程就足夠?qū)W習(xí)FPGA,無須再學(xué)習(xí)其他資料,是您學(xué)習(xí)FPGA的最佳選擇。感覺課程非常實用,與眾不同的地方在于,它練習(xí)很多,而且會先出一個功能文檔,然后按照文檔設(shè)計,接著對照設(shè)計思路,看

發(fā)表于 05-20 14:47

【明德?lián)P視頻分享】點撥FPGA課程--第十九章??異步時序處理

1. 異步時序和亞穩(wěn)態(tài)2. 三態(tài)門3. 異步時序練習(xí)14. 異步時序練習(xí)1答案5. 異步時序

發(fā)表于 11-06 09:08

異步FIFO結(jié)構(gòu)及FPGA設(shè)計

首先介紹異步FIFO 的概念、應(yīng)用及其結(jié)構(gòu),然后分析實現(xiàn)異步FIFO的難點問題及其解決辦法; 在傳統(tǒng)設(shè)計的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對其進行綜合仿真和FPGA 實現(xiàn)。

發(fā)表于 04-16 09:25

?46次下載

高速異步FIFO的設(shè)計與實現(xiàn)

本文主要研究了用FPGA 芯片內(nèi)部的EBRSRAM 來實現(xiàn)異步FIFO 設(shè)計方案,重點闡述了異步FIFO 的標(biāo)志信號——空/滿狀態(tài)的設(shè)計思路,并且用VHDL 語言實現(xiàn),最后進行了仿真驗

發(fā)表于 01-13 17:11

?40次下載

異步FIFO結(jié)構(gòu)及FPGA設(shè)計

異步FIFO結(jié)構(gòu)及FPGA設(shè)計,解決亞穩(wěn)態(tài)的問題

發(fā)表于 11-10 15:21

?4次下載

FPGA之異步練習(xí)2:設(shè)計思路

異步雙方不需要共同的時鐘,也就是接收方不知道發(fā)送方什么時候發(fā)送,所以在發(fā)送的信息中就要有提示接收方開始接收的信息,如開始位,同時在結(jié)束時有停止位。

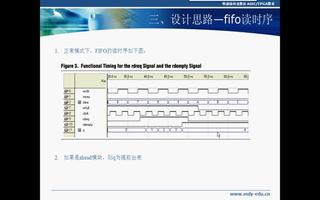

FPGA之FIFO練習(xí)1:設(shè)計思路

FIFO隊列具有處理簡單,開銷小的優(yōu)點。但FIFO不區(qū)分報文類型,采用盡力而為的轉(zhuǎn)發(fā)模式,使對時間敏感的實時應(yīng)用(如VoIP)的延遲得不到保證,關(guān)鍵業(yè)務(wù)的帶寬也不能得到保證。

FPGA之FIFO練習(xí)3:設(shè)計思路

根據(jù)FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發(fā)生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

FPGA之異步練習(xí)2:接口時序參數(shù)

異步時序電路是指電路中除以使用帶時鐘的觸發(fā)器外,還可以使用不帶時鐘的觸發(fā)器和延遲元件作為存儲元件;電路中沒有統(tǒng)一的時鐘;電路狀態(tài)的改變由外部輸入的變化直接引起。

FPGA異步練習(xí)之測試文件(2)

FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲單元加載編程數(shù)據(jù)來實現(xiàn)的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實現(xiàn)的功能,FPGA允許無限次的編程。

FPGA之異步練習(xí)1:設(shè)計思路

基于FPGA的數(shù)字系統(tǒng)設(shè)計中大都推薦采用同步時序的設(shè)計,也就是單時鐘系統(tǒng)。但是實際的工程中,純粹單時鐘系統(tǒng)設(shè)計的情況很少,特別是設(shè)計模塊與外圍芯片的通信中,跨時鐘域的情況經(jīng)常不可避免。

FPGA之FIFO練習(xí)2:設(shè)計思路

FIFO( First Input First Output)簡單說就是指先進先出。由于微電子技術(shù)的飛速發(fā)展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。

分形生成FPGA設(shè)計練習(xí)

電子發(fā)燒友網(wǎng)站提供《分形生成FPGA設(shè)計練習(xí).zip》資料免費下載

發(fā)表于 07-06 10:09

?0次下載

FPGA異步信號處理方法

FPGA(現(xiàn)場可編程門陣列)在處理異步信號時,需要特別關(guān)注信號的同步化、穩(wěn)定性以及潛在的亞穩(wěn)態(tài)問題。由于異步信號可能來自不同的時鐘域或外部設(shè)備,其到達時間和頻率可能不受FPGA內(nèi)部時鐘

FPGA之異步練習(xí):設(shè)計思路

FPGA之異步練習(xí):設(shè)計思路

評論