顧名思義,EMC就是關于如何解決電子設備如何對其他設備產生干擾、或防止外部設備對自身電子設備產生電磁場干擾的問題。在PCB布線設計中,特別是高速電路設計,您必須得考慮電路的電磁兼容,不然的話,您的產品很可能通不過3C標準。

今天我們就來講講電磁兼容(EMC)在PCB布線設計中,需要注意哪些具體設計細節,注意哪些問題。從大體上來講 ,PCB電磁兼容的設計,要對以下這幾類電路布線重點關注。

1.強輻射信號線(高頻、高速、時鐘走線為代表)2.敏感信號(如復位信號)3.功率電源信號4.接口信號(模擬接口或數字通信接口)

下面,我們針對普遍的PCB電路和高速電路PCB電磁兼容設計,詳細列舉一二。

一、電磁兼容在低速信號的PCB設計問題

低速電路PCB設計中,我們需要考慮如下幾點要素:

1、電源走線策略

對于電源來說,任何板都要遵循此規則。每個芯片電源管腳必須放置0.1uF的電容。這樣能濾除芯片電源高速干擾。對于不鋪銅,而是直接走粗線的,每隔3000mil必須加電容(10uF+0.1uF)。這樣高頻噪聲會濾除。

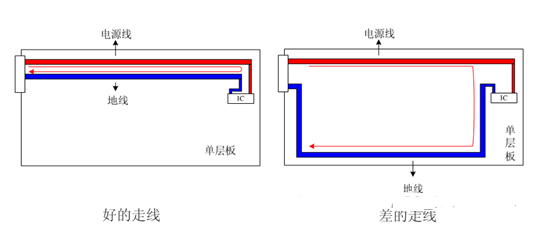

單層板的話,電源與地必須緊挨著走線,以減少回流環路面積。如下圖

2、敏感信號的走線策略

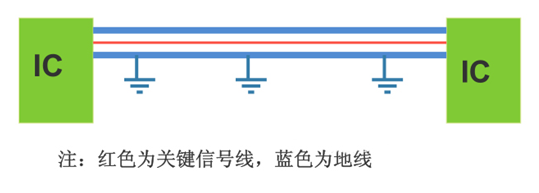

對于敏感信號最好是要用地包住。這樣包地即提供了信吃最短回流路徑,也能消除與其它相鄰信號的干擾。如下圖

如果是多層板,對于特別敏感的信號線除了同層用包地處理,還可以上,下兩層也是大面積的鋪地。這樣,使信號的上,下,左,右都有地包著。保證信號的干凈。

3、信號的回流面積最小定律

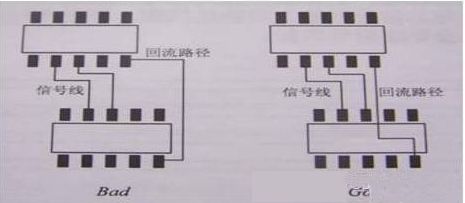

在PCB設計中,每根信號最好能做到與地的回流路徑最短,如下圖所示

回路面積最小,信號的抗干擾能力加強,對外的EMI也達到最小。單雙面的話,只能使地回路盡可能的短。本文微信公眾號: PCB_technique。對于多層板,就要在相鄰層鋪上大面積的銅作為地。這個鋪大面積的銅的相鄰層,也叫信號的參考層。做阻抗設計時,就是以這個參考層來計算阻抗大小的。

4、PCB的走線方式

PCB走線不能走直角,一般走45度角。高速信號最好走圓弧。超高速信號10度走線。走線寬度要一致,不然會產生阻抗不連續。對于高速信號就會產生不必要的反射,振鈴。

5、相鄰層的布線策略

相鄰層走線時,最好是形成垂直。一層是平行走線,那相鄰層就要垂直走線。這樣相鄰層的信號不會形成干擾。實在無法避免,就適當減小平行走線線段的長度。最好小于1000mil

6、在電源線中過孔的個數

在布電源線時,在不同層連接用到過孔時,必須考慮良好連接性。如果電流大,由于過孔的電阻性,放一個過孔可能會降低到終端的電壓。導致到芯片電源腳的電壓低于實際設計的電壓,而使芯片不能工作。這時我們在換層連接處多加幾個過孔。

7、電容的放置及布線

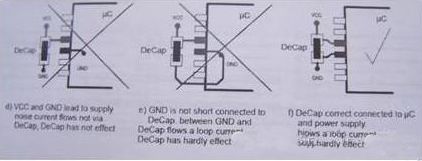

濾波電容在放置時,如第1條所說,要靠近芯片管腳放置,布線要盡可能的粗,短。保證濾高頻效果。電容接地腳要就近打孔到地層。不能連一根很長的線再跟地相連。如下圖所示

二、電磁兼容在高速信號的PCB設計問題

1、3W與20H法則

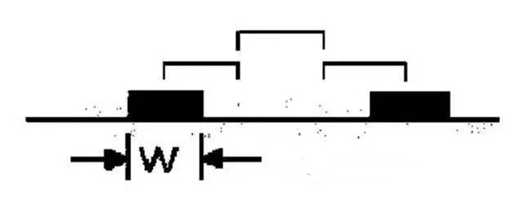

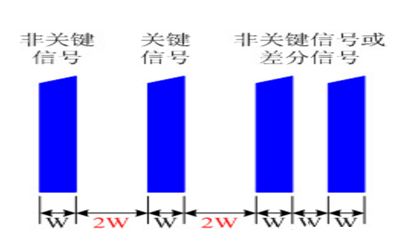

3W就是信號線之間的布線間距是線寬的兩倍,中心距是3倍。如圖所示:

3W的線間距,可以保證不受其它干擾信號的電場達到70%以上,如要達到98%的電場不互相干擾,就要使用10W的間距。

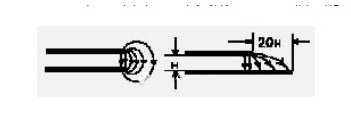

20H是指多層板電源平面要比地平面邊緣縮進兩個平面之間間距的20倍以上。這樣,電源被地包圍在地平面之內,大減小了向外輻射的機率。如下圖所示:

2、高速信號的走線層次選擇

高速信號線最好是走在里層,這樣介質層起到屏蔽作用,能有效抑制EMI信號的向外輻射。

3、高帶關鍵信號包地處理

高速信號線中如時鐘錢,最好采用包地處理,而且包地每隔3000mil打一個過孔連接到地層。關鍵信號與其它線之間要滿足3W規則。如下圖所示:

-

pcb

+關注

關注

4324文章

23135瀏覽量

398877 -

電磁

+關注

關注

15文章

1137瀏覽量

51882

原文標題:高速PCB設計中考慮EMC,您不得不知道的布線技巧(附完整EMC學習大禮包)

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高速PCB設計中考慮EMC的布線技巧

高速PCB設計中考慮EMC的布線技巧

評論