鎖相環(huán)在工作的過(guò)程中,當(dāng)輸出信號(hào)的頻率與輸入信號(hào)的頻率相等時(shí),輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環(huán)名稱(chēng)的由來(lái)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

仿真

+關(guān)注

關(guān)注

50文章

4102瀏覽量

133739 -

pll

+關(guān)注

關(guān)注

6文章

777瀏覽量

135208 -

頻率

+關(guān)注

關(guān)注

4文章

1514瀏覽量

59276

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SF-EP1C V3.1光盤(pán)找不到了,還能下到資料嗎?

很早以前買(mǎi)的開(kāi)發(fā)板SF-EP1C V3.1,光盤(pán)找不到了,在哪里能下到光盤(pán)的資料啊?謝謝!

發(fā)表于 04-07 13:11

仿照特權(quán)同學(xué)視頻教程第29講操作出錯(cuò)

特權(quán)同學(xué)CPLD視頻教程第29講Lesson29:SF-EP1C開(kāi)發(fā)板實(shí)驗(yàn)8——基于M4K塊的移位寄存器配置仿真實(shí)驗(yàn).wmv我操作了一下,和視頻不太一樣,出錯(cuò)了,見(jiàn)下圖高手看看,如何解

發(fā)表于 10-18 22:35

基于EP1C3的進(jìn)階實(shí)驗(yàn)_cyclone_PLL_Test2

基于EP1C3的進(jìn)階實(shí)驗(yàn)_cyclone_PLL_Test2

發(fā)表于 01-21 11:24

?8次下載

基于EP1C3的進(jìn)階實(shí)驗(yàn)_Cyclone_PLL_Test1

基于EP1C3的進(jìn)階實(shí)驗(yàn)_Cyclone_PLL_Test1

發(fā)表于 01-21 11:24

?5次下載

基于EP1C3的進(jìn)階實(shí)驗(yàn)cyclone_PLL_Test2

基于EP1C3的進(jìn)階實(shí)驗(yàn)cyclone_PLL_Test2

發(fā)表于 10-27 18:20

?10次下載

基于EP1C3的進(jìn)階實(shí)驗(yàn)Cyclone_PLL_Test1

基于EP1C3的進(jìn)階實(shí)驗(yàn)Cyclone_PLL_Test1

發(fā)表于 10-27 18:20

?18次下載

基于EP1C3的進(jìn)階實(shí)驗(yàn)_cyclone_PLL_Test2

基于EP1C3的進(jìn)階實(shí)驗(yàn)_cyclone_PLL_Test2

發(fā)表于 11-18 16:05

?0次下載

FPGA視頻教程之SF-EP1C開(kāi)發(fā)板PLL配置仿真實(shí)驗(yàn)的詳細(xì)資料說(shuō)明

不僅僅從頻率和相位上比較穩(wěn)定,而且其時(shí)鐘網(wǎng)絡(luò)延時(shí)也相比內(nèi)部邏輯產(chǎn)生的分頻時(shí)鐘要小得多。下面就如何配置一一個(gè)PLL做一些說(shuō)明。

發(fā)表于 03-06 11:14

?2次下載

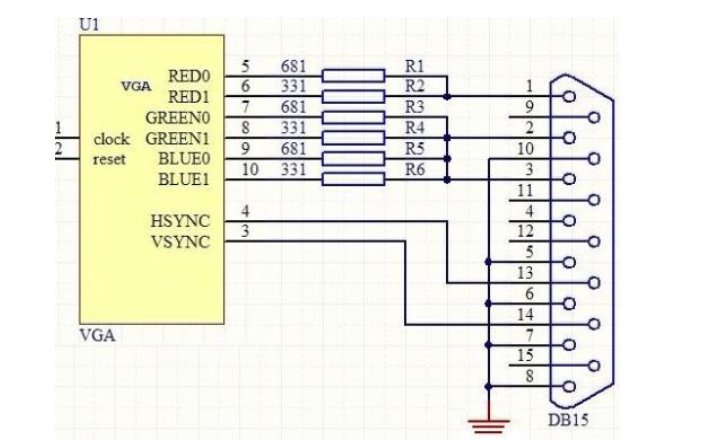

FPGA視頻教程之SF-EP1C開(kāi)發(fā)板256色VGA顯示實(shí)驗(yàn)的詳細(xì)資料說(shuō)明

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之SF-EP1C開(kāi)發(fā)板256色VGA顯示實(shí)驗(yàn)的詳細(xì)資料說(shuō)明。

發(fā)表于 03-06 11:14

?6次下載

FPGA視頻教程之SF-EP1C開(kāi)發(fā)板基于M4K塊的移位寄存器配置仿真實(shí)驗(yàn)說(shuō)明

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之SF-EP1C開(kāi)發(fā)板基于M4K塊的移位寄存器配置仿真實(shí)驗(yàn)說(shuō)明資料免費(fèi)下載。

發(fā)表于 03-06 14:01

?8次下載

SF-EP1C開(kāi)發(fā)板之256色VGA顯示實(shí)驗(yàn)

本視頻的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之SF-EP1C開(kāi)發(fā)板256色VGA顯示實(shí)驗(yàn)的詳細(xì)資料說(shuō)明。

SF-EP1C開(kāi)發(fā)板之基于M4K塊的移位寄存器配置仿真實(shí)驗(yàn)

本視頻的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之SF-EP1C開(kāi)發(fā)板基于M4K塊的移位寄存器配置仿真實(shí)驗(yàn)說(shuō)明。

SF-EP1C開(kāi)發(fā)板之PLL配置仿真實(shí)驗(yàn)

得到的時(shí)鐘不僅僅從頻率和相位上比較穩(wěn)定,而且其時(shí)鐘網(wǎng)絡(luò)延時(shí)也相比內(nèi)部邏輯產(chǎn)生的分頻時(shí)鐘要小得多。”下面就如何配置一一個(gè)PLL做一些說(shuō)明。

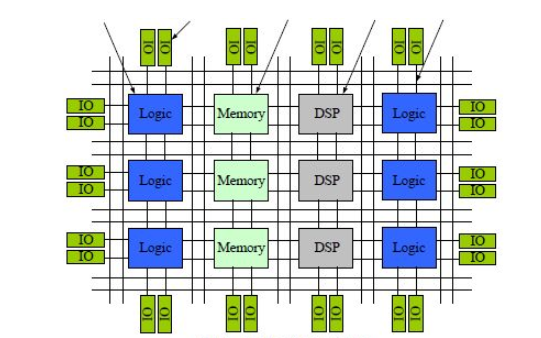

深入淺出玩轉(zhuǎn)FPGA視頻:SF-EP1C開(kāi)發(fā)板介紹

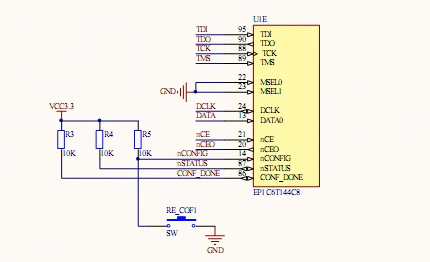

SF-EP1C開(kāi)發(fā)板有著比較豐富的外設(shè),也給用戶預(yù)留了一些可擴(kuò)展的接口。FPGA使用EP1C3T144C8,硬件電路充分考慮了可升級(jí)性,該板子同樣適用于EP1C6T144。

FPGA視頻教程:SF-EP1C開(kāi)發(fā)板-PLL配置仿真實(shí)驗(yàn)

7、1個(gè)串口;1個(gè)SD卡接口;1個(gè)256色VGA接口;?1個(gè)64MBit(4*1M*256Bit)?SDRAM;?8位撥碼開(kāi)關(guān)

SF-EP1C學(xué)習(xí)板:PLL配置仿真實(shí)驗(yàn)

SF-EP1C學(xué)習(xí)板:PLL配置仿真實(shí)驗(yàn)

評(píng)論