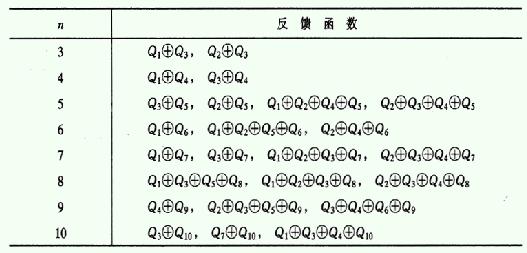

移位寄存器是另一種類型的時序邏輯電路,可用于存儲或傳輸二進制數(shù)據(jù)

此順序設(shè)備加載其輸入上的數(shù)據(jù)然后移動或每個時鐘周期將其“移位”到輸出,因此名稱移位寄存器。

移位寄存器基本上由幾個單位“D”組成 - 類型數(shù)據(jù)鎖存器,每個數(shù)據(jù)位一個,邏輯“0”或“1”,以串行型菊花鏈方式連接在一起,以便一個數(shù)據(jù)鎖存器的輸出成為下一個鎖存器的輸入

數(shù)據(jù)位可以串行輸入或輸出移位寄存器,從左或右方向一個接一個地輸入,或者在并行配置中同時輸出。

組成單個移位寄存器設(shè)備所需的單個數(shù)據(jù)鎖存器的數(shù)量通常取決于最常用的存儲位數(shù)b由8個單獨的數(shù)據(jù)鎖存器構(gòu)成的8位(1字節(jié))寬。

移位寄存器用于數(shù)據(jù)存儲或數(shù)據(jù)移動,因此通常用于計算器內(nèi)部或計算機在將數(shù)據(jù)添加到一起之前存儲數(shù)據(jù),例如兩個二進制數(shù),或者將數(shù)據(jù)從串行轉(zhuǎn)換為并行或并行轉(zhuǎn)換為串行格式。構(gòu)成單個移位寄存器的各個數(shù)據(jù)鎖存器均由公共時鐘(Clk)信號驅(qū)動,使其成為同步器件。

移位寄存器IC通常提供 clear 或重置連接,以便它們可以根據(jù)需要“設(shè)置”或“重置”。通常,移位寄存器以四種不同模式之一運行,數(shù)據(jù)通過移位寄存器的基本移動為:

串行輸入到并行輸出(SIPO) - 寄存器加載串行數(shù)據(jù),一次一位,存儲的數(shù)據(jù)以并行形式在輸出端可用。

串行輸入到串行輸出(SISO) - 數(shù)據(jù)在寄存器的“IN”和“OUT”串行移位,在時鐘控制下左右兩個方向一次一位。

并行輸出到串行輸出(PISO) - 并行數(shù)據(jù)同時加載到寄存器中,并在寄存器中串行移出一位時鐘控制下的時間。

并行到并行輸出(PIPO) - 并行數(shù)據(jù)同時加載到寄存器中,并一起傳輸?shù)剿鼈兏髯缘妮敵鲇上嗤臅r鐘脈沖組成。

d的影響ata通過移位寄存器從左向右移動可以圖形方式顯示為:

此外,定向運動通過移位寄存器的數(shù)據(jù)可以在左側(cè),(左側(cè)移位)到右側(cè),(右側(cè)移位)左側(cè)但右側(cè)外側(cè),(旋轉(zhuǎn))或左右兩側(cè)移位在同一寄存器內(nèi),從而使其成為可能雙向。在本教程中,假設(shè)所有數(shù)據(jù)都向右移動(右移)。

串行輸入到并行輸出(SIPO)移位寄存器

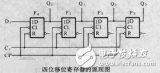

4位串行-in到并行移位寄存器

操作如下。讓我們假設(shè)所有觸發(fā)器( FFA 到 FFD )剛剛復(fù)位(CLEAR輸入)并且所有輸出 Q A 到 Q D 處于邏輯電平“0”,即沒有并行數(shù)據(jù)輸出。

如果邏輯“1”連接到 FFA 的 DATA 輸入引腳,則在第一個時鐘脈沖輸出 FFA 和因此,得到的 Q A 將設(shè)置為高電平為邏輯“1”,所有其他輸出仍然保持低電平為邏輯“0”。現(xiàn)在假設(shè) FFA 的 DATA 輸入引腳再次返回到邏輯“0”,給出一個數(shù)據(jù)脈沖或0-1-0。

第二個時鐘脈沖將 FFA 的輸出更改為邏輯“0”,輸出 FFB 和 Q B HIGH至邏輯“1”,因為其輸入 D 在 Q A 上具有邏輯“1”電平。邏輯“1”現(xiàn)在已經(jīng)沿著寄存器向右移動或“移位”了一個位置,因為它現(xiàn)在位于 Q A 。

當(dāng)?shù)谌齻€時鐘脈沖到達時,此邏輯“1”值移至 FFC ( Q C )的輸出,依此類推,直至到達第五個時鐘脈沖,將所有輸出 Q A 再次設(shè)置為 Q D 再次返回邏輯電平“0”因為 FFA 的輸入在邏輯電平“0”保持不變。

每個時鐘脈沖的作用是將每個階段的數(shù)據(jù)內(nèi)容向右移動一個位置,這將在下表中顯示,直到 0-0-0-1 的完整數(shù)據(jù)值存儲在寄存器中。現(xiàn)在可以直接從 Q A 到 Q D 的輸出讀取該數(shù)據(jù)值。

然后,數(shù)據(jù)已從串行數(shù)據(jù)輸入信號轉(zhuǎn)換為并行數(shù)據(jù)輸出。真值表和后續(xù)波形顯示邏輯“1”從左到右通過寄存器傳播如下。

通過移位寄存器的基本數(shù)據(jù)移動

注意第四個時鐘脈沖結(jié)束后的4位數(shù)據(jù)( 0-0-0-1 )存儲在寄存器中,并將保留在那里提供時鐘登記冊已經(jīng)停止。實際上,寄存器的輸入數(shù)據(jù)可以包括邏輯“1”和“0”的各種組合。通用的 SIPO IC包括標(biāo)準(zhǔn)的8位74LS164或74LS594。

串行輸出到串行輸出(SISO)移位寄存器

這個移位寄存器與上面的SIPO非常相似,只是在數(shù)據(jù)被直接讀取之前從輸出 Q A 到 Q D 的并行形式,這次允許數(shù)據(jù)直接流過注冊并退出另一端。由于只有一個輸出, DATA 以串行模式一次一位地保留移位寄存器,因此名稱串行輸入到串行輸出移位寄存器或SISO。

SISO移位寄存器是四種配置中最簡單的一種,因為它只有三個連接,串行輸入(SI)決定進入左側(cè)翻轉(zhuǎn)的內(nèi)容-flop,串行輸出(SO),取自右手觸發(fā)器的輸出和時序信號(Clk)。下面的邏輯電路圖顯示了一個通用的串行輸出串行移位寄存器。

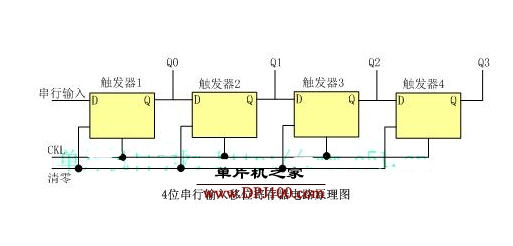

4位串行輸入到串行輸出移位寄存器

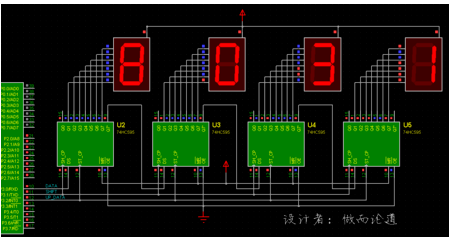

如果輸出數(shù)據(jù)與輸入數(shù)據(jù)完全相同,您可能會想到SISO移位寄存器的重點。那么這種類型的移位寄存器也可以作為臨時存儲設(shè)備,或者它可以作為數(shù)據(jù)的時間延遲設(shè)備,時間延遲量由寄存器中的級數(shù)控制, 4,8,16等或通過改變時鐘脈沖的應(yīng)用。常用的IC包括74HC595 8位串行輸入到串行輸出移位寄存器,全部具有3態(tài)輸出。

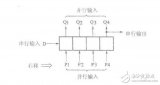

并行輸出到串行輸出(PISO)移位寄存器

并行到串行輸出移位寄存器的作用與上面的串行輸入和并行輸出相反。數(shù)據(jù)以并行格式加載到寄存器中,其中所有數(shù)據(jù)位同時進入其輸入,并行輸入引腳 P A 至 P D 的寄存器。然后以正常右移模式從 Q 處的寄存器順序讀出數(shù)據(jù),表示 P A 處的數(shù)據(jù)到 p <子> d

該數(shù)據(jù)在每個時鐘周期以串行格式一次一位地輸出。值得注意的是,對于這種類型的數(shù)據(jù)寄存器,不需要時鐘脈沖來并行加載寄存器,因為它已經(jīng)存在,但需要四個時鐘脈沖來卸載數(shù)據(jù)。

4位并行輸出移位寄存器

由于此類移位寄存器轉(zhuǎn)換并行數(shù)據(jù),例如將8位數(shù)據(jù)字轉(zhuǎn)換為串行格式,它可以用于將許多不同的輸入線復(fù)用成單個串行數(shù)據(jù)流,該數(shù)據(jù)流可以直接發(fā)送到計算機或通過通信線路傳輸。常用的IC包括74HC166 8位并行/串行輸出移位寄存器。

并行輸出(PIPO)移位寄存器

最終操作模式是并行到并行移位寄存器。這種類型的移位寄存器還充當(dāng)臨時存儲設(shè)備或類似于上述SISO配置的時間延遲設(shè)備。數(shù)據(jù)以并行格式顯示在并行輸入引腳 P A 到 P D ,然后一起傳輸通過相同的時鐘脈沖直接將它們的輸出引腳 Q A 連接到 Q D 。然后一個時鐘脈沖加載和卸載寄存器。這種并行加載和卸載的安排如下所示。

4位并行到并行移位寄存器

PIPO移位寄存器是四種配置中最簡單的一種,因為它只有三個連接,并行輸入(PI)決定了什么進入觸發(fā)器,并行輸出(PO)和序列時鐘信號(Clk)。

類似于串行輸入到串行輸出移位寄存器,這種類型的寄存器也可以作為臨時存儲設(shè)備或延時設(shè)備,具有時間量延遲隨時鐘脈沖的頻率而變化。此外,在這種類型的寄存器中,各個觸發(fā)器之間沒有互連,因為不需要對數(shù)據(jù)進行串行移位。

通用移位寄存器

今天有很多高速度雙向“通用”類型移位寄存器可用,例如TTL 74LS194,74LS195或 CMOS 4035 ,它們可用作4位多功能設(shè)備,可以是用于串行到串行,左移,右移,串行到并行,并行到串行,或作為并行到并行的多功能數(shù)據(jù)寄存器,因此它們的名稱為“通用”。

這些通用移位寄存器可以執(zhí)行并行和串行輸入到輸出操作的任意組合,但需要額外的輸入來指定所需的功能以及預(yù)加載和復(fù)位器件。常用的通用移位寄存器是TTL 74LS194,如下所示。

4位通用移位寄存器74LS194

通用移位寄存器是非常有用的數(shù)字設(shè)備。它們可以配置為響應(yīng)需要某種形式的臨時存儲器存儲的操作,或者用于延遲信息(例如SISO或PIPO配置模式)或以串行或并行格式將數(shù)據(jù)從一個點傳輸?shù)搅硪粋€點。通用移位寄存器經(jīng)常用于算術(shù)運算中,用于向左或向右移位數(shù)據(jù)以進行乘法或除法。

移位寄存器教程摘要

然后總結(jié)一下Shift寄存器

一個簡單的移位寄存器可以僅使用D型觸發(fā)器,每個數(shù)據(jù)位一個觸發(fā)器。

每個觸發(fā)器的輸出連接到右側(cè)觸發(fā)器的 D 輸入。

移位寄存器將數(shù)據(jù)保存在存儲器中,并在每個時鐘脈沖上移動或“移位”到所需位置。

每個時鐘脈沖將寄存器的內(nèi)容移位一位到左側(cè)或右側(cè)。

數(shù)據(jù)位可以在串行輸入(SI)配置中一次一位地加載,或者以并行配置(PI)同時加載。

對于串聯(lián)輸出(SO),可以一次一位地從寄存器中刪除數(shù)據(jù),或者從并行輸出(PO)同時刪除所有數(shù)據(jù)。

移位寄存器的一個應(yīng)用是串行和并行之間的數(shù)據(jù)轉(zhuǎn)換,或串行的并行轉(zhuǎn)換。

移位寄存器分別標(biāo)識為SIPO,SISO,PISO,PIPO,或者作為通用移位寄存器,所有功能組合在一個設(shè)備中。

在關(guān)于順序邏輯電路的下一個教程中,我們將看看當(dāng)移位寄存器中的最后一個觸發(fā)器的輸出直接連接到第一個翻轉(zhuǎn)的輸入時會發(fā)生什么。翻牌產(chǎn)生一個閉環(huán)電路,不斷循環(huán)循環(huán)數(shù)據(jù)。然后產(chǎn)生另一種稱為環(huán)形計數(shù)器的順序邏輯電路,用作十進制計數(shù)器和分頻器。

-

寄存器

+關(guān)注

關(guān)注

31文章

5359瀏覽量

120793 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7102瀏覽量

89282 -

二進制

+關(guān)注

關(guān)注

2文章

795瀏覽量

41701 -

邏輯

+關(guān)注

關(guān)注

2文章

833瀏覽量

29486

發(fā)布評論請先 登錄

相關(guān)推薦

線性移位寄存器

移位寄存器的工作原理是什么?

移位寄存器實驗報告_移位寄存器原理

移位寄存器的特點_移位寄存器工作原理

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

移位寄存器的原理

移位寄存器的種類與作用

不同移位寄存器基本數(shù)據(jù)輸入/輸出摘要

不同移位寄存器基本數(shù)據(jù)輸入/輸出摘要

評論