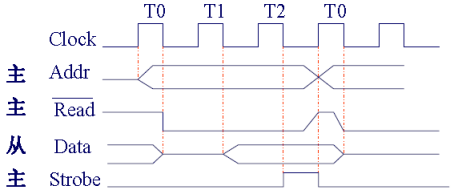

(1) 同步方式

?發送、接收雙方統一步調,具備統一的時鐘信號。?完全由同步時鐘確定收發時刻,沒有應答信號。?例:總線的讀操作

(2) 異步方式

?發送、接收雙方根據自身的工作速度來確定總線傳送的步調?沒有統一的時鐘信號,有主同步MSYN和從同步SSYN

?MSYN上升沿:主設備啟動輸入?SSYN上升沿:從設備已將數據準備好;?MSYN下降沿:主設備已將數據取走;?SSYN下降沿:從設備讓出數據總線?特點:各設備以自身需要的速度工作,時間利用率高。

·事件C: Ssyn↑→Msyn↓

·事件R: Msyn↓ → Ssyn ↓

·全互鎖:有C且有R

·半互鎖:或有C、或有R

(3) 準同步方式在完全同步方式中加一點異步的手段。有同步時鐘,也有應答信號線。同步地采樣應答信號

總線操作方式

微機系統各部件之間的信息交換是通過總線操作周期完成的,一個總線周期通常分為以下四個階段。

① 總線請求和仲裁階段:當有多個模塊提出總線請求時,必須由仲裁機構仲裁,確定將總線的使用權分配給哪個模塊。

② 尋址階段:取得總線使用權的模塊,經總線發出本次要訪問的存儲器或I/O端口的地址和有關命令。

③ 傳送數據階段:主模塊(指取得總線控制權的模塊)與其他模塊之間進行數據的傳送。

④ 結束階段:主模塊將有關信息從總線上撤除,主模塊交出對總線的控制權。

-

FPGA

+關注

關注

1629文章

21744瀏覽量

603660 -

時序

+關注

關注

5文章

388瀏覽量

37343

原文標題:總線的操作時序和操作方式詳解

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SSH遠程操作的基本方式

vim的操作方式有哪幾種

將TLV320ADCx120和PCMx120-Q1作為音頻總線控制器進行配置和操作

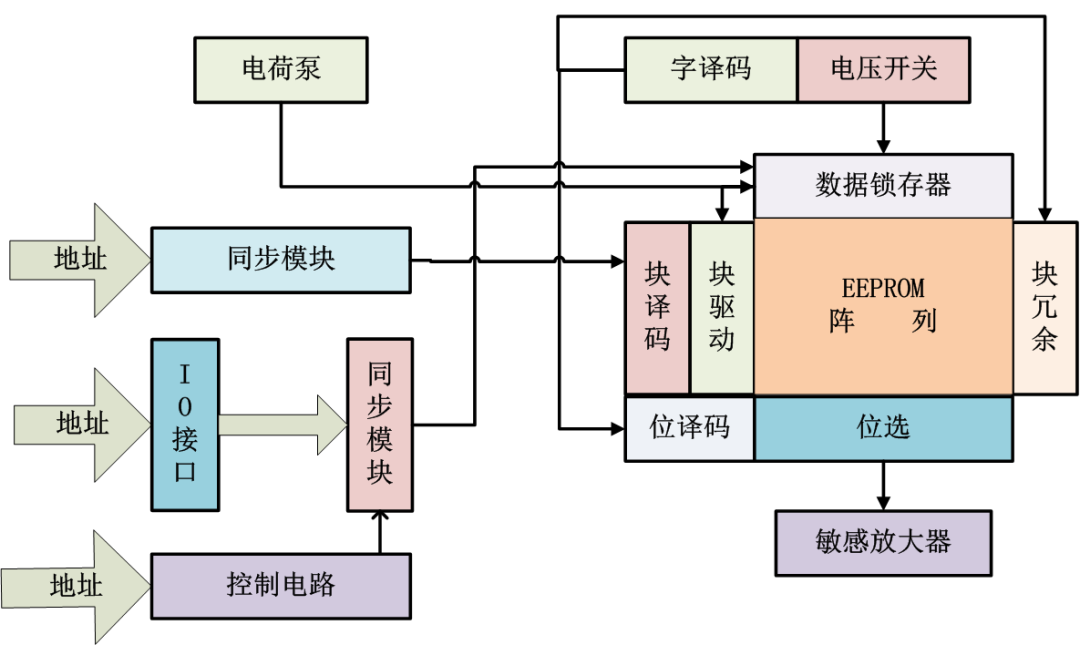

DRAM內存操作與時序解析

異步總線中傳送操作的控制機制

TSMaster 中不同總線報文消息過濾的操作方式

STM32H7 FMC操作SDRAM讀比寫慢很多是為什么?

TSMaster 總線記錄功能操作指南

總線的操作時序和操作方式詳解

總線的操作時序和操作方式詳解

評論