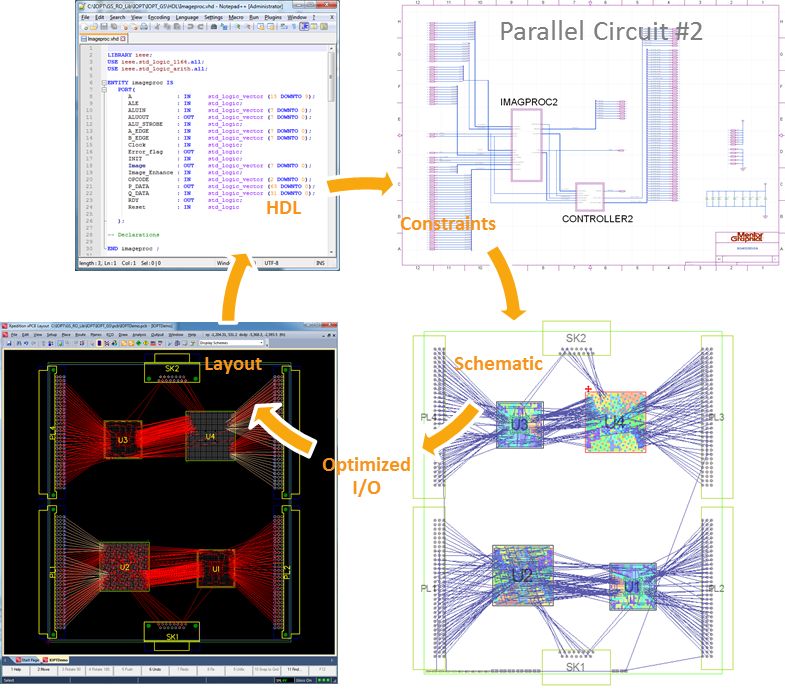

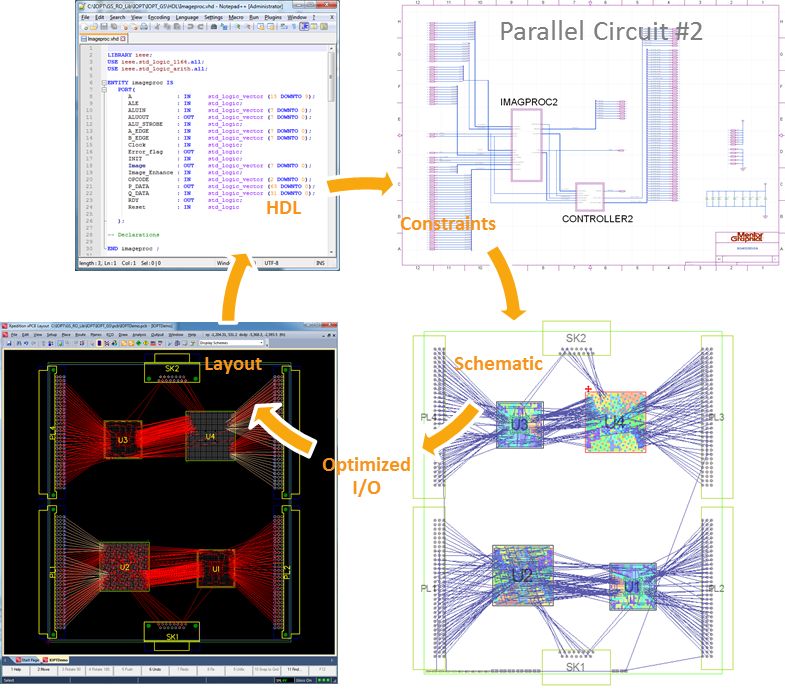

隨著電子產(chǎn)品的集成性及復(fù)雜度呈指數(shù)型增長,加上越來越苛刻的研發(fā)周期要求,給各種設(shè)計公司提出了難題。這其中FPGA的設(shè)計挑戰(zhàn)尤為突出。不斷增加的管腳數(shù)量,同一PCB上的多顆FPGA之間互連等等,面對這些挑戰(zhàn)如果還依照以往的手動式設(shè)計流程,勢必會在激烈的市場競爭中失去優(yōu)勢!Mentor公司針對這種實際應(yīng)用情況,提出了集成式管腳優(yōu)化方案,根據(jù)信號連接關(guān)系及器件位置擺放信息,自動實現(xiàn)IO管腳優(yōu)化,在保證產(chǎn)品質(zhì)量的前提下,高效完成FPGA設(shè)計及優(yōu)化工作,在最短的時間內(nèi)使產(chǎn)品順利上市!

4大技術(shù)優(yōu)勢:

1縮減設(shè)計成本:

減少過孔數(shù)量

節(jié)省PCB疊層數(shù)量

減少生產(chǎn)制造迭代次數(shù)

2縮短設(shè)計周期:

減少設(shè)計迭代次數(shù)

提升FPGA布線效率

快速優(yōu)化IO管腳,自動生成器件symbol

3減少設(shè)計失誤:

杜絕器件symbol設(shè)計失誤

避免手動更換IO管腳而造成的失誤

4提高產(chǎn)品質(zhì)量:

減少布線長度,提升信號質(zhì)量

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標題:不容錯過的研討會 | 復(fù)雜FPGA高效設(shè)計及優(yōu)化方法

文章出處:【微信號:gh_1a93bb3ab6f3,微信公眾號:Mentor明導(dǎo)PADS】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

焊接是現(xiàn)代制造業(yè)中不可或缺的一部分,廣泛應(yīng)用于建筑、汽車、航空、船舶等領(lǐng)域。隨著科技的發(fā)展,對焊接技術(shù)的要求越來越高,優(yōu)化焊接流程顯得尤為重要。 1. 焊接工藝的優(yōu)化 1.1 選擇合適的焊接方法

![的頭像]() 發(fā)表于

發(fā)表于 01-19 13:52

?227次閱讀

使用RISC-V進行高效數(shù)據(jù)處理的方法涉及多個方面,包括處理器內(nèi)核與DSA(領(lǐng)域特定加速器)之間的通信優(yōu)化、內(nèi)存管理優(yōu)化、多線程性能提升等。以下是一些具體的

![的頭像]() 發(fā)表于

發(fā)表于 12-11 17:52

?430次閱讀

我們在比較FPGA的芯片參數(shù)時經(jīng)常說某一款FPGA是多少萬門的,也有的說其有多少個LE,那么二者之間有何關(guān)系呢?

FPGA等效門數(shù)的計算方法有兩種,一是把

![的頭像]() 發(fā)表于

發(fā)表于 11-11 09:45

?358次閱讀

優(yōu)化FPGA(現(xiàn)場可編程門陣列)設(shè)計的性能是一個復(fù)雜而多維的任務(wù),涉及多個方面和步驟。以下是一些關(guān)鍵的優(yōu)化策略: 一、明確性能指標 確定需求 :首先,需要明確

![的頭像]() 發(fā)表于

發(fā)表于 10-25 09:23

?431次閱讀

本文描述了一種簡單高效配置FPGA的方法,該方法利用微處理器從串行外圍接口(SPI)閃存配置FPGA設(shè)備。這種

![的頭像]() 發(fā)表于

發(fā)表于 10-24 14:57

?753次閱讀

AI大模型的性能優(yōu)化是一個復(fù)雜而關(guān)鍵的任務(wù),涉及多個方面和策略。以下是一些主要的性能優(yōu)化方法: 一、模型壓縮與優(yōu)化 模型蒸餾(Model D

![的頭像]() 發(fā)表于

發(fā)表于 10-23 15:01

?889次閱讀

引言由于芯片設(shè)計復(fù)雜度的提升、集成規(guī)模的擴大,以及產(chǎn)品上市時間要求的縮短,使得設(shè)計驗證變得更加困難。特別是在多FPGA環(huán)境中,設(shè)計調(diào)試和驗證的復(fù)雜性進一步增加,傳統(tǒng)的調(diào)試手段難以滿足對高性能、

![的頭像]() 發(fā)表于

發(fā)表于 10-09 08:04

?788次閱讀

,FPGA 也需要不斷適應(yīng)和改進。研究人員和開發(fā)者將致力于針對 FPGA 的特點對深度學(xué)習(xí)算法進行優(yōu)化,例如探索更高效的模型壓縮方法、量化技

發(fā)表于 09-27 20:53

在FPGA(現(xiàn)場可編程門陣列)設(shè)計中,消除時鐘抖動是一個關(guān)鍵任務(wù),因為時鐘抖動會直接影響系統(tǒng)的時序性能、穩(wěn)定性和可靠性。以下將詳細闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從

![的頭像]() 發(fā)表于

發(fā)表于 08-19 17:58

?1550次閱讀

減少錯誤并更容易調(diào)試。然而,經(jīng)常出現(xiàn)的問題是性能權(quán)衡。在高度復(fù)雜的 FPGA 設(shè)計中實現(xiàn)高性能需要手動優(yōu)化 RTL 代碼,而這對于HLS開發(fā)環(huán)境生成的 RTL 代碼來說是不可能的。然而,存在一些解決方案

發(fā)表于 08-16 19:56

在FPGA(現(xiàn)場可編程門陣列)中實現(xiàn)狀態(tài)機是一種常見的做法,用于控制復(fù)雜的數(shù)字系統(tǒng)行為。狀態(tài)機能夠根據(jù)當(dāng)前的輸入和系統(tǒng)狀態(tài),決定下一步的動作和新的狀態(tài)。這里,我們將詳細探討如何在FPGA設(shè)計中實現(xiàn)狀態(tài)機,包括其基本概念、類型、設(shè)

![的頭像]() 發(fā)表于

發(fā)表于 07-18 15:57

?681次閱讀

FPGA(現(xiàn)場可編程門陣列)在處理異步信號時,需要特別關(guān)注信號的同步化、穩(wěn)定性以及潛在的亞穩(wěn)態(tài)問題。由于異步信號可能來自不同的時鐘域或外部設(shè)備,其到達時間和頻率可能不受FPGA內(nèi)部時鐘控制,因此處理起來相對復(fù)雜。以下是對

![的頭像]() 發(fā)表于

發(fā)表于 07-17 11:10

?1229次閱讀

這種高帶寬的互聯(lián)做了設(shè)計和優(yōu)化,更是在FPGA上集成了NOC,跟傳統(tǒng)FPGA中的routing有很大的區(qū)別,這也讓我們在復(fù)雜設(shè)計中可以減少因為Congestion導(dǎo)致的各種問題,減少代

發(fā)表于 04-24 15:09

功能,從而實現(xiàn)對數(shù)字電路的高效定制。FPGA語言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,這些語言具有強大的描述能力,能夠精確地定義硬件的每一個細節(jié),從而實現(xiàn)復(fù)雜

![的頭像]() 發(fā)表于

發(fā)表于 03-15 14:50

?985次閱讀

成本具有重要意義。

設(shè)計優(yōu)化:書中對FPGA加速器的技術(shù)進行了優(yōu)化,例如循環(huán)平鋪和轉(zhuǎn)換,并通過定量分析計算吞吐量和片內(nèi)外I/O帶寬,幫助讀者理解如何設(shè)計出更高效的加速器硬件參數(shù)。

實際

發(fā)表于 01-31 21:14

復(fù)雜FPGA高效設(shè)計及優(yōu)化方法

復(fù)雜FPGA高效設(shè)計及優(yōu)化方法

評論