1XDF(賽靈思開發(fā)者大會(huì))在北京國際飯店舉行。作為業(yè)界最權(quán)威、最具深度的FPGA交流大會(huì)之一,Xilinx把行業(yè)最頂尖的FPGA專家和企業(yè)匯聚一堂,集思廣益,分享和交流FPGA產(chǎn)品開發(fā)經(jīng)驗(yàn)與應(yīng)用方案,為業(yè)內(nèi)軟硬件開發(fā)者與設(shè)計(jì)者提供獨(dú)到的見解和靈感。Xilinx CEO Victor Peng 、華為IT智能計(jì)算業(yè)務(wù)副總裁張小華、阿里云FPGA異構(gòu)計(jì)算研發(fā)總監(jiān)張振祥等業(yè)內(nèi)領(lǐng)袖出席。同時(shí),在會(huì)上,賽靈思推出了業(yè)界首款自適應(yīng)計(jì)算加速平臺(tái)Versal和加速器Alveo,引爆現(xiàn)場。

作為Xilinx在中國智能汽車電子領(lǐng)域唯一的Certified member,深圳市自行科技有限公司(簡稱:自行科技)受邀參加,公司聯(lián)合創(chuàng)始人兼CTO諶璟博士在現(xiàn)場分享了“基于FPGA的計(jì)算機(jī)視覺系統(tǒng)設(shè)計(jì)與開發(fā)”的主題演講。諶璟博士結(jié)合其多年的深度學(xué)習(xí)與FPGA開發(fā)經(jīng)驗(yàn),從性能、成本、開發(fā)難度等多個(gè)維度出發(fā),提出一套系統(tǒng)化的FPGA深度神經(jīng)網(wǎng)絡(luò)優(yōu)化流程,受到了Xilinx AI及邊緣計(jì)算產(chǎn)品營銷總監(jiān)Nick與機(jī)器學(xué)習(xí)產(chǎn)品營銷高級(jí)經(jīng)理Andy等業(yè)內(nèi)專家的高度贊賞。

圖文:自行科技聯(lián)合創(chuàng)始人兼CTO諶璟博士做主題演講

諶博認(rèn)為,CNN與FPGA的結(jié)合可以組合利用多種算法模塊,充分發(fā)揮FPGA在計(jì)算速度、功耗、成本等方面的優(yōu)勢,降低開發(fā)難度與周期,減少開發(fā)成本。但是CNN中存在大量冗余計(jì)算,因此如何在FPGA中實(shí)現(xiàn)CNN加速設(shè)計(jì)就尤為重要。

諶璟博士演講獲得現(xiàn)場嘉賓觀眾一致好評(píng)

自行科技通過多年CNN與FPGA自主研發(fā)經(jīng)驗(yàn),開發(fā)出業(yè)內(nèi)最具性價(jià)比的FPGA加速設(shè)計(jì)方案。會(huì)中,她表示,F(xiàn)PGA加速設(shè)計(jì)需要算法工程師和FPGA工程師共同參與。一方面,通過剪枝壓縮、權(quán)值壓縮等方法對(duì)網(wǎng)絡(luò)壓縮算法進(jìn)行優(yōu)化,以減少網(wǎng)絡(luò)冗余計(jì)算,釋放可用資源。例如,我們可以僅僅將少數(shù)“重要”的卷積核量化為8bit權(quán)值,其余卷積核用1bit權(quán)值表示,構(gòu)造混合精度網(wǎng)絡(luò),在確保網(wǎng)絡(luò)檢測性能的基礎(chǔ)上大幅度提高計(jì)算效率。另一方面,不同的FPGA架構(gòu)需要適配對(duì)應(yīng)的CNN網(wǎng)絡(luò)結(jié)構(gòu),因此需要有針對(duì)性地進(jìn)行并行化和結(jié)構(gòu)化設(shè)計(jì),讓計(jì)算模塊得到充分利用,避免大量計(jì)算資源閑置。同時(shí),在進(jìn)行網(wǎng)絡(luò)設(shè)計(jì)時(shí)還要充分利用FPGA片內(nèi)資源,避免DSP計(jì)算資源與邏輯資源的浪費(fèi)。

以SSD網(wǎng)絡(luò)為例,在不考慮其他操作帶來的時(shí)延(DDR時(shí)延、FSM狀態(tài)轉(zhuǎn)移時(shí)延~等)的情況下,Xilinx zynq7020在CNN計(jì)算幀率最高可達(dá)5.7fps;但是,自行科技通過權(quán)值壓縮、并行化設(shè)計(jì)等CNN網(wǎng)絡(luò)加速設(shè)計(jì)和算法優(yōu)化后,計(jì)算幀率提升了4-5倍,大大提高了芯片的運(yùn)行效率,成為了業(yè)內(nèi)低成本高效率FPGA應(yīng)用典范!

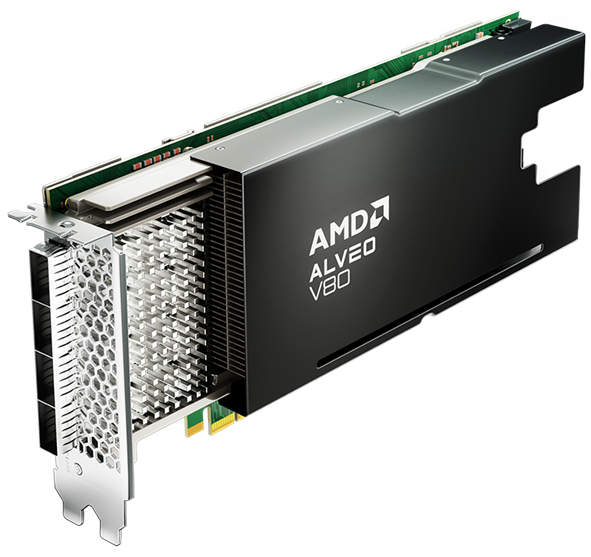

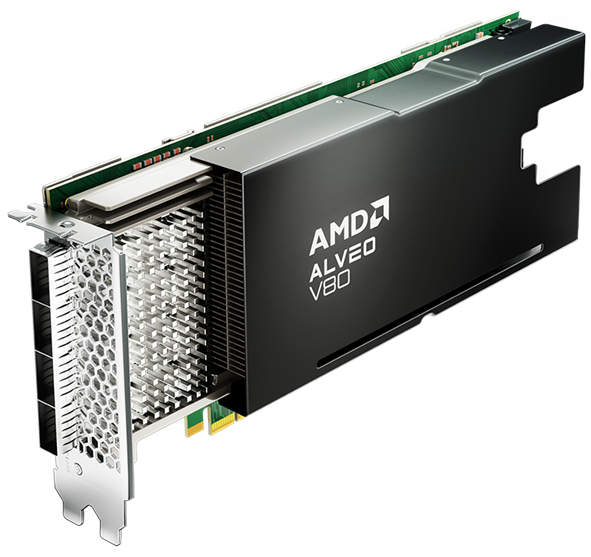

最后,諶博總結(jié)到:“FPGA與CNN的結(jié)合具備廣泛的應(yīng)用前景,但是在開發(fā)的過程中也需要我們不斷克服困難和挑戰(zhàn)。當(dāng)前FPGA平臺(tái)技術(shù)與工具不斷迭代更新,這就需要我們時(shí)刻關(guān)注世界最前沿的技術(shù)。今天我非常高興在現(xiàn)場見證了業(yè)界首款自適應(yīng)計(jì)算加速平臺(tái)Versal ACAP以及新一代FPGA加速器卡Alveo。這不僅可以加快公司軟硬件迭代創(chuàng)新進(jìn)程,還為我們探索更優(yōu)秀的FPGA加速方案提供了思路。未來,隨著CNN的計(jì)算量不斷上升,數(shù)據(jù)吞吐量也會(huì)顯著增大,這就需要不斷提高FPGA片內(nèi)BRAM資源利用效率,深入研究CNN模型壓縮算法,優(yōu)化基于FPGA的CNN框架,這也需要行業(yè)共同的努力!”

目前,該方案已經(jīng)成功應(yīng)用于公司的三大產(chǎn)品:前向ADAS系統(tǒng)、駕駛員監(jiān)控(DMS)系統(tǒng)和智能環(huán)視影像系統(tǒng),產(chǎn)品都已順利實(shí)現(xiàn)量產(chǎn)。基于FPGA平臺(tái)與CNN算法的深度結(jié)合,自行科技率先開發(fā)出國內(nèi)首款基于深度學(xué)習(xí)技術(shù)的駕駛員監(jiān)控(DMS)系統(tǒng),打造出業(yè)內(nèi)功能最全面、性價(jià)比最高的駕駛員監(jiān)控(DMS)系統(tǒng),成為國內(nèi)駕駛員監(jiān)控系統(tǒng)標(biāo)桿企業(yè)。

除此之外,自行科技前向ADAS系統(tǒng)與智能環(huán)視影像系統(tǒng)以其可靠的目標(biāo)檢測準(zhǔn)確性和語義分割精度獲得國內(nèi)眾多傳統(tǒng)車廠(乘用車與商用車)、新能源和互聯(lián)網(wǎng)造車公司和Tier1汽車零部件供應(yīng)商的高度認(rèn)可。相信隨著FPGA開發(fā)技術(shù)的不斷成熟,CNN加速設(shè)計(jì)將獲得更廣泛的應(yīng)用,讓我們拭目以待!

-

監(jiān)控系統(tǒng)

+關(guān)注

關(guān)注

21文章

3939瀏覽量

175850 -

高效率

+關(guān)注

關(guān)注

0文章

32瀏覽量

10457 -

異構(gòu)計(jì)算

+關(guān)注

關(guān)注

2文章

102瀏覽量

16317

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD Alveo V80計(jì)算加速器網(wǎng)絡(luò)研討會(huì)

貿(mào)澤開售適用于高性能計(jì)算應(yīng)用的AMD Alveo V80加速器卡

ALINX受邀參加AMD自適應(yīng)計(jì)算峰會(huì)

集成32GB HBM2e內(nèi)存,AMD Alveo V80加速卡助力傳感器處理、存儲(chǔ)壓縮等

PMP22165.1-適用于 Xilinx 通用自適應(yīng)計(jì)算加速平臺(tái) (ACAP) 的電源 PCB layout 設(shè)計(jì)

借助全新 AMD Alveo? V80 計(jì)算加速卡釋放計(jì)算能力

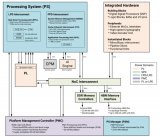

在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺(tái)示例設(shè)計(jì)流程

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺(tái)之PL通過NoC讀寫DDR4實(shí)驗(yàn)(4)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺(tái)之PL LED實(shí)驗(yàn)(3)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺(tái)PL LED實(shí)驗(yàn)(3)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之 Versal 介紹(2)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之準(zhǔn)備工作(1)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺(tái)之Versal介紹(2)

賽靈思推出了自適應(yīng)計(jì)算加速平臺(tái)Versal和加速器Alveo

賽靈思推出了自適應(yīng)計(jì)算加速平臺(tái)Versal和加速器Alveo

評(píng)論