本系列教學視頻由賽靈思高級戰略應用工程師帶領你從零開始,一步步深入掌握HLS 以及 UltraFAST 設計方法,幫助您成為系統設計和算法加速的大拿!

FOR 循環優化 — 循環合并 Lesson 16

在之前的課程我們介紹了了解 HLS 的入門,以及通過實例講解了 HLS 的工作原理和對不同數據類型的介紹和處理 ... ... 上節課我們介紹了 "FOR" 循環優化的一些基本性能指標。本節視頻,我們將繼續介紹 Vivado HLS 所支持的 “for循環” 的優化方法。在默認情況下,Vivado HLS 并不會對順序執行的 for 循環優化為并行執行,LOOP_MERGE 約束提供了這樣一種可能:for 循環并行執行。本講結合案例介紹了循環合并的三個主要規則。

專家介紹:

Lauren Gao,Xilinx 戰略應用高級工程師

專注于 C/C++ 高層次綜合,擁有多年利用 Xilinx FPGA 實現數字信號處理算法的經驗,對 Xilinx FPGA 的架構、開發工具和設計理念有深入的理解。發布網絡視頻課程《Vivado入門與提高》點擊率超過5萬、出版《基于FPGA的數字信號處理(第2版)》一書,并廣受好評。

往期課程

Lesson1:軟件工程師怎么了解 FPGA 架構

Lesson2:Vivado HLS 工作原理

Lesson3:HLS 設計流程 — 基本概念介紹

Lesson4:HLS 設計流程 - 實例演示

Lesson5:如何處理任意精度的數據類型

Lesson6:數據類型的轉換

Lesson7:了解 HLS 中的復合數據類型

Lesson8:Vivado HLS 中的 C/C++ 基本運算

Lesson9:Vivado HLS 下的 C/C++ 測試平臺的基本架構

Lesson10:描述高效的 C 測試平臺 - 測試激勵

Lesson11:描述高效的 C 測試平臺 - 輸出監測與格式控制

Lesson12:Vivado HLS 接口綜合 - 基本介紹

Lesson13:Vivado HLS 接口綜合 - 對數組的處理

Lesson14:Vivado HLS 接口綜合 - 其他案例演示

Lesson15:for循環優化 - 基本性能指標

原文標題:HLS教學視頻16:FOR 循環優化 — 循環合并

文章出處:【微信公眾號:賽靈思】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1629文章

21750瀏覽量

604106 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131322 -

C++

+關注

關注

22文章

2110瀏覽量

73695

發布評論請先 登錄

相關推薦

如何用matlab進行gamma可能性分析?

PSOC5LP與低通濾波器進行硬件連接的可能性有多大?

物聯網的諸多工業可能性

如何啟用在配置 -> Revup配置部分中輸入我自己的設置的可能性?

基于可能性計算模型的信息系統風險評估系統設計

廣義可能性模糊時態計算樹邏輯的模型檢測

for循環的執行流程

記憶黑板與智能手機或平板電腦同步的可能性與實現

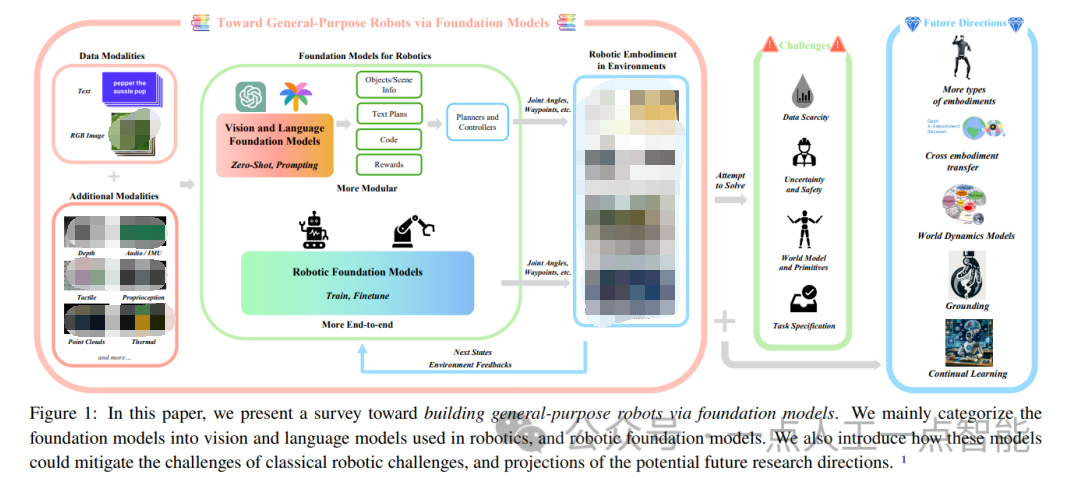

基礎模型能為機器人帶來怎樣的可能性?

for 循環并行執行的可能性

for 循環并行執行的可能性

評論