賽靈思 5 月 27 日宣布, 在其 UltraScale+ 全可編程器件發展藍圖上新增存儲器帶寬快車道(Xilinx 擴大 16nm UltraScale+ 產品路線圖為數據中心新增加速強化技術)。這種新型高速路由將 3D HBM(高帶寬存儲器)DRAM、大規模并行高帶寬接口和賽靈思最先進的 16nm UltraScale+ All Programmable 芯片完美集成在臺積公司 (TSMC) 和賽靈思聯合開發的 3D CoWoS 硅中介層 (3D on 3D) 上。賽靈思支持 HBM 的 UltraScale+ FPGA 結合臺積公司 (TSMC) CoWoS 硅中介層的高密度高性能互聯技術,能實現高達 Tbps 級的帶寬性能,相對于獨立封裝的 FPGA 和 SDRAM 而言,存儲器帶寬可提升高達 10 倍。將存儲器帶寬提升 10 倍的賽靈思加速增強型 16nm All Programmable 器件,將能夠滿足數據中心應用(尤其是云計算)的處理及存儲器帶寬要求。當日宣布的信息指出:“賽靈思已經在同業界領先的超大規模數據中心客戶協作,共同打造優化配置和產品。”

下面披露一些有關 HBM 和臺積公司 (TSMC) / 賽靈思聯合開發的硅中介層的技術細節

維基百科(Wikipedia)信息顯示,最初版 HBM 是 3D 協議棧 DRAM 器件陣列,由 AMD 和 SK Hynix 聯合開發,并于 2013 年成為 JEDEC 標準。將單位引腳的存儲器傳輸速率翻了一番的 HBM2 于2016 年 1 月成為 JEDEC 標準。三星僅在幾天后就宣布早期量產 HBM2 器件,而 SK Hynix則于 2016 年 3 月對 HBM2 器件進行了演示。所以 HBM 已經非常現實了。

SK Hynix HBM2提供的幻燈片對 HBM1 和 HBM2 進行了比較:

圖1:SK Hynix對 HBM1 和 HBM2 進行了對比

HBM 3D存儲器協議棧包括多個存儲器芯片和可選基礎邏輯芯片,它們通過硅通孔(TSV)連接在一起。一個 HBM 2 協議棧的存儲器帶寬據說超過 1Tbps,多個協議棧可集成到一個器件中。

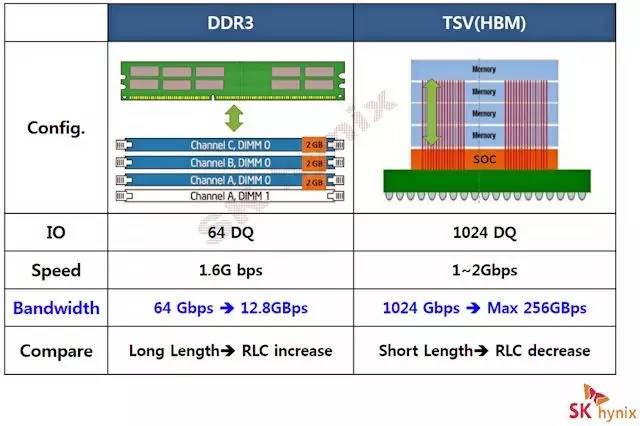

下面這張幻燈片對初始版 HBM 和 DDR3 SDRAM 進行了對比(摘自 2014 年熱芯片大會上的 SK Hynix 演示):

圖2:HBM 和 DDR3 比較,來自“HBM:適用于高帶寬要求處理器的存儲器解決方案” Joonyoung Kim和 Younsu Kim 在 2014 年熱芯片大會上的演示

您可看到,初始版 HBM 的存儲器帶寬相對于 DDR3 SDRAM 存儲器 Bank 而言提升了 10 多倍。

臺積公司 (TSMC) 和賽靈思聯合開發的 3D硅中介層技術現已正式稱為 CoWoS,并贏得北美 2013 年 SEMI 兩項大獎之一。SEMI 是“服務于微電子和納米電子產業生產供應鏈的全球產業協會”。

賽靈思基于 CoWoS 硅中介層技術的 16nm 器件是第三代 3D 器件。賽靈思第一代 3D 器件包括一系列基于 28nm 技術的 Virtex-7 FPGA:

Virtex-7 2000T All Programmable 3D IC:全球首款 3D FPGA,單個器件封裝,含有5 萬個邏輯單元。

Vrtex-7 H580T:全球首款異構 3D FPGA,采用 8 個 28Gbps收發器。

Virtex-7 H870T:全球第二款異構3D FPGA,采用 16 個 28Gbps 收發器,支持 400GE線路卡。

賽靈思第二代 3D 器件包括基于臺積公司(TSMC) 20nm 芯片技術、采用 440 萬個邏輯單元的 Virtex UltraScale VU440 3D FPGA。

今天宣布的消息稱賽靈思將擴展 3D 技術到16nm UltraScale+ 器件系列。您或許已經想到了,由于這是第三代技術,而且已經有兩代器件多批次投產供貨為基礎,因此

CoWoS 是非常牢靠的產品,而且也得到很好的了解和認知。

-

芯片

+關注

關注

456文章

50889瀏覽量

424301 -

存儲器

+關注

關注

38文章

7496瀏覽量

163932 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131309

發布評論請先 登錄

相關推薦

賽靈思宣布,在其發展藍圖上新增存儲器帶寬快車道

賽靈思宣布,在其發展藍圖上新增存儲器帶寬快車道

評論