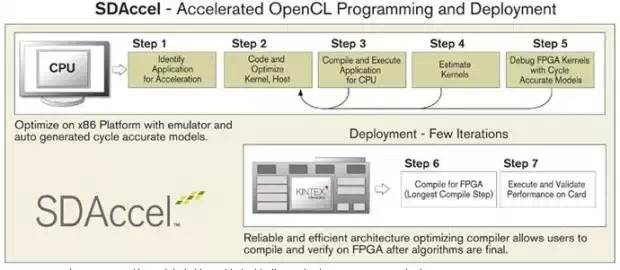

在賽靈思 SDSoC 開發(fā)環(huán)境發(fā)布前,標準 SoC 設計方法涉及一系列不同的工程設計技巧。通常來說,如果系統(tǒng)架構師根據要求生成系統(tǒng)架構和子系統(tǒng),那么解決方案的功能要分別實現在硬件(邏輯側)和軟件(處理器側)中。這樣,FPGA 和軟件工程師要分別開發(fā)各自的功能,再根據集成測試計劃進行組成和測試。這種方法持續(xù)運用了多年,但賽靈思 Zynq-7000 All Programmable SoC 以及即將推出的賽靈思 Zynq UltraScale+ MP-SoC 等功能更強的 SoC 的問世要求采用新的設計方法。

SDSoC 方法能幫助更廣泛的工程師用戶群開發(fā)極高性能系統(tǒng)。在 SDSoC 開發(fā)環(huán)境中進行開發(fā)的工程師新手會發(fā)現,可以輕松快速地啟動并運行系統(tǒng),而且系統(tǒng)優(yōu)化也同樣便捷。

我們舉一個簡單而具代表性的例子來說明如何完成上述任務并獲得相應的收益。我們針對的是運行 Linux 的 ZedBoard,并采用內置示例之一:矩陣乘法器和加法模板。

設計方法簡史

可編程邏輯器件自 1980 年推出以來一直迅速發(fā)展。起初,工程師通過原理圖輸入法對器件進行編程(雖然 22v10 等較早期的可編程邏輯器件 (PLD) 是通過邏輯方程編程的)。這需要電子工程師執(zhí)行大部分 PLD 開發(fā)工作,因為邏輯設計和優(yōu)化通常屬于電子工程學范疇。隨著器件尺寸和功能的不斷提升,這種原理圖輸入法自然開始面臨局限性問題,因為設計和驗證時間會隨著設計復雜性的增加而顯著延長。工程師需要具備在更高抽象層上工作的能力。

VHDL 和 Verilog 應運而生。二者開始都是用來描述和模擬邏輯設計(特別是 ASIC)的語言。VHDL 甚至有自己的軍用標準。既然我們要在硬件描述語言 (HDL) 中描述邏輯行為,那么自然應該綜合所需的邏輯電路。綜合工具的開發(fā)使得工程師能描述通常在寄存器傳輸層的邏輯行為。HDL 也能大幅改進驗證方法,有助于開發(fā)行為測試平臺,支持結構化驗證。HDL 也首次支持模塊化和廠商獨立性。

HDL 內在并行性、寄存器傳輸層設計法和實現流程則需要了解優(yōu)化和時序收斂,這就意味著 PLD 開發(fā)任務大部分落到了電子工程師的身上。

HDL 一直是 PLD 開發(fā)領域的事實標準,但多年發(fā)展中也考慮到整體產業(yè)的發(fā)展需求。單就 VHDL 而言,相繼于 1987 年(IEEE 采用的第一年)、1993 年、2000 年、2002 年、2007 年、2008 年進行了修訂。不過,跟原理圖輸入法一樣,HDL 也逐漸開始面臨一系列局限性問題,包括開發(fā)和驗證時間太長、器件功能要求提高等。

隨著 PLD 的角色從膠合邏輯向加速外設甚至最終向系統(tǒng)核心發(fā)展,業(yè)界需要新的設計方法來滿足有關發(fā)展需求。近年來,高層次綜合 (HLS) 越來越受歡迎。根據高層次綜合法,設計通過 C/C++(用賽靈思的 Vivado HLS)或其他工具(如 MathWorks 公司的 MATLAB 或國家儀器公司的 LabVIEW)輸入。由于新的設計方法能夠充分發(fā)揮器件的功能,這種方法開始將設計和實現從電子工程領域轉向軟件領域,從而顯著擴大了潛在的 PLD 設計人員群體,并鞏固了 PLD 作為系統(tǒng)核心的地位。

因此,SoC 設計自然能用 HLS 來生成緊密集成的開發(fā)環(huán)境,工程師則能在環(huán)境中無縫加速設計邏輯側功能。在此情況下,SDSoC 環(huán)境應運而生。

熟悉的環(huán)境

SDSoC 開發(fā)環(huán)境基于 Eclipse,大多數軟件開發(fā)人員對這種環(huán)境應該是比較熟悉的(圖1)。該環(huán)境通過采用能處理 C 或 C++ 程序的全新 SDSoC 編譯器無縫支持器件可編程邏輯 (PL) 側功能加速。

SDSoC環(huán)境中使用最高抽象層進行開發(fā),具體如下:

在 C 或 C++ 中開發(fā)應用。

對應用進行特性分析,明確性能瓶頸問題。

使用特性分析信息,明確器件 PL 側哪些功能需要加速。

隨后構建系統(tǒng)并生成 SD 卡映像。

硬件到位后,進一步分析性能并根據要求優(yōu)化加速功能。

我們能在 SDSoC 環(huán)境中開發(fā)出可在裸機、FreeRTOS 或 Linux 操作系統(tǒng)上運行的各種不同應用。該環(huán)境內置支持 ZedBoard、MicroZed 和 Digilent ZYBO 等大部分 Zynq SoC 開發(fā)板。這樣,我們不僅能加速開發(fā)應用,還能通過該功能定義自己的底層硬件平臺,在自己的定制硬件平臺能用于集成時使用。

在 SDSoC 環(huán)境中編譯程序時,構建過程輸出提供了從 SD 卡配置 Zynq SoC 所需的系列文件。該系列文件包括一級和二級引導載入程序,以及操作系統(tǒng)所需的應用和映像。

SDSOC 實例

下面我們看看 SDSoC 環(huán)境如何工作,多快就能讓實例啟動并運行起來。我們針對的 ZedBoard 開發(fā)板運行 Linux 操作系統(tǒng)并使用內置矩陣乘法器和加法模板。

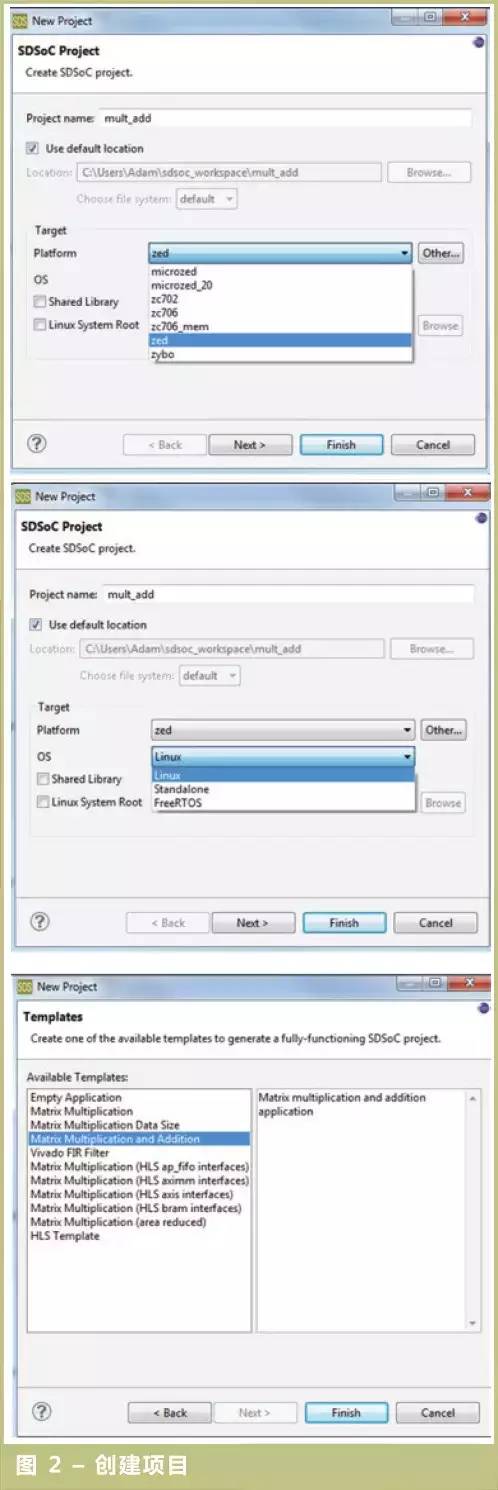

首先一如既往地創(chuàng)建項目。我們能通過歡迎窗口(圖 1)或通過菜單選擇“File -> New -> SDSoC”項目來創(chuàng)建項目。這兩種方法都能打開對話框,讓我們給項目命名,選擇開發(fā)板和操作系統(tǒng)(圖 2)。

這將在 SDSoC GUI 左側 Project Explorer 下生成項目。我們在該項目下會看到以下文件夾,每個文件夾都有自己唯一的圖標:

SDSoC 硬件功能:這里我們能看到轉移到硬件的功能。一開始這個文件夾是空的,等待我們轉移。

Includes:展開這個文件夾能看到構建過程中使用的所有 C/C++ 報頭文件。

src:包含演示用源代碼。

為確保我們正確配置所有事項,包括 SDSoC 安裝和環(huán)境以及開發(fā)板,我們要構建演示,其只在器件片上處理系統(tǒng) (PS) 側運行。

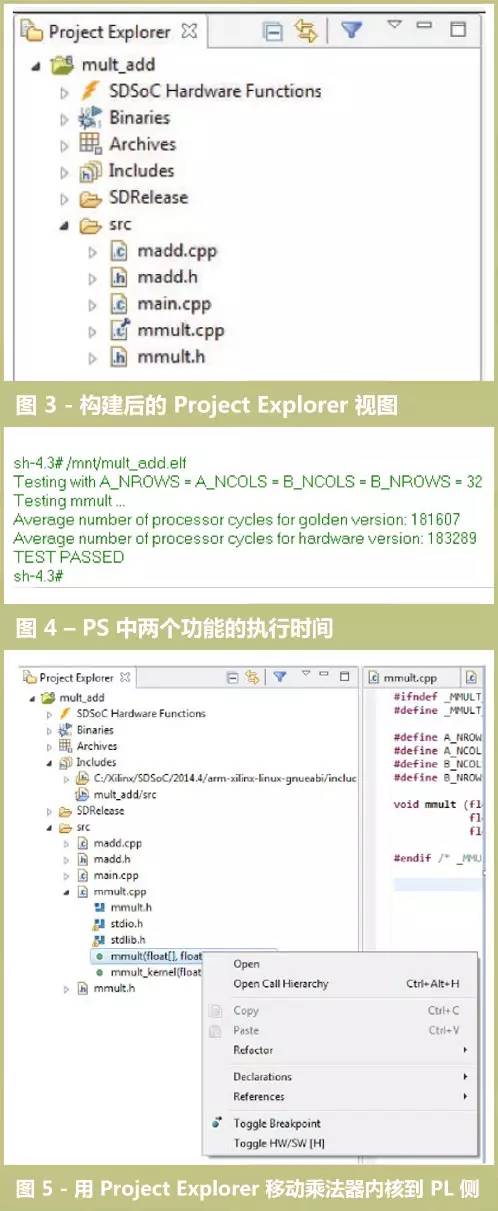

當然,下一步就是構建項目了。在菜單上選中項目,我們選擇“Project->Build Project”。構建時間不會太長。完成后,會看到如圖 3 所示的文件夾出現在 Project Explorer 中的項目下。除了上述文件夾之外,還有:

二進制文件:這里能找到軟件編譯過程生成的可執(zhí)行連接 (ELF) 文件。

歸檔:鏈接對象文件,創(chuàng)建其中的二進制文件。

SDRelease:包含我們的引導文件和報告。

我們已經構建了首個演示,只能在 Zynq SoC 的 PS 上運行,下面我們來看看如何確保其按預期正常運行。對應用進行特性分析,明確 SDSoC 加速運行。工程師用特性分析信息明確應該移動哪些功能。

我們用已提供的 sds_lib.h 庫在基本層面進行特性分析,這能在 64 位全局計數器上獲得基本時間戳 API,讓我們測出每個功能的用時。我們用API 能簡單記錄功能開始和停止時間,這一時間差就是整個過程的執(zhí)行時間。

源代碼包括兩個版本的矩陣乘法和加法算法。所謂的黃金版不用于轉移到片上可編程邏輯 (PL);另一版則針對這個目的。通過在 PS 中構建并運行,我們能確保有針對性地對比,而且兩個流程執(zhí)行時間基本相同。

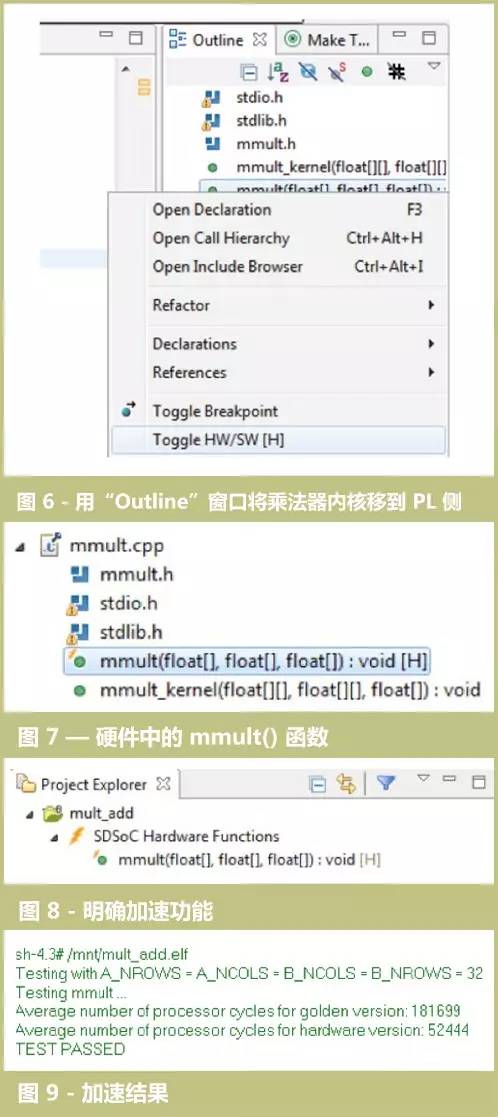

構建完成后,我們能拷貝“Project Explorer 下 SDRelease -> sd_card”文件夾中的所有文件到 SD 卡,然后將 SD 卡插到 ZedBoard 上(SD 卡配置的模式引腳要正確設置)。終端程序連接以及引導序列完成后,我們就要運行程序。輸入“/mnt/mult_add.elf”(這里的 mult_add 是我們創(chuàng)建的項目的名稱)。在 ZedBoard 上運行,得到如圖 4 所示的結果,顯示兩個功能運行的時間基本相同。

驗證執(zhí)行時間基本相同后,我們將乘法函數移到 SoC 的 PL 側,這步很容易實現。

分析實例中 src 目錄的文件結構,我們看到:

main.cpp:這包含主函數、黃金計算、時間戳和器件硬件側所用的乘法加法函數調用。

mmult.cpp:這包含在硬件部分運行的乘法函數。

madd.cpp:這包含在硬件部分運行的加法函數。

完成上述步驟后,下次構建項目時,SDSoC 鏈接器會自動調用賽靈思 Vivado HLS 和Vivado 來執(zhí)行 SoC 中 PL 側的功能。

下一步就是將一個函數轉移到 SoC 的 PL 側。我們通過以下兩種方法之一能完成這一任務:

在 Project Explorer 中,我們展開文件,看到文件中的函數,選擇感興趣的函數,右鍵點擊并選擇“Toggle HW/SW [H]”(圖5)。

打開文件并執(zhí)行右側“outline”標簽下的同樣選項,這也能顯示函數(圖 6)。

開關硬件中加速的 mmult() 函數能讓 [H] 添加到函數后面(圖 7)。

我們還會看到 SDSoC Hardware Functions 下選擇的功能(“Project Explorer”標簽中項目下方,圖 8)。這能讓我們方便地看到設計中加速的所有功能。

完成上述步驟后,下次構建項目時,SDSoC 鏈接器會自動調用賽靈思 Vivado HLS和Vivado Design Suite 其余部分來執(zhí)行 SoC 中 PL 側的功能。與此同時,會創(chuàng)建軟件驅動程序,支持功能加速。我們看到,功能轉移到器件 PL 側是無縫的,而且還會提高性能。

編譯和生成 SD 卡映像后,我將 mmult() 函數移到硬件,在 ZedBoard 上運行。如圖 9 所示,執(zhí)行時間(處理器工作循環(huán))只有 52,444 / 183,289 = 0.28,也就是此前期間 PS 側 183,289 個處理器工作循環(huán)(執(zhí)行時間)的 28%(圖 4)。考慮到器件 PS 側相同功能的性能,我們看到只需簡單點擊鼠標就能大幅改進執(zhí)行時間。

-

子系統(tǒng)

+關注

關注

0文章

109瀏覽量

12417 -

系統(tǒng)構架

+關注

關注

0文章

5瀏覽量

6253

發(fā)布評論請先 登錄

相關推薦

賽靈思表示將推出更多功能更強的設計方案

賽靈思表示將推出更多功能更強的設計方案

評論