UltraFast是Xilinx在2013年底推出的一套設計方法學指導,旨在指引用戶最大限度地利用現有資源,提升系統性能,降低風險,實現更快速且可預期的設計。面向Vivado的UltraFast方法學的主體是UG949文檔,配合相應的Checklist,隨Vivado版本同時更新,用戶可以在Xilinx的主頁上免費下載。目前,針對Vivado設計套件的UltraFast中文版也已經上市,另外一套全新的針對嵌入式可編程設計的UltraFast嵌入式設計方法指南UG1046也已經在Xilinx官網上開放下載。

盡管UltraFast這個字眼經常在網上看到,不論官方還是其他媒體上說起Vivado設計套件時也常常提到,但很多用戶仍然對這個概念十分模糊,有不少人下載文檔后看到300頁的PDF頓時也失去了深入學習和了解的興趣。

適逢《Vivado使用誤區與進階》系列連載半年多,大部分預先列好的主題也都已經按照計劃完成,我們準備把這些短文集結為一本電子書,方便更多讀者隨手翻閱或是必要時用作設計參考。借此機會,套用在Xilinx內部被譽為 “Vivado之父”的產品營銷總監 Greg Daughtry在去年第一屆Club Vivado中所提出的 “時序收斂十大準則” 的概念,試著用十分鐘的篇幅來概括一下什么是UltraFast,以及怎樣利用UItraFast真正幫助我們的FPGA設計。

時序設計的十大準則,基本上也涵蓋了UltraFast設計方法指南的基本要點。UG949中將FPGA設計分為設計創建、設計實現和設計收斂幾大部分來討論,除了介紹所有可用的設計方法和資源,更多的是一些高級方法學技巧,這些技巧基本上都跟時序收斂有關或是以時序收斂為目標,有些通用的方法和技巧甚至脫離了具體選用的FPGA器件的限制,適用于更廣泛意義上的時序收斂。

最寶貴的是,所有這些UltraFast設計方法學技巧都來自一線技術支持人員的經驗以及客戶的反饋,是業界第一本真正意義上完全面向用戶的指南,這一點只要你試著讀過一兩節UG949就會有明顯感覺,所有其中提到的技巧和方法都具有很高的可操作性,可以帶來立竿見影的效果。

接下來我們就由這十大準則展開,帶領各位讀者在十分鐘內理清UltraFast方法學的脈絡,一探其究竟。

準則一:合適的代碼風格

理想環境下,源代碼可以獨立于最終用于實現的器件,帶來最佳的可移植性和可復用性。但是,底層器件各自獨特的結構,決定了通用代碼的效率不佳,要最大化發揮硬件的性能,必然需要為實現工具和器件量身定制代碼。

關于Xilinx器件和Vivado適用的代碼風格,我們有以下建議:

準則二:精準的時序約束

精準的時序約束是設計實現的基礎,對時序驅動工具Vivado來說,約束就是最高指示,是其努力實現的目標。很多時候我們發現,約是有經驗的工程師約是喜歡用一些舊有經驗套用在Vivado上,例如很多人偏愛用過約束的方式來追求更高的性能,但實際上對Vivado來說,大部分的過約束只會阻礙時序收斂。

簡要概括而言,精簡而準確的約束是時序收斂的必要條件,而UltraFast中提出的Baseline基線方法則是充分條件。

具體的約束方法我們在《XDC約束技巧》中有詳細討論,除了保證語法正確,還要注意設置XDC約束的順序,通常第一次運行時只需要約束所有時鐘,然后在內部路徑基本滿足時序約束的情況下加入關鍵I/O的約束,其次再考慮必要的時序例外約束。

所有這些約束都必須遵循精簡而準確的原則,且可以借助Vivado中的XDC Templates以及Timing Constraint Wizard的幫助來進行。

Baseline基線方法可以說是UltraFast的靈魂部分,強烈建議所有Vivado的用戶都能精讀UG949中的這部分內容,并將之應用在具體的設計中。有機會我會深入展開一篇專門介紹Baseline方法的短文,這里先將其核心的概念做一個總結。

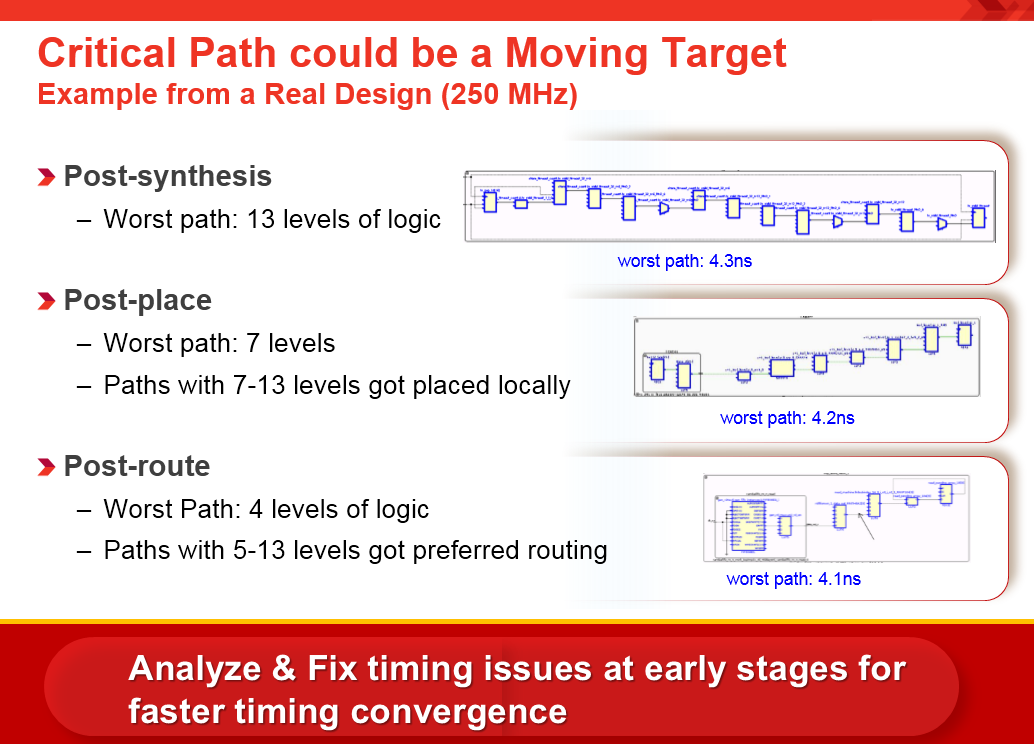

上圖展示了同一個設計在三個不同階段用同樣的命令報告時序所得到的最差路徑,可以清晰的看出,即使不做任何源代碼上的改動,設計中真正最差的路徑已經不會作為最差路徑出現在布局布線后的報告中。這正是因為Vivado時序驅動的天性決定了其在設計實現的每一步都是以開始時讀到的設計輸入和約束為依據,盡量將最好的資源用在最差的路徑上,從而盡最大可能實現時序收斂。

這便是Baseline理論的基礎,除了按順序設置精準的時序約束,在設計實現的每一步,用戶都需要關注時序報告,并以其為依據來調整設計源代碼或是應用其他必要的約束和選項來優化設計。保證每一階段之后的時序報告都滿足約束或是僅余300ps以內的時序違例,再進入下一階段的設計實現過程,否則,應該繼續在當前階段或是退回到上一階段調整后重跑設計,直到滿足要求再繼續。

越早發現和定位問題,越是可以通過少量的努力來達到更大范圍的改進。

準則三:管理高扇出網絡

高扇出網絡幾乎是限制FPGA設計實現更高性能的第一大障礙,所以我們需要很嚴肅地對待設計中的高扇出網絡。

很多人會陷入一個誤區,反復糾結到底多大的扇出值算是大?其實這一點不是絕對的,在資源充裕時序要求不高的情況下幾千甚至上萬都不算大,反之在局部關鍵路徑上僅有幾十的扇出也可能需要進一步降低。

在Vivado中,我們除了關注時序報告,尤其是布局后布線前的報告來定位關鍵路徑上影響時序的高扇出網絡外,還有一個專門的命令report_high_fanout_nets ,在給其加上 -timing的選項后,可以在報告高扇出路徑的同時報告出這條路徑的Slack,幫助用戶直觀了解當前路徑的時序裕量。此外,這個命令在報告中還會指出高扇出網絡的驅動類型,是FF或是LUT等。

找到目標后,可以利用max_fanout來限定其扇出值,讓工具在實現過程中復制驅動端寄存器來優化。如果高扇出網絡并不是由同步邏輯來驅動,則可能需要修改代碼。還有一些工具層面上的降扇出方法,比如選擇更強更有針對性的策略,或是允許多次物理優化phys_opt_design,甚至是通過我們在《用Tcl定制Vivado設計實現流程》中提到的“鉤子”腳本等方式來進行局部降扇出的物理優化等等。

但有一點需要注意,Vivado綜合選項中的全局扇出限定要慎用 ,不要將其設置的過低以免綜合出的網表過于龐大,帶來資源上的浪費,并可能導致局部擁塞。

準則四:層次化設計結構

隨著設計規模的不斷擴大,以及SoC設計的興起,越來越多的IP被整合到大設計中,曾經為高性能設計而生,便于統一管理和控制的自頂向下的設計流程變得不再適用,FPGA設計也跟大規模SoC設計一樣,需要采用層次化的設計流程,即自底向上的流程。這也要求設計者在源代碼階段就考慮到最終的實現,處理好模塊的層次邊界。

Vivado中的IP設計是原生的自底向上流程,用戶可以將IP生成獨立的DCP再加入到頂層設計中去。我們也鼓勵用戶將某些相對固定或獨立的模塊綜合成DCP后加入頂層設計,這么做除了加快設計迭代外,也更利于設計開始階段的調試和問題的定位。

Vivado中的OOC模式甚至還支持完全層次化的設計,即將底層模塊的布局布線結果也進行復用,這么做雖然流程復雜,卻帶來了更全面的控制性,也是部分可重配置技術的實現基礎。

準則五:處理跨時鐘域設計

FPGA設計中通常都帶有跨時鐘域的路徑,如何處理這些CDC路徑非常重要。由于Vivado支持的約束標準XDC在處理CDC路徑上與上一代ISE中支持的UCF約束有本質區別,如何約束以及怎樣從設計上保證CDC路徑的可靠性就成了重中之重。

《XDC約束技巧之CDC篇》中對Vivado中的跨時鐘域設計有詳細描述,UG949中也有不少篇幅用來討論CDC路徑的各種設計技巧和約束方法。建議用戶深入學習和了解這部分的內容,其中有不少概念并不僅僅局限于FPGA設計中的跨時鐘域設計,放在其他IC設計上也一樣有效。

需要提醒大家的是,一定要利用好Vivado中的各種報告功能,例如report_cdc和DRC報告中的methodology_checks來檢測設計中的CDC結構問題,并作出具體的設計調整或是補全CDC約束。另外要注意各種不同的CDC路徑處理方法之間的優劣,選擇最適合自己設計的方式,配合相應的約束來保證跨時鐘域路徑的安全。

準則六:少而精的物理約束

不同于對時序約束尤其是時鐘約束之全面而精準的要求,Vivado對物理約束的要求只有一個字:少。這里的物理約束更多強調的是除了I/O引腳位置這些必要項之外的約束,例如對RAMB和DSP48的位置約束,還有局部的floorplan計劃。

很多資深工程師非常喜歡畫floorplan,因為其對設計的數據流和資源使用情況了如指掌,根據自己理解畫出的floorplan通常也算合理。但是,floorplan在Vivado中的重要性遠低于以往在ISE上的作用。根據客戶的實際經驗反饋,絕大多數的設計中都無需任何floorplan(某些時序要求較高的SSI芯片設計上可能需要),因為算法的改進,Vivado在布局上比上一代ISE更聰明,沒有任何物理約束(除了IO引腳位置約束)的設計反而能在更短的時間內更好地滿足時序要求。

在確實需要鎖定某些宏單元以及進行floorplan的設計中,一般我們會推薦先不加任何物理約束來跑設計,在其他諸如改進源代碼,設置約束和選項,改變策略等辦法都試過后,再嘗試物理約束。而且,最好只在少量關鍵的設計區域進行floorplan,切忌過度約束,不要創建資源利用率過高的pblocks,同時避免重疊的pblocks區域。

順便提一下,Vivado IDE中的Device視圖可以通過設置不同顏色來高亮顯示不同模塊,用戶可以根據當前設計的布局結果配合時序報告和關鍵路徑來創建和調整floorplan,操作非常便捷。

準則七:選擇實現策略

從ISE升級到Vivado后,很多用戶發現SmartXplorer功能不見了,當設計進行到后期,假如不能遍歷種子,常讓人感到無所適從,甚至懷疑到了這一步Vivado便無計可施。那么事實到底如何呢?

嚴格來講,Cost Table 其實是一種無奈之舉,說明工具只能通過隨機種子的改變來“撞大運”般篩選出一個最佳結果,這也解釋了為何改變Cost Table的結果是隨機的,一次滿足時序,并不代表一直可以滿足。

因為更高級算法的引入,Vivado中的設計實現變得更加可靠,而且是真正意義上的可預計的結果。但這并不代表在Vivado中對同一個設計進行布局布線只能有一種結果。我們可以通過“策略”來控制實現過程中的算法側重,從而可以產生更優化的結果。

策略(Strategy)是一組工具選項和各個階段指示(Directive)的組合,Vivado IDE中內置了幾十種可供用戶直接選用,但如果窮盡各種組合,整個實現過程大約有上千種策略。當然,我們沒必要遍歷每種策略。而且因為策略是一種可預計可重現的實現方法,所以對同一個設計,可以在選擇幾種有側重點的策略后挑選出效果最好的那個,只要設計后期沒有大的改動,便可一直延用同樣的策略。

具體策略的特性,請參考UG949和UG904等文檔,也可以在Vivado中通過help菜單了解。更多時候,選擇怎樣的策略是一種經驗的體現,另外,即使找到了最佳實現策略,也仍舊有可能不滿足時序要求,這時候我們還可以參考《用Tcl定制Vivado設計實現流程》中所述,對設計實現的流程進行進一步的個性化定制。

另外要強調一點,修改策略來提升性能必須放在調整代碼、約束和選項等更直接高效的優化方法之后進行,其能帶來的性能提升比起前述優化方法來說也更加局限。

準則八:共享控制信號

共享控制信號這一點充分體現了設計必須考慮到用于底層實現的芯片結構的重要性,在Xilinx的芯片上,時鐘、置位/復位和時鐘使能等信號通稱為Control Set,進入同一個SLICE的Control Set必須統一。換句話說,不同Control Set控制下的FFs不能被Vivado放進同一個SLICE。

為了提升SLICE的利用率,獲得更高效的布局方案,提升時序性能,我們必須控制一個設計中Control Set的總數,盡量共享控制信號。具體做法包括:

盡量整合頻率相同的時鐘和時鐘使能信號;

在生成IP時選擇“共享邏輯”功能,則可以在不同IP間盡可能的共享時鐘資源;

遵循Xilinx建議的復位準則:

盡量少使用復位

必須復位時采用同步復位

確保使用高電平有效的復位

避免異步復位(RAMB和DSP48模塊中不支持異步復位)

Xilinx的復位準則必須嚴格遵守,根據現場支持的經驗來看,很多設計性能的瓶頸就在于設計源代碼時沒有考慮底層實現器件的硬件結構特點,尤其以復位信號的實現問題最為突出。

準則九:讀懂日志和報告

任何一個工具的日志和報告都是衡量其性能最重要的一環,正因為有了完備的日志與報告,用戶才可以通過其中顯示的信息,定位設計中可能的問題,決定優化方向。

Vivado日志中將信息顯示為三大類,分別為Error、Critical Warning和一般Warning/Notes等。Error會導致工具直接中斷,其他警告不會中斷工具運行,但所有的Critical Warning都需要用戶逐一檢查并通過修改設計、增加約束或設置選項之類的辦法來修復。

Vivado的報告功能很強大,除了《讀懂用好Timing Report》中描述的時序分析報告,還有很多重要的報告,小到檢查設計中的特定時序元件和鏈路,大到各種預置和自定義的DRC檢查,不僅提供給了用戶多樣的選擇,也進一步保證了設計的可靠性。

Vivado也一直在增強和更新報告的種類,比如2014.3之后還增加了一個設計分析報告report_design_analysis,用來報告關鍵路徑上的潛在問題以及設計的擁塞程度。完整的report命令和功能可以在UG835中查詢。

準則十:發揮Tcl的作用

Tcl在Vivado中的作用不容小覷,不僅設計流程和報告全面支持Tcl腳本,就連XDC約束根本上也來自于Tcl,用戶甚至可以直接把包含有循環等功能的高級約束以Tcl的形式讀入Vivado中用來指引整個實現流程。

《Vivado使用誤區與進階》系列中有三篇關于Tcl在Vivado中的應用文章,詳細描述了如何使用Tcl創建和應用約束,查找目標和定位問題;如何用Tcl來定制Vivado的設計實現流程,為圖形化界面提供更多擴展支持;以及如何用Tcl實現ECO流程。Tcl所帶來的強大的可擴展性決定了其在版本控制、設計自動化流程等方面具有圖形化界面不能比擬的優勢,也解釋了為何高端FPGA用戶和熟練的Vivado用戶都更偏愛Tcl腳本。

另外,隨著Xilinx Tcl Store的推出,用戶可以像在App Store中下載使用app一樣下載使用Tcl腳本,簡化了Tcl在Vivado上應用的同時,進一步擴展了Tcl的深入、精細化使用。最重要的是,Tcl Store是一個基于GitHub的完全開源的環境,當然也歡迎大家上傳自己手中有用的Tcl腳本,對其進行補充。

小結

關于UltraFast的要點總結基本可以概括在上述十點,這也可以看作是對《Vivado使用誤區與進階》系列短文的一個串燒。

-

嵌入式系統

+關注

關注

41文章

3607瀏覽量

129599 -

代碼

+關注

關注

30文章

4808瀏覽量

68808 -

約束

+關注

關注

0文章

82瀏覽量

12748

發布評論請先 登錄

相關推薦

采用FPGA實現DisplayPort詳細教程【賽靈思內部資料】

面向未來十年 “All Programmable”器件 賽靈思發布Vivado設計套件

賽靈思客戶共賀Vivado 設計套件推出

賽靈思新一代Vivado設計套件首次面向公眾開放

賽靈思推出UltraFast幫助用戶學習Vivado

賽靈思推出UltraFast幫助用戶學習Vivado

評論