《XDC約束技巧之時鐘篇》中曾對I/O約束做過簡要概括,相比較而言,XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應用特性決定了其在接口上有多種構建和實現方式,所以從UCF到XDC的轉換過程中,最具挑戰的可以說便是本文將要討論的I/O約束了。

I/O約束的語法

XDC中可以用于I/O約束的命令包括set_input_delay / set_output_delay和set_max_delay / set_min_delay 。其中,只有那些從FPGA管腳進入和/或輸出都不經過任何時序元件的純組合邏輯路徑可以用set_max_delay / set_min_delay來約束,其余I/O時序路徑都必須由set_input_delay / set_output_delay來約束。如果對FPGA的I/O不加任何約束,Vivado會缺省認為時序要求為無窮大,不僅綜合和實現時不會考慮I/O時序,而且在時序分析時也不會報出這些未約束的路徑。

本文以下章節將會著重討論XDC接口約束和時序分析的基礎,介紹如何使用set_input_delay / set_output_delay對FPGA的I/O時序進行約束。

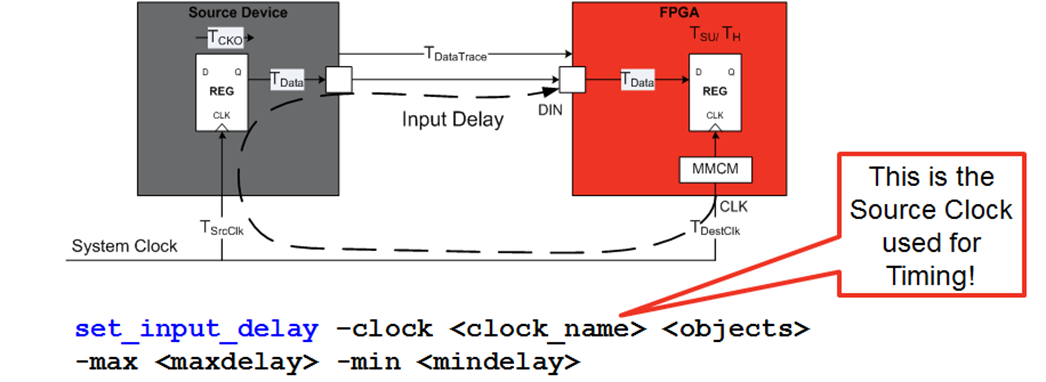

Input約束

上圖所示set_input_delay的基本語法中, 是想要設定input約束的端口名,可以是一個或數個port;-clock 之后的 指明了對 時序進行分析所用的時鐘,可以是一個FPGA中真實存在的時鐘也可以是預先定義好的虛擬時鐘;-max之后的 描述了用于setup分析的包含有板級走線和外部器件的延時;-min之后的 描述了用于hold分析的包含有板級走線和外部器件的延時。

上述這些選項是定義Input約束時必須寫明的,還有少數幾個可選項,如 -add_delay 和 -clock_fall用于DDR接口的約束。

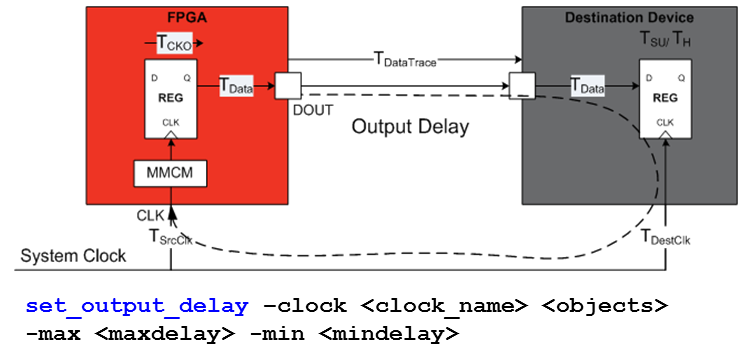

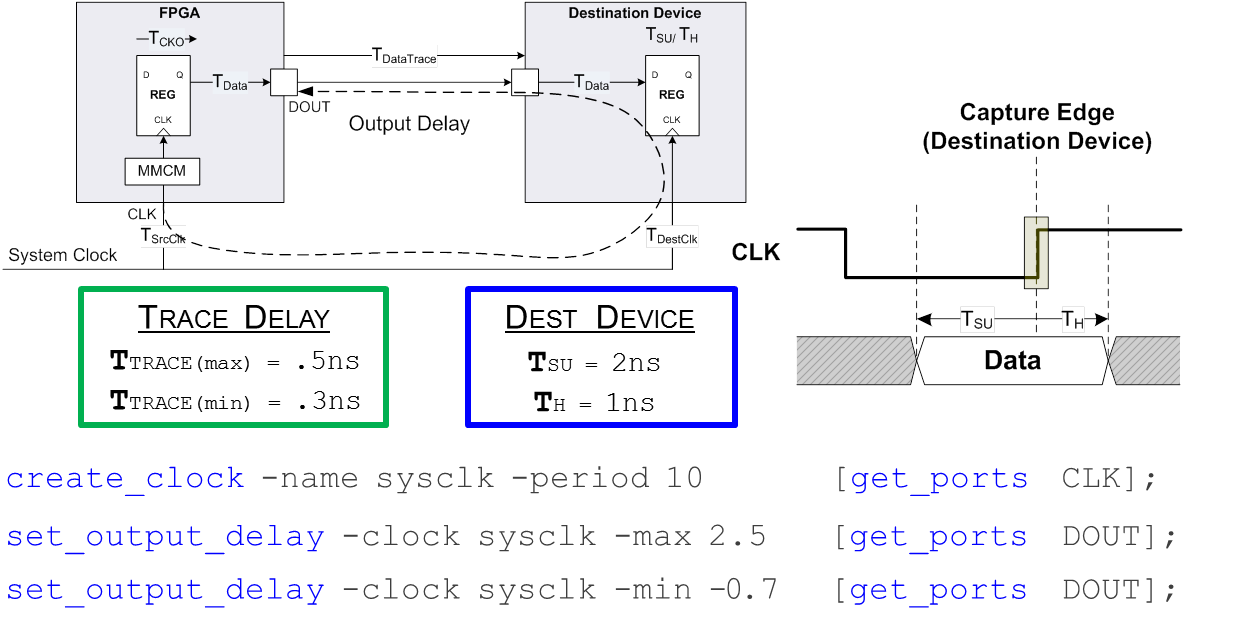

Output約束

上圖所示set_output_delay的基本語法中, 是想要設定output約束的端口名,可以是一個或數個port;-clock 之后的 指明了對 時序進行分析所用的時鐘,可以是一個FPGA中真實存在的時鐘也可以是預先定義好的虛擬時鐘;-max之后的 描述了用于setup分析的包含有板級走線和外部器件的延時;-min之后的 描述了用于hold分析的包含有板級走線和外部器件的延時。

上述這些選項是定義Output約束時必須寫明的,還有少數幾個可選項如 -add_delay 和 -clock_fall用于DDR接口的約束。

Setup/Hold時序分析

我們知道約束是為了設計服務,而設置好的約束必須在時序報告中加以驗證。所以,怎樣理解時序分析中的檢查規則就成了重中之重,這一點對I/O約束來說尤為重要。理解時序分析工具如何選取路徑分析的發送端(Launch)和接收端(Capture)時鐘沿(Clock Edges),在Setup和Hold分析時又有怎樣的具體區別,以及這些數字在時序報告中如何體現等等是設置正確I/O約束的基礎。

更具體的時序分析方法以及如何深入解讀時序報告等內容將會在后續另開主題文章詳述,這里僅就Setup/Hold分析時對時鐘邊沿的選擇加以描述,便于以下章節的展開。

Setup時序分析

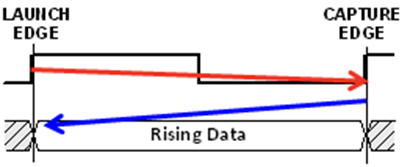

同步電路設計中,一般情況下,數據在時鐘上升沿發送,在下一個時鐘上升沿接收,發送的時鐘沿稱作Launch Edge,接收沿稱作Capture Edge。時序分析中的Setup Check跟Capture Edge的選擇息息相關。

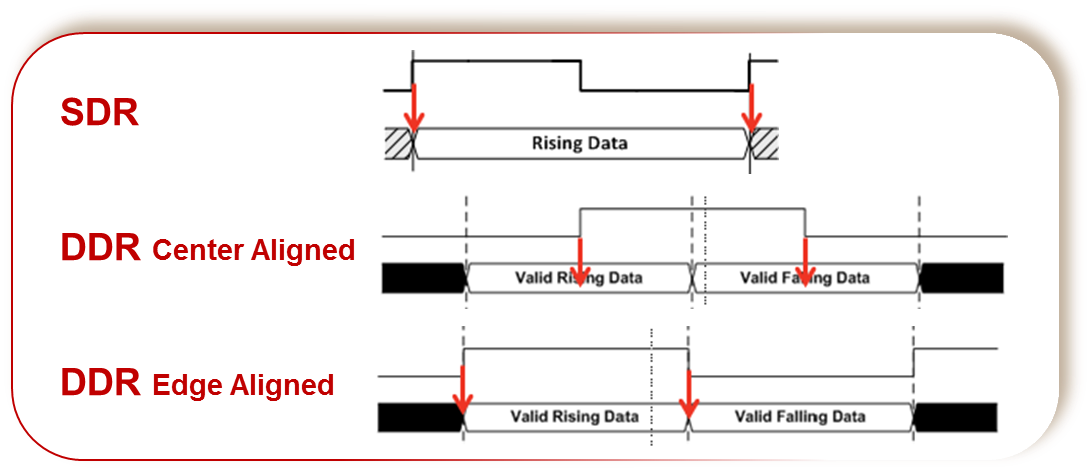

在SDR接口的setup分析中,工具如下圖這樣識別發送和接收時鐘沿。

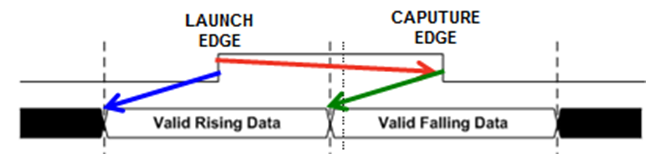

而在DDR接口的setup分析中,因為數據是雙沿采樣,所以發送和接收時鐘沿變成上升(下降)沿發送,下降(上升)沿接收。

Hold時序分析

Hold Check主要是為了保證數據在接收(采樣)端時鐘沿之后還能穩定保持一段時間,對Hold分析而言,同一個時鐘沿既是Launch Edge也是Capture Edge,這一點對SDR和DDR(不論是中心對齊還是邊沿對齊)都一樣。

Input接口類型和約束

由于歷史的原因,相當一部分FPGA設計仍然在系統中起到膠合邏輯(Glue Logic)的作用,當然,如今的FPGA中嵌入了高速串行收發器和嵌入式處理器等,早就不僅僅局限于系統設計的配角,反而成為了其中的主角甚至是明星。但數據接口的同步一直是 FPGA設計中的常見問題,也是一個重點和難點,很多設計不穩定都是因為數據接口的同步有問題。

FPGA的數據接口同步根據系統級設計方式來講可以分為系統同步和源同步兩種。

系統同步接口

系統同步接口(System Synchronous Interface)的構建相對容易,以FPGA做接收側來舉例,上游器件僅僅傳遞數據信號到FPGA中,時鐘信號則完全依靠系統板級來同步。時鐘信號在系統級上同源,板級走線的延時也要對齊。正因為這樣的設計,決定了數據傳遞的性能受到時鐘在系統級的走線延時和skew以及數據路徑延時的雙重限制,無法達到更高速的設計要求,所以大部分情況也僅僅應用SDR方式。

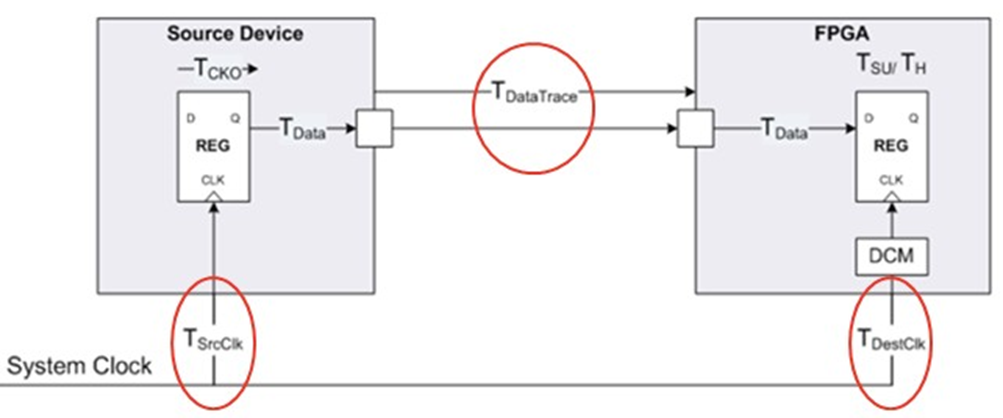

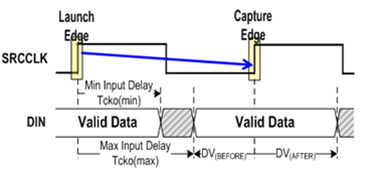

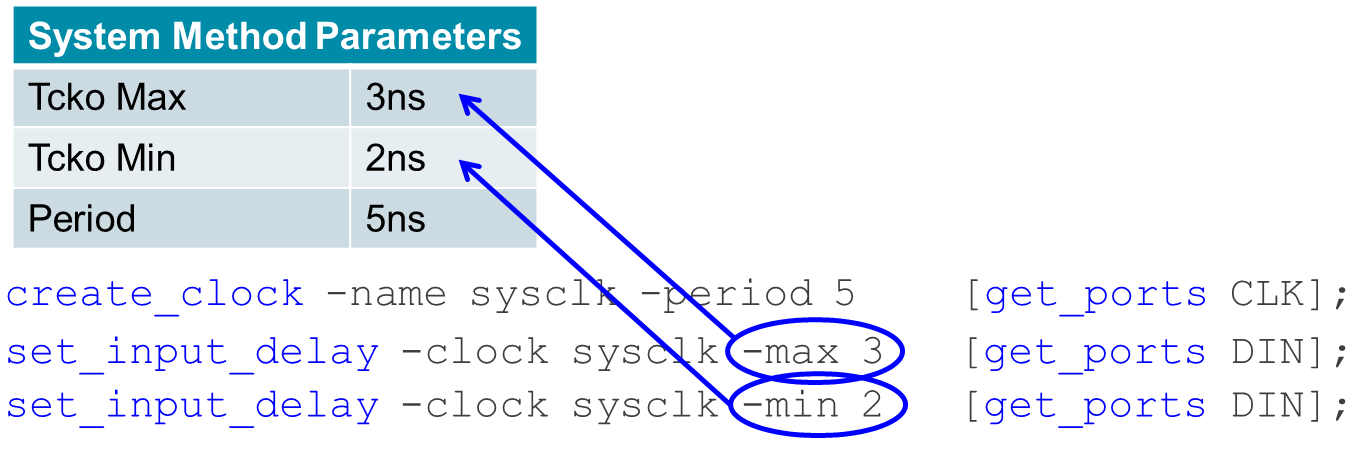

對系統同步接口做Input約束相對容易,只需要考慮上游器件的Tcko和數據在板級的延時即可。下圖是一個SDR上升沿采樣系統同步接口的Input約束示例。

設置和分析I/O約束一定要有個系統級思考的視角,如上右圖所示,Launch Edge對應的是上游器件的時鐘,而Capture Edge則對應FPGA的輸入時鐘,正因為是系統同步時鐘,所以可以將其視作完全同步而放在一張圖上分析,這樣一來,就可以用一般時序分析方法來看待問題。

一條完整的時序路徑,從源觸發器的C端開始,經過Tcko和路徑傳輸延時再到目的觸發器的D端結束。放在系統同步的接口時序上,傳輸延時則變成板級傳輸延時(還要考慮skew),所以上述 -max 后的數值是Tcko的最大值加上板級延時的最大值而來,而-min后的數值則是由兩個最小值相加而來。

源同步接口

為了改進系統同步接口中時鐘頻率受限的弊端,一種針對高速I/O的同步時序接口應運而生,在發送端將數據和時鐘同步傳輸,在接收端用時鐘沿脈沖來對數據進行鎖存,重新使數據與時鐘同步,這種電路就是源同步接口電路(Source Synchronous Interface)。

源同步接口最大的優點就是大大提升了總線的速度,在理論上信號的傳送可以不受傳輸延遲的影響,所以源同步接口也經常應用DDR方式,在相同時鐘頻率下提供雙倍于SDR接口的數據帶寬。

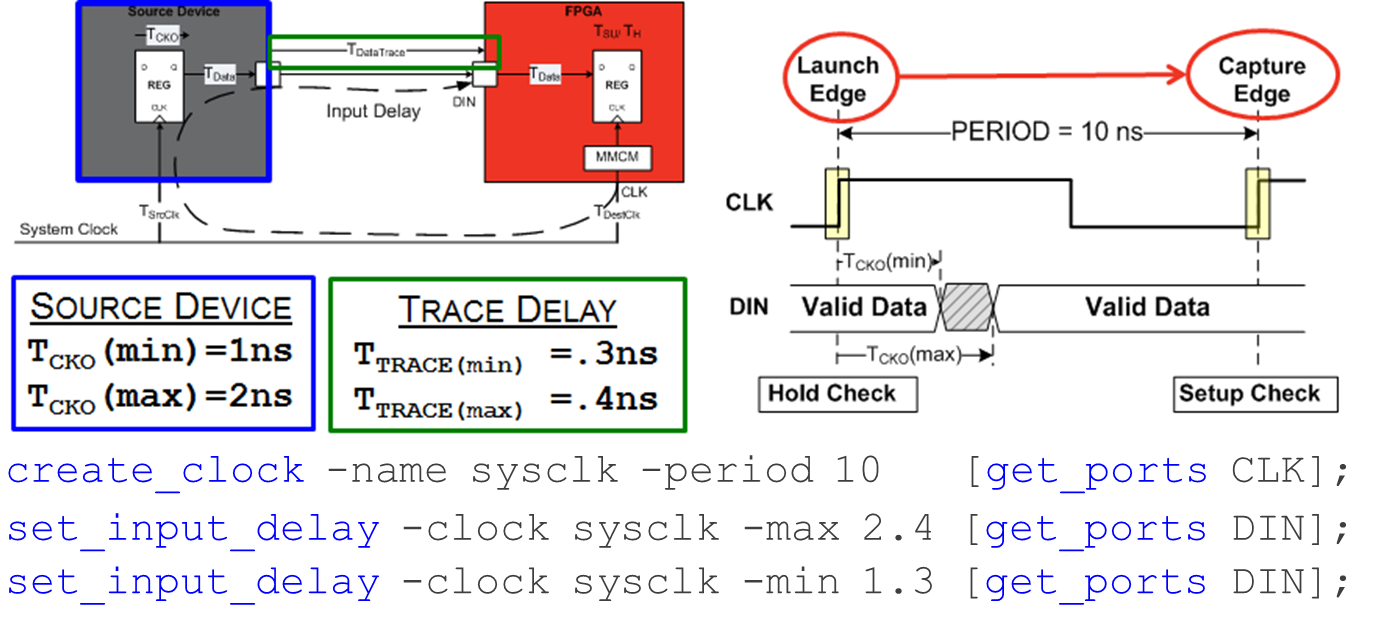

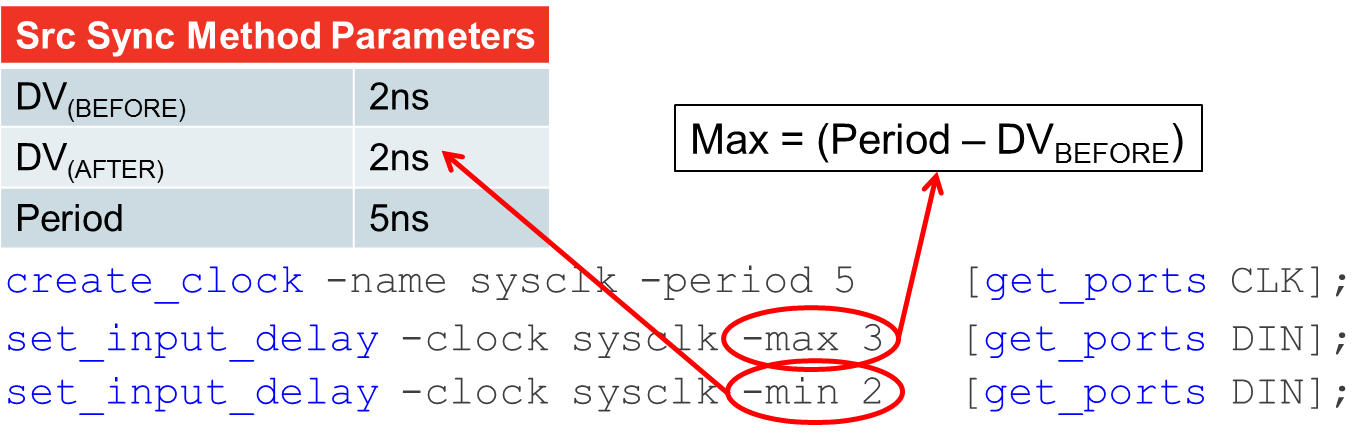

源同步接口的約束設置相對復雜,一則是因為有SDR、DDR、中心對齊(Center Aligned)和邊沿對齊(Edge Aligned)等多種方式,二則可以根據客觀已知條件,選用與系統同步接口類似的系統級視角的方式,或是用源同步視角的方式來設置約束。

如上圖所示,對源同步接口進行Input約束可以根據不同的已知條件,選用不同的約束方式。一般而言,FPGA作為輸入接口時,數據有效窗口是已知條件,所以方法2更常見,Vivado IDE的Language Templates中關于源同步輸入接口XDC模板也是基于這種方法。但不論以何種方式來設置Input約束,作用是一樣,時序報告的結果也應該是一致的。

針對上圖所示中心對齊源同步SDR接口時序,分別按照兩種方式來約束,需要的已知條件和計算方式雖然不同,但卻可以得到完全一樣的結果。

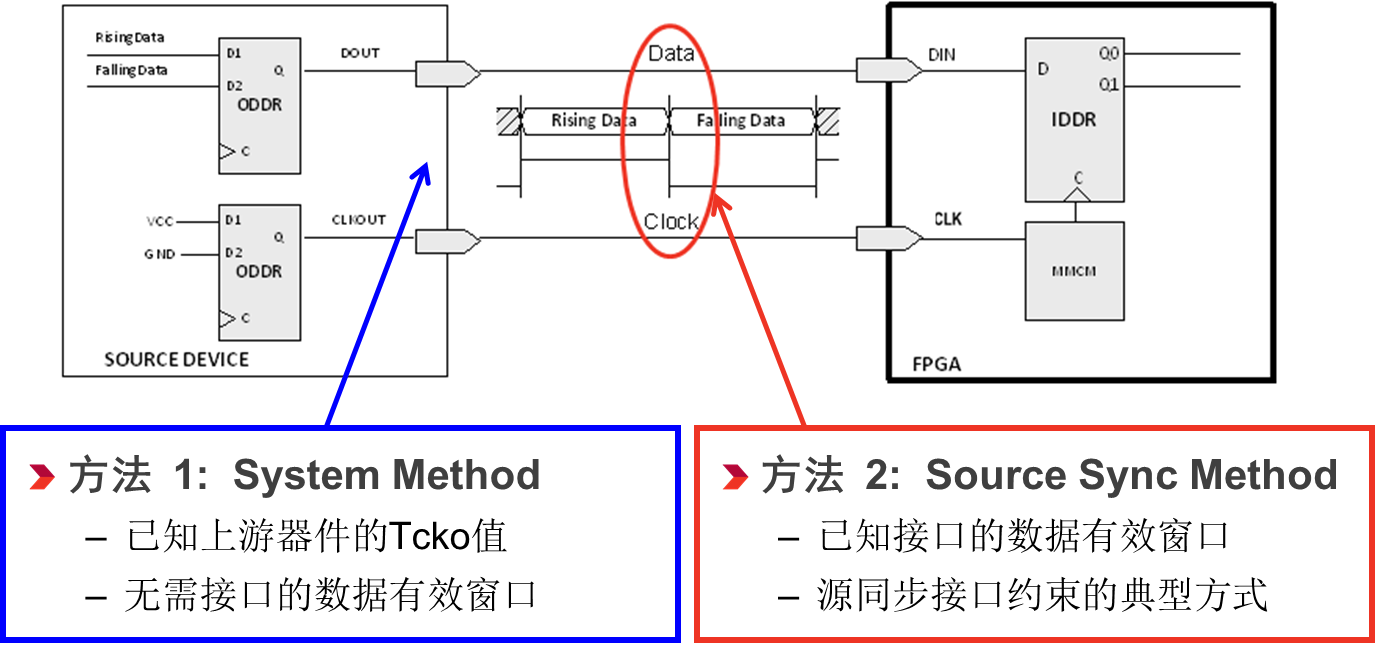

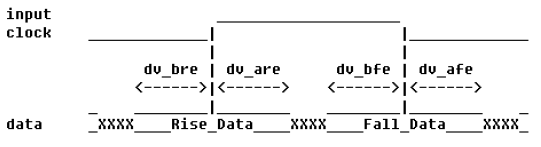

DDR接口的約束設置

DDR源同步接口的約束稍許復雜,需要將上升沿和下降沿分別考慮和約束,以下以源同步接口為例,分別就輸入接口數據為中心對齊或邊沿對齊的方式來舉例。

DDR源同步中心對齊輸入接口

已知條件如下:

時鐘信號 src_sync_ddr_clk的頻率: 100 MHz

數據總線: src_sync_ddr_din[3:0]

上升沿之前的數據有效窗口 ( dv_bre ) :4 ns

上升沿之后的數據有效窗口 ( dv_are ) : 6 ns

下降沿之前的數據有效窗口 ( dv_bfe ) :7 ns

下降沿之后的數據有效窗口 ( dv_afe ) : 2 ns

可以這樣計算輸入接口約束:DDR方式下數據實際的采樣周期是時鐘周期的一半;上升沿采樣的數據(Rise Data)的 -max 應該是采樣周期減去這個數據的發送沿(下降沿)之前的數據有效窗口值dv_bfe,而對應的-min 就應該是上升沿之后的數據有效窗口值dv_are ;同理,下降沿采樣的數據(Fall Data)的 -max 應該是采樣周期減去這個數據的發送沿(上升沿)之前的數據有效窗口值dv_bre,而對應的-min 就應該是下降沿之后的數據有效窗口值dv_afe 。

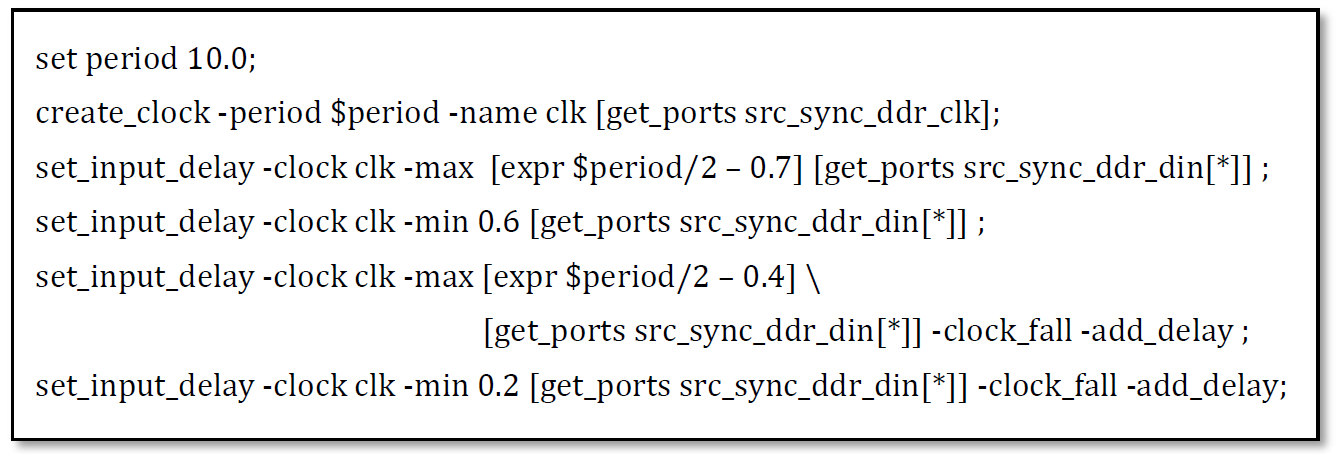

所以最終寫入XDC的Input約束應該如下所示:

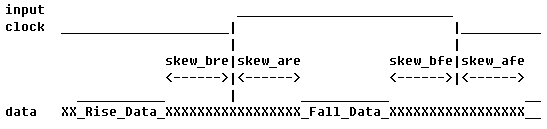

DDR源同步邊沿對齊輸入接口

已知條件如下:

時鐘信號 src_sync_ddr_clk的頻率: 100 MHz

數據總線: src_sync_ddr_din[3:0]

上升沿之前的數據skew (skew_bre ) :6 ns

上升沿之后的數據skew (skew_are ) :4 ns

下降沿之前的數據skew (skew_bfe ) :3 ns

下降沿之后的數據skew (skew_afe ) :7 ns

可以這樣計算輸入接口約束:因為已知條件是數據相對于時鐘上升沿和下降沿的skew,所以可以分別獨立計算;上升沿的 -max 是上升沿之后的數據skew (skew_are ),對應的-min 就應該是負的上升沿之前的數據skew (skew_bre );下降沿的 -max 是下降沿之后的數據skew (skew_afe ),對應的-min 就應該是負的下降沿之前的數據skew (skew_bfe )。

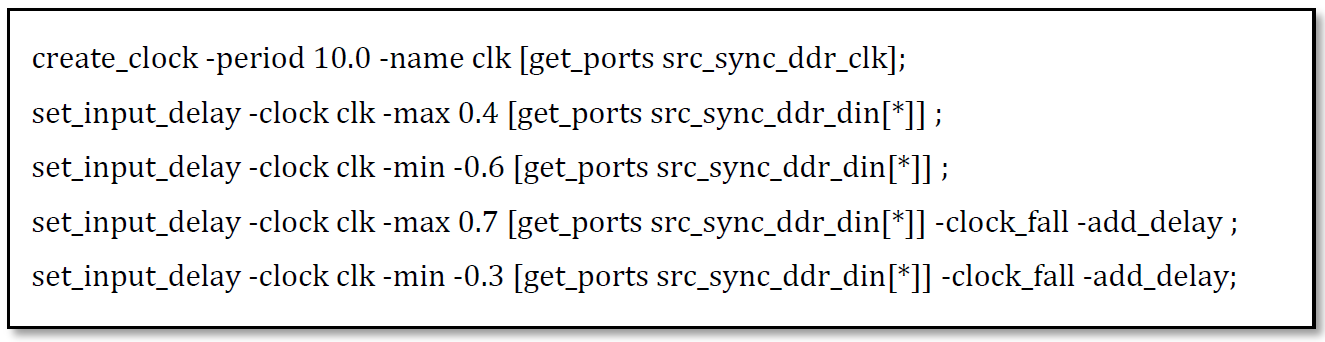

所以最終寫入XDC的Input約束應該如下所示:

出現負值并不代表延時真的為負,而是跟數據相對于時鐘沿的方向有關。請一定牢記set_input_delay中 -max/-min的定義,即時鐘采樣沿到達之后最大與最小的數據有效窗口(set_output_delay中 -max/-min的定義與之正好相反,詳見后續章節舉例說明)。

在這個例子中,數據是邊沿對齊,只要有jitter跟skew的存在,最差情況下,數據有效窗口在到達時鐘采樣沿之前就已經結束,所以會有負數出現在-min之后。因此,在實際應用中,FPGA用作輸入的邊沿對齊DDR源同步接口的情況下,真正用來采樣數據的時鐘會經過一個MMCM/PLL做一定的相移,從而把邊沿對齊變成中心對齊。

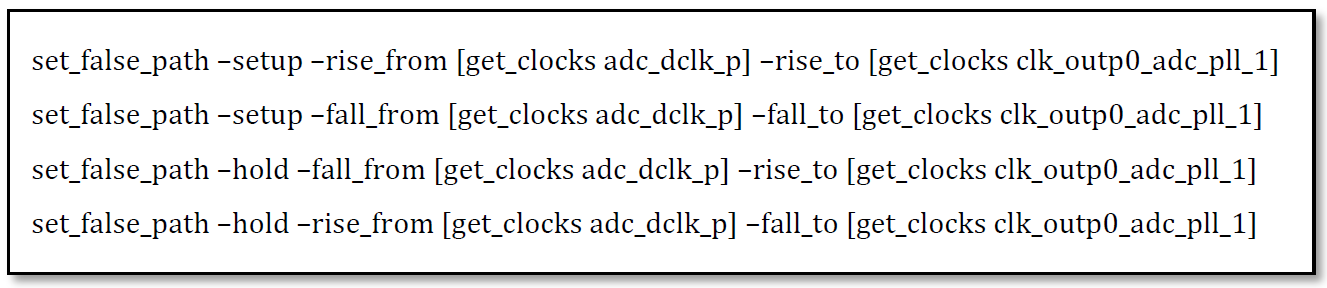

另外,在經過MMCM/PLL相移后的采樣時鐘跟同步接口輸入的時鐘之間需要做set_false_path的約束(如下述例子)而把那些偽路徑從時序報告中剔除,這里不再詳述。

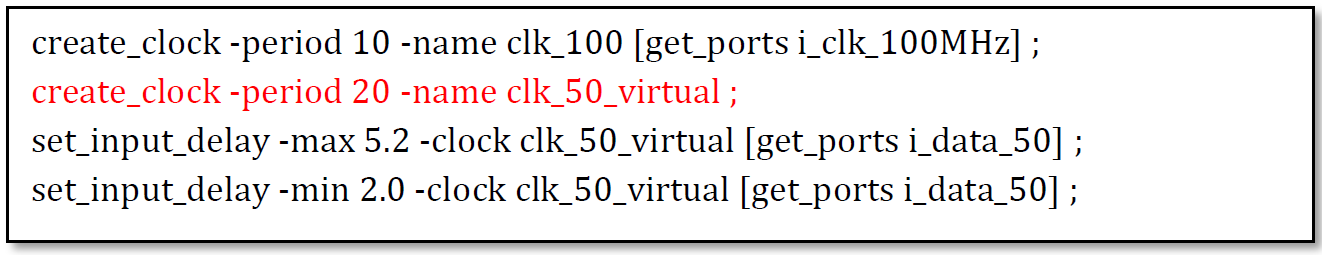

虛擬時鐘

在FPGA做系統同步輸入接口的情況下,很多時候上游器件送入的數據并不是跟某個FPGA中已經存在的真實的時鐘相關,而是來自于一個不同的時鐘,這時就要用到虛擬時鐘(Virtual Clock)。

舉例來說,上游器件用一個100MHz的時鐘送出數據到FPGA,實際上這個數據每兩個時鐘周期才變化一次,所以可以用50MHz的時鐘來采樣。FPGA有個100MHz的輸入時鐘,經過MMCM產生一個50MHz的衍生時鐘,并用其來采樣上游器件送來的同步數據。當然,系統級的設計上,必須有一定的機制來保證上游器件中的發送時鐘和FPGA中的接收時鐘的時鐘沿對齊。

此時,我們可以借助虛擬時鐘的幫助來完成相應的Input接口約束。

-

電路

+關注

關注

172文章

5950瀏覽量

172588 -

約束

+關注

關注

0文章

82瀏覽量

12748 -

Output

+關注

關注

0文章

31瀏覽量

10514

發布評論請先 登錄

相關推薦

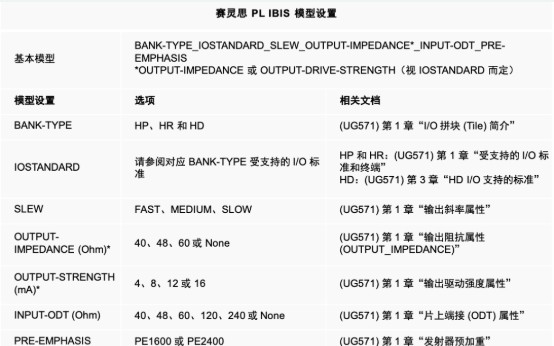

FPGA設計時序約束指南【賽靈思工程師力作】

回收Xilinx芯片 收購賽靈思芯片

賽靈思關于I/O約束法的簡要概括(下)

賽靈思關于I/O約束法的簡要概括(上)

賽靈思關于I/O約束法的簡要概括(上)

評論