最近的項目邏輯資源不夠,因為應用需求,要一組256個四輸入的模塊,后來改吧改吧,改成了一組165個6輸入的模塊,解決了需求問題,為什么啊,因為四輸入的那個模塊浪費xilinx的資源了,xilinx的LUT是六輸入的,xilinx在7系列前的LUT還是五輸入的,現在都變成了六輸入(其實是兩個五輸入共享連接線)。

具體應用不說了,來看看關于LUT表這件事。

LUT表是最基本的邏輯單元,入門書籍必有的內容,基本原理這里不說了。

一般的,有SLICEM和SLICEL兩種,M代表存儲,L代表邏輯,好記吧。

L的功能M也能實現,M比L更復雜,所以我們直接去看SLICEM。

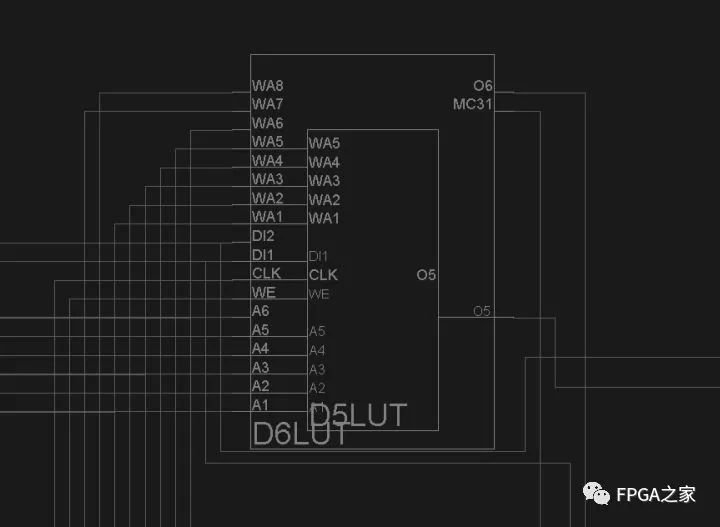

圖上面時直接從工具里面截的,這里面包括了:

6位讀地址輸入(A1-A6)

8位寫地址輸入(WA1-WA7)

寫時鐘(CLK)

寫使能(WEN)

數據輸入(DI1)

數據輸出(O6)

移位寄存器輸出(MC31)

除此之外,由于DI2輸入線和O5輸出的存在,這片LUT還可以被配置為32-depth,2-bit-data-wide的RAM。

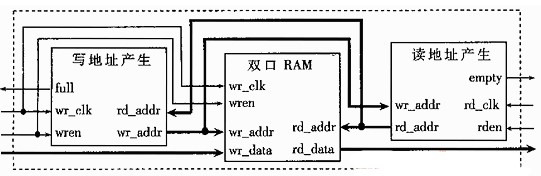

為什么寫是8位,讀是6位呢?有疑惑就看datasheet或者user guide啊,翻出UG474,里面有張圖,看了就明白了:

拿一個SLICEM的四個LUT搭一個256的單口RAM,看到了吧,寫地址8位直接用,讀地址用6位,然后高兩bit,一個給F7MUX,一個給F8MUX,相當于做了兩級二選一。

還有一個重點要說的是移位寄存器,移位寄存器用的最多的地方就是做delay 了。

下面是簡單的兩段代碼:

always @(posedge clk )begin

shift_r <= {shift_r[62:0],rxp} ;

end

always @(posedge clk )begin

txp <= shift_r[63];

end

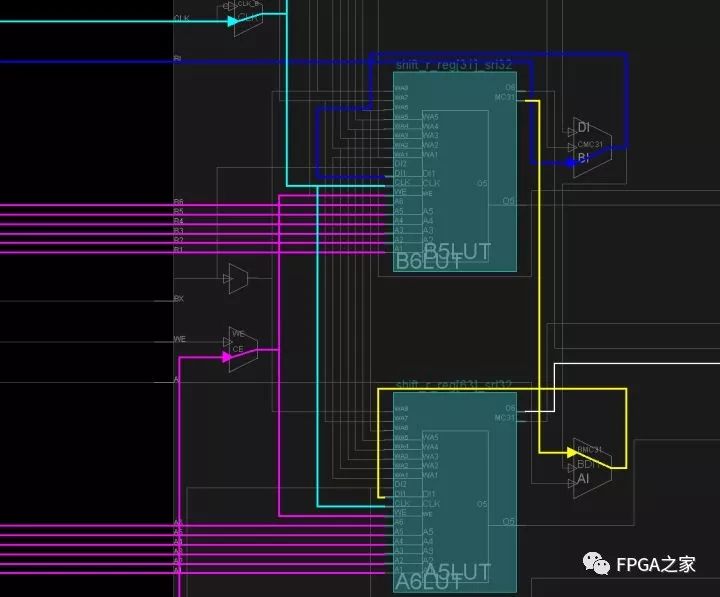

大概的意思就是將rxp輸入延遲64個時鐘周期,然后輸出。在很多文檔里面都說過了,LUT單元是可以直接生成移位寄存器的,當然必須是SLICEM里面的LUT的,我們看看最后生成的結果是啥樣的:

有點不好看啊,我倆簡單解釋一下:

1.紅線代表LTU讀地址輸入,讀地址代表了移位寄存器輸出的位數,寫31就是延遲32位,可見所有的地址都被連接在一個高電平上,5h11111=31,一般情況下,是A[5:1]表征地址,A[0]固定為高

2.青色是時鐘,這對于SLICEL來說是沒有的,因為有了時鐘,才可能同步操作;

3.藍色是需要移位的數據,程序里面的rxp,直接輸入到了LUT-B的數據DI1口

4.黃色從LUT-B的MC31輸出的結果,一個LUT可以作為32位的移位寄存器,因為需要移位64次, 所以需要兩個LUT級聯才能完成完整的移位結果

5.白色是最后的輸出,注意是從O6輸出的,即級聯之后64位移位后的結果,再過一級FF之后,就是txp 。

這種寫法比較簡單直觀,也有一些同學想要規范,那我們調用一下官方的原語試試:

SRL16E #(

.INIT(16'h0000), // Initial contents of shift register

.IS_CLK_INVERTED(1'b0) // Optional inversion for CLK

)

SRL16E_inst (

.Q(SRL10_r), // 1-bit output: SRL Data

.CE(1), // 1-bit input: Clock enable

.CLK(clk), // 1-bit input: Clock

.D(rxp ), // 1-bit input: SRL Data

// Depth Selection inputs: A0-A3 select SRL depth

.A0(0),

.A1(1),

.A2(0),

.A3(1) //0x1010= 10

);

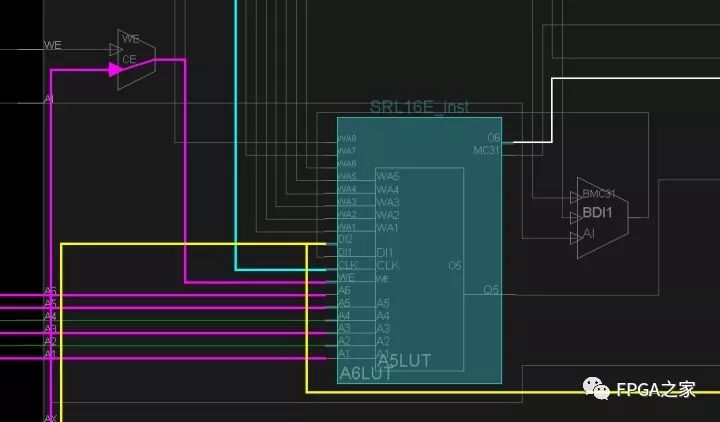

這是一個經典的16位寄存器的小模塊,看看布線后成啥樣:

1.紅線代表LTU讀地址輸入,讀地址代表了移位寄存器輸出,一般情況下,是A[5:1]表征地址,但是我們看到黃色線代表的數據激怒的是DI2,也就是用了兩個5輸入LUT中的一個,所以真實的地址是4‘h1010 = 10,也就是移位10+1次,A[0]固定為高

2.青色是時鐘;

3.黃色是輸入,rxp ,注意是從DI2口輸入的

4.白色是最后的輸出,注意是從O6輸出的,即10位移位后的結果,也就是SRL10_r。

7系列因為LUT表地址位增加,因此還支持32位移位的原語,我們來看看:

SRLC32E #(

.INIT(32'h00000000), // Initial contents of shift register

.IS_CLK_INVERTED(1'b0) // Optional inversion for CLK

)

SRLC32E_inst (

.Q(SRL20_r), // 1-bit output: SRL Data

.Q31(SRL31_r), // 1-bit output: SRL Cascade Data

.A(5'd20), // 5-bit input: Selects SRL depth

.CE(1), // 1-bit input: Clock enable

.CLK(clk), // 1-bit input: Clock

.D(rxp ) // 1-bit input: SRL Data

);

看看會是怎樣布線的:

1.紅線代表LTU讀地址輸入,讀地址代表了移位寄存器輸出,一般情況下,是A[5:1]表征地址,是5‘h10100 = 20,也就是移位20次,A[0]固定為高

2.青色是時鐘;

3.黃色是輸入,rxp ,注意是從DI1口輸入的

4.白色時最后的輸出,注意是從O6輸出的,即20+1位移位后的結果,也就是SRL20_r。

5.咖啡色是32位移位后的結果,也就是SRL31_r

這個移位跟信號實際delay的關系,還要看個仿真才能看明白:

圖要放大看,rxp_r信號delay了11個時鐘節拍(計數器從750到761)得到信號SRL10_r,delay了21個時鐘節拍得到了信號SRL20_r,delay了32個時鐘節拍得到信號SRL31_r。

也就是delay的時鐘節拍N,與配置的LUT地址A之間的關系為:

N = A + 1

-

移位寄存器

+關注

關注

3文章

258瀏覽量

22294

原文標題:二大爺聊FPGA(8).LUT與移位寄存器

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

labview基于的簡單的循環采集數據(包括讀、寫命令及報警功

零基礎學FPGA(十一)初入江湖之i2c通信

FIFO讀使能問題

電池管理器件的讀/寫操作

Linux下flash操作讀、寫、擦除步驟

MCS-51單片機指令系統“讀-改-寫”指令

PIC何謂讀-修改-寫,導致的問題及其解決之道

單片機里面“”32bit地址“”與所指向的“8bit數據“的關系

優化數據庫性能使用LSI MegaRAID CacheCade Pro 2.0讀/寫緩存軟件

vLUT表:寫 讀地址輸入、數據輸出 入這里面包括

vLUT表:寫 讀地址輸入、數據輸出 入這里面包括

評論