L6562A建模1

今天我們開始以L6562A為例來介紹如何使用Simpis對芯片進行行為級別建模。

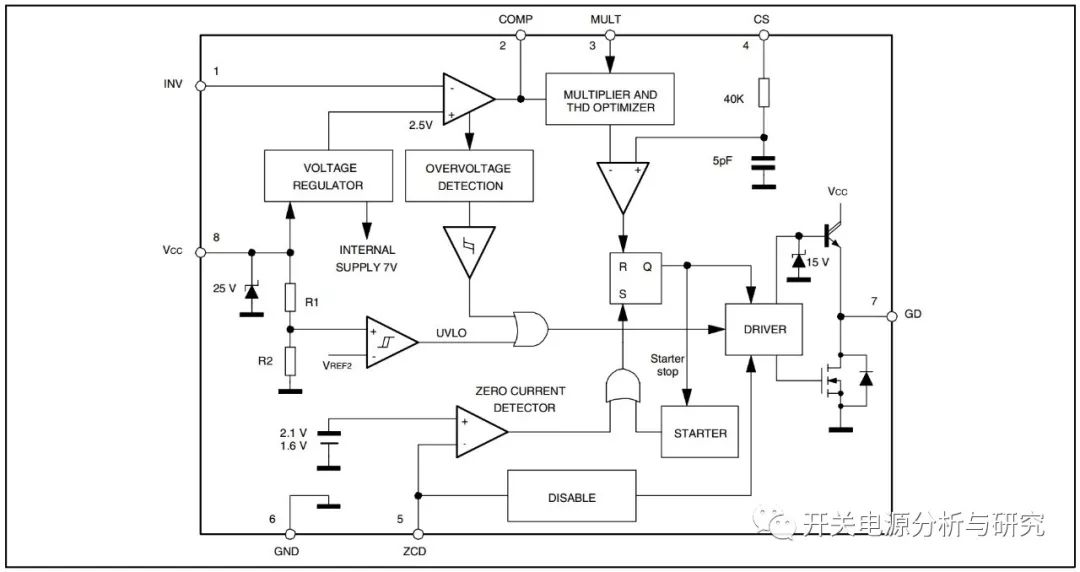

L6562A是一款基于BCM(臨界導通模式)的PFC控制器。我們先看一下它的框圖:

以及各個引腳的功能:

INV:電壓反饋引腳,用于穩定輸出電壓;

COMP:誤差比較器輸出,需要加上補償網絡使電壓環穩定,以及實現高功率因數和較低的THD;

MULT:內部乘法器的輸入管腳,用來為內部電流環提供板正弦參考信號,實現PFC(使輸出電流與電壓同相位,都為半正弦形狀);

CS:電流采樣信號引腳,采集流過MOS管的電流信號,輸入到內部比較器,與內部半正弦調制信號比較,產生PWM信號;

ZCD:生壓電感去磁感應輸入引腳,當檢測到流過升壓電感的電流下降到零時,會在內部產生一個下降沿信號信號觸發驅動電路開啟,打開開關,開始下一個周期;

GND:內部參考地信號;

GD:內部驅動信號,用于驅動外部MOS管;

Vcc:芯片供電引腳;

我們對照框圖簡單介紹一下它的工作原理:MULT引腳采樣前端整流橋的輸出電壓信號(半正弦波形),該信號作為電流信號的調制整形參考信號。CS引腳一方面是采樣電感電流信號,使用前述半正弦調制整形信號來調制電感電流信號包絡。INV是電壓環反饋引腳,配合COMP引腳的補償電路實現穩定的電壓環。ZCD引腳監測磁芯狀態,用來開啟下一個周期。

還是需要強調一點,我們建立的行為級別模型是基于數據手冊規格參數表和原理描述以及我自己對于這個的理解,并不能表示真實的電路到底是如何實現的,每個人對于某一功能或參數的理解以及實現方法可能都不一樣,所以大家不用糾結,只是給大家參考一下,大家有更好的想法可以告訴我。

我們從幾個方面來討論L6562A的建模,我們會分幾次給大家介紹。

供電部分

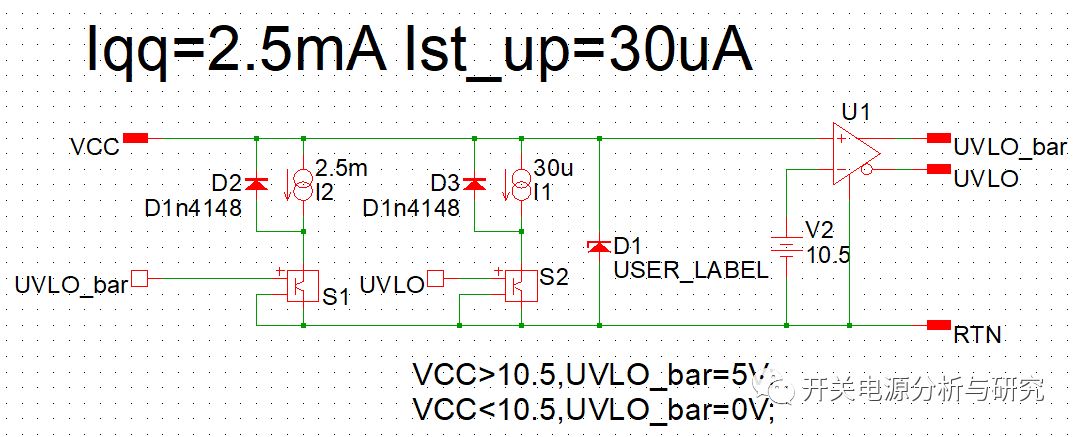

輸入欠壓檢測電路:

當輸入供電電壓高于10.5V時,UVLO_bar信號輸出為高,表明沒有出現欠壓現象,若輸入供電電壓低于10.5V時,UVLO為高電平,表明輸入電壓欠壓;2.5mA表征啟動后的靜態電流;30uA表征未正常啟動(欠壓)下的靜態電流;(參照規格書中的Istart_up和Iq)

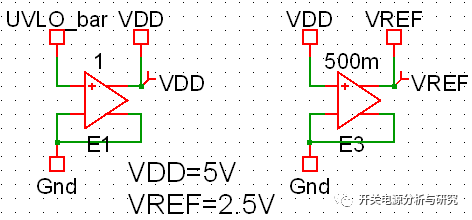

內部參考與供電信號:

VDD為內部電路供電,VREF是內部電壓環參考電壓;

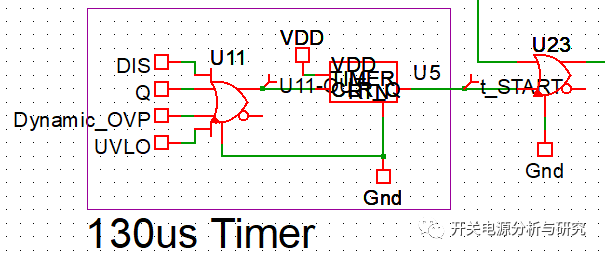

時鐘電路

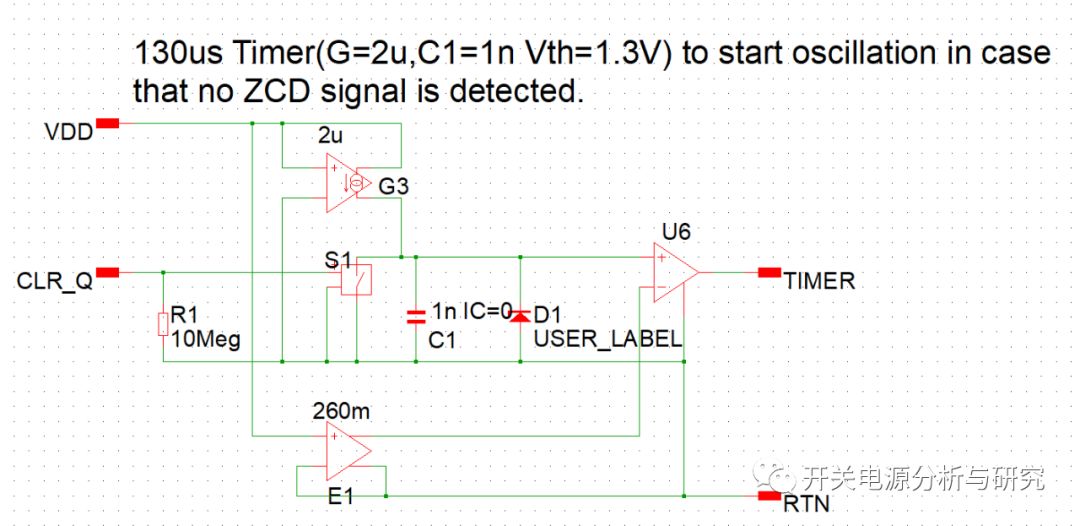

數據手冊框圖中畫出了一個STARTER,它與ZCD引腳實現的ZERO CURRENT DETECTION電路輸出的信號經過或的邏輯后輸出到RS觸發器的S端。這兩個信號就是內部實現開關開啟的觸發信號。規格參數中的tSTART指定了內部一個固定時鐘,其周期典型值為130us,其電路表示及其內部電路實現如下:

其實現原理非常簡單,就是通過控制一個電流源對一個電容沖放電,當電容電壓高于參考值時輸出高電平,否則輸出低電平。當然這個時鐘一般只在系統剛啟動時工作,待進入穩態后該時鐘就不起作用了。U11的四個輸入信號是用來給電容放電或關閉時鐘的。待進入穩態后系統周期低于130us,當開關管開啟時Q為高電平,該信號會釋放C1電流,這樣該時鐘模塊永遠不會輸出高電平,即關閉了該時鐘模塊。DIS, Dynamic_OVP, UVLO都是在出現錯誤狀態下關閉該時鐘的信號。

-

芯片

+關注

關注

456文章

50908瀏覽量

424459 -

控制器

+關注

關注

112文章

16389瀏覽量

178427 -

電壓

+關注

關注

45文章

5612瀏覽量

115913

原文標題:淺談芯片建模2

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ADuC7026微控制器在125°C下運行時不斷重啟、這是正常行為嗎?

使用C2000 MCU對用于數字控制的雙向降壓/升壓轉換器進行建模

使用PSpice仿真器對TI智能高側開關中的熱行為進行建模

L6562A對芯片進行行為級別建模控制器

L6562A對芯片進行行為級別建模控制器

評論