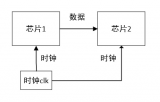

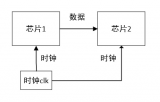

一、前言 芯片間的數據傳輸根據同一時間傳輸的bit數分為串行傳輸和并行傳輸。 串行傳輸:每次傳輸1b....

一、主時鐘create_clock 1.1 定義 主時鐘是來自FPGA芯片外部的時鐘,通過時鐘輸入端....

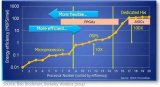

FPGA已成為現今的技術熱點之一,無論學生還是工程師都希望跨進FPGA的大門。那么我們要玩轉FPGA....

多相濾波器的基本概念是把FIR濾波器分割成若干較小的單元,然后組合這些單元的結果。首先,讓我們考慮一....

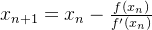

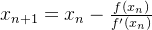

一、平方根及三種常見平方根算法簡介 數學是物理的基礎,是廣大世界的基本組成部分,而數學運算是數學理論....

一、單比特CDC傳輸1.1 慢到快 快時鐘域相比慢時鐘域采樣速度更快,也就是說從慢時鐘域來到快時鐘域....

一、RGB接口 (1)接口定義 RGB顏色是工業界的一種顏色標準,是通過對紅、綠(G)、藍(B)三個....

一、UART協議 1.UART簡介 通用異步收發器,是一種通用的串行、異步通信總線,該總線有兩條數據....

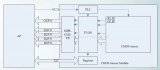

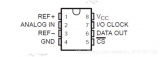

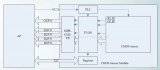

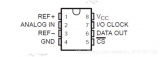

AD芯片采用TLC549,該芯片的功能為將模擬信號轉換成數字信號。通常的模數轉換器是將一個輸入電壓信....

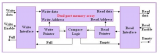

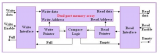

FSMC總線通信簡介 FSMC是STM32系列采用的一種新型存儲器擴展技術。在外部存儲器擴展方面具有....

FIFO作為FPGA崗位求職過程中最常被問到的基礎知識點,也是項目中最常被使用到的IP,其意義是非常....

HDMI(High Definition Multimedia Interface)高解晰度多媒體數....

AMBA AXI4(高級可擴展接口 4)是 ARM 推出的第四代 AMBA 接口規范。AMD Viv....

1. FIFO簡介 FIFO是一種先進先出數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,使用....

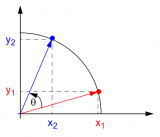

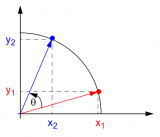

CORDIC算法的思想是通過迭代的方法,使得累計旋轉過的角度的和無限接近目標角度。它是一種數值計算逼....

TCP/IP 協議 使用 TCP/IP 協議可以將 FPGA 中的數據以太網的形式輸出到上位機,上位....

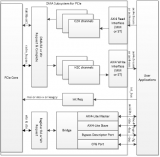

PCIE是一種用于連接計算機內部各個組件的總線標準,而上位機是指與設備進行通信和控制的計算機。

PCIE是一種高速串行總線接口標準,用于連接計算機內部的各種外設和組件。在PCIe架構中,BAR(B....

JESD204是一種連接數據轉換器(ADC和DAC)和邏輯器件的高速串行接口,該標準的 B 修訂版支....

FPGA(現場可編程門陣列)和DSP(數字信號處理器)之間通過SRIO接口進行調試通常需要以下步驟....

眾所周知,通用處理器(CPU)的摩爾定律已入暮年,而機器學習和 Web 服務的規模卻在指數級增長。

FIFO是一種先進先出數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,使用起來非常簡單,缺點是....

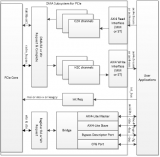

安路科技提供基于PCIe 硬核控制器開發的SGDMA IP。SGDMA可作為一個PCIe2AXI4系....

在以太網鏈路上的數據包稱作以太網幀。以太網幀起始部分由前導碼和幀開始符組成。后面緊跟著一個以太網報頭....

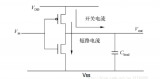

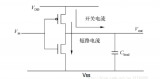

CMOS電路功耗主要由動態功耗和靜態功耗組成,動態功耗又分為開關功耗、短路功耗兩部分

總的片上功耗 Total On-Chip Power: 總的片上功耗是器件內部的功耗,等同于器件的靜....

在數字信號處理(DSP)領域,需要處理的數據量很大,并且實時性要求很高。

對于那些了解FPGA靈活性和可編程性的人來說,這并不令人驚訝,但對許多其他人來說,這兩者之間的聯系可....

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口....

在利用處理編碼信號時,一般在較為理想的環境下可以很方便進行計算,判斷等。