本文為大家帶來四個八進制計數器設計方案。

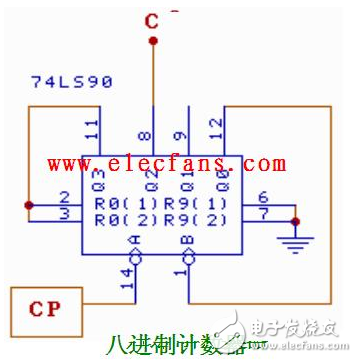

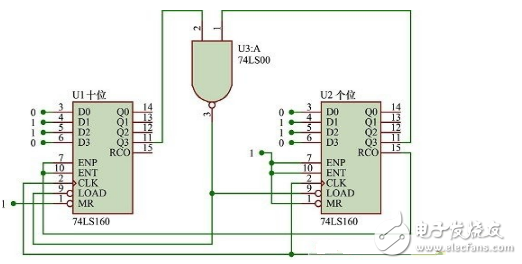

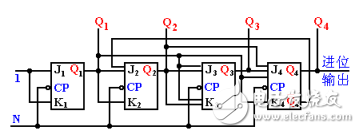

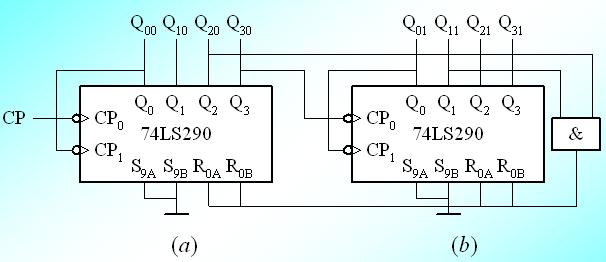

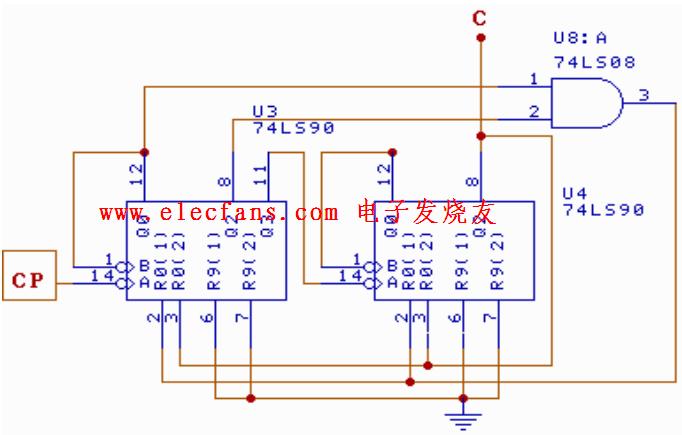

八進制計數器設計方案一:基于74LS90芯片的八進制計數器設計

兩位以上的數需要74LS90芯片級連,即低位芯片計數滿后,低位的最高位作為進位,送到高一位芯片的CP端。

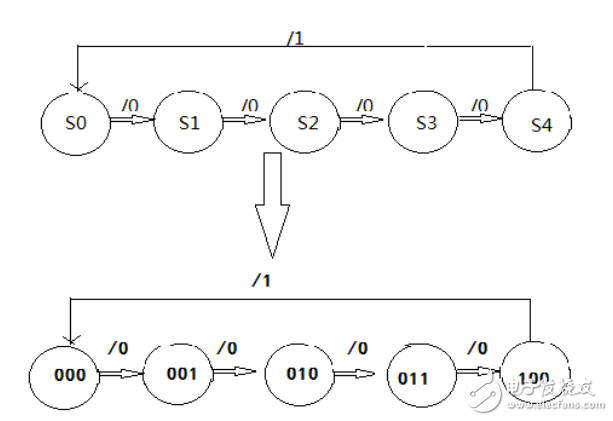

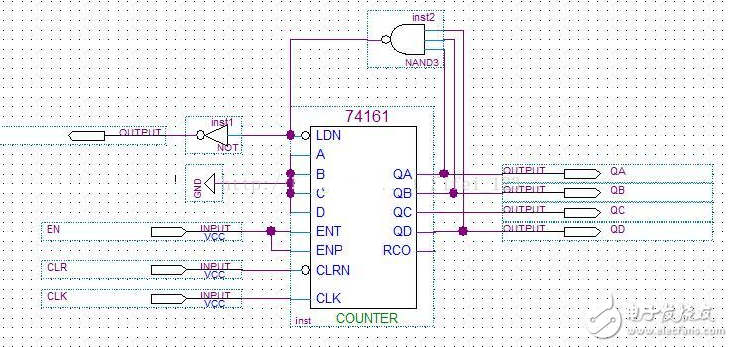

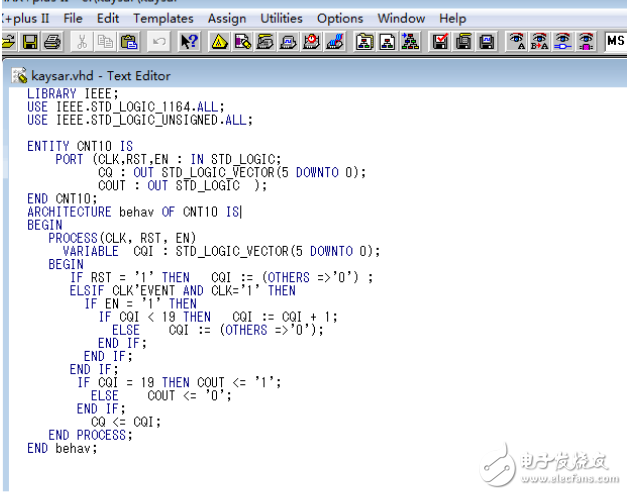

八進制計數器設計方案二:同步八進制加法計數器設計

時序電路的設計,就是根據給定的邏輯功能,設計其邏輯電路。設計步驟為:

a.擬定原始狀態表或狀態圖:把設計電路的一般文字描述變成電路輸入,輸出和狀態關系的說明,在此基礎上,擬定原始狀態表或狀態圖。

b.狀態簡化:原始狀態中可能有有多余的狀態,可用狀態簡化的方法將其消去,以得到最小狀態表。

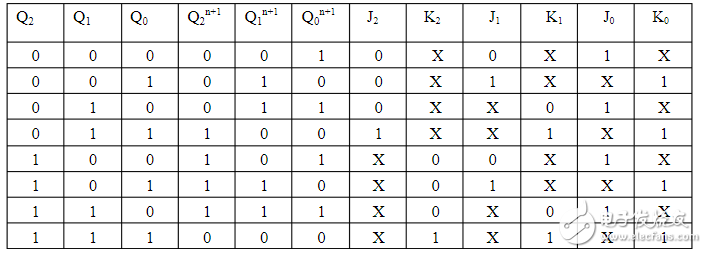

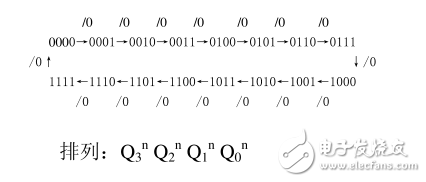

c.狀態分配:根據最小化狀態表的狀態數目,確定構成電路的觸發器數目。d.確定激勵函數和輸出函數:根據狀態表確定。擬定狀態表和激勵表(如下表)

同步八進制加法計數器狀態表

由上述表可求出方程:

J0=K0=1

J1=K1=Q0J2=K2=Q0Q1

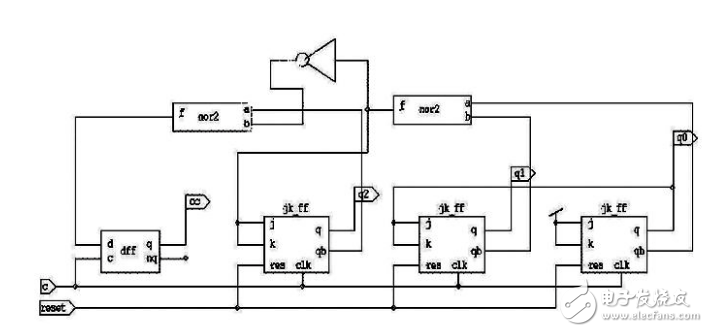

據方程得知我們所使用JK觸發器的連接方式,其中根據J2=K2=Q0Q1可知道本電路需要用到一個與門電路,但因為與門電路要使用6個二級管,而或非門只需4個二極管,為了使用版圖布線簡單,我們把與門替換成或非門,并把兩個輸入端改成0Q1Q。當計數到“111”的時候計數器進行進位,輸出C=1。而且此動作要與CP脈沖同步,此功能使用一個D觸發器來實現。

同步八進制加法計數器的邏輯圖

根據輸入輸出方程得出八進制加法計數器的邏輯圖如下圖:

同步八進制加法計數器邏輯圖

輸入時鐘信號:CLK輸出信號:Q0Q1Q2

輸出進位端:C

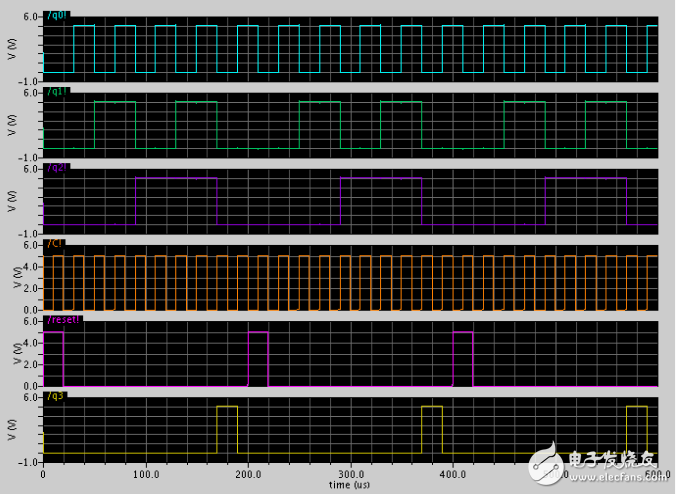

同步八進制加法計數器仿真波形

同步八進制加法計數器仿真波形圖

(1)輸出端用Q0Q1Q2表示,Q0為最高位,Q2為最低位,Q3是進位端,輸出端用Q2Q1Q0表示;

(2)設計算器的初始狀態為Q0Q1Q2=000,當第1個鐘脈沖CP上升沿到來時,若Reset為1,Q2由“0”變為“1”,計數器的輸出狀態Q0Q1Q2由000—001;第2個CP脈沖作用后,Q2由“1”變為“0”,由于下降沿的作用,Q1由“0”變為“1”,計數器的輸出狀態Q0Q1Q2由000—001;依次類推,逐個輸入CP脈沖時,計算器的輸出狀態按照Q0Q1Q2—000—001—010—011—100—101—110—111的規律變化。當輸入第8個CP脈沖時,Q2由“1”變為“0”,其下降沿使Q1由“1”變為“0”,Q1的下降沿使Q0由“1”變為“0”,計數狀態由111—000,完成一個計數周期。同時進位端Q3由“0”變為“1”。實現了同步八進制加法計數器的功能。

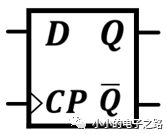

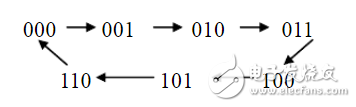

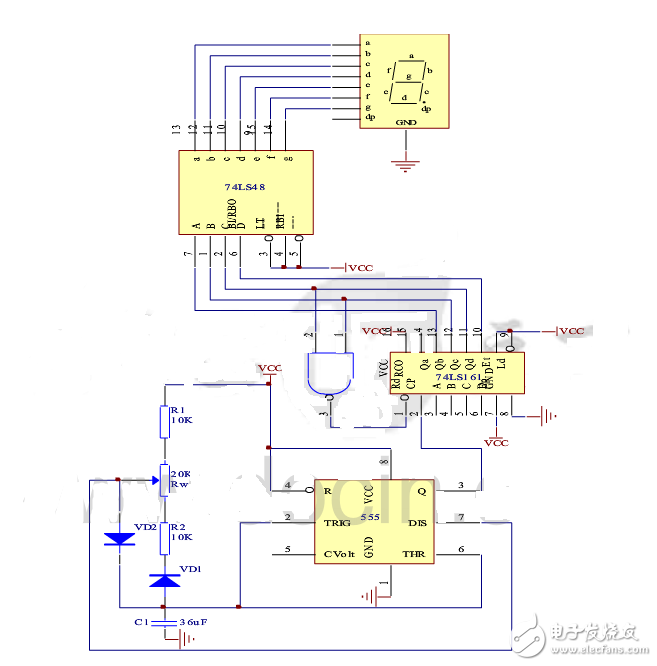

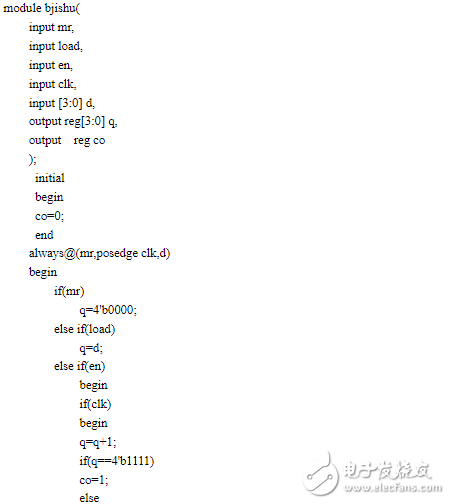

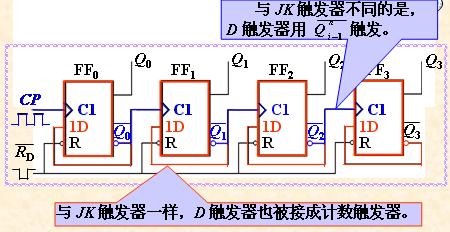

八進制計數器設計方案三:基于D觸發器的異步八進制計數器設計

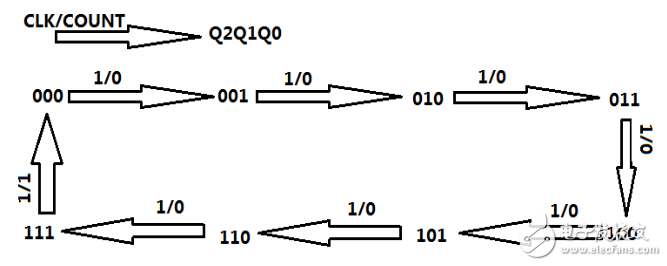

狀態圖以及激勵表

按照要求,計數器的狀態由時鐘上升沿控制,從000到111共八個狀態,其中從111狀態跳轉到000狀態時count輸出高電平。故可得出計數器的狀態圖如圖下圖所示。

八進制計數器狀態圖

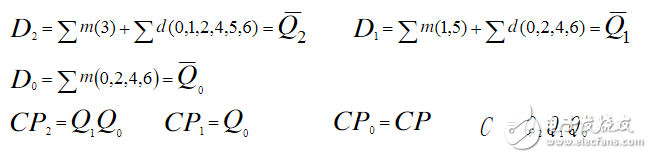

激勵表如下表所示(注:表中Qnm為觸發器輸出信號,Dn為觸發器輸入信號,CPn觸發器時鐘信號,C為進位信號)。

異步八進制計數器激勵表

根據上表可寫出激勵方程和時鐘方程

電子發燒友App

電子發燒友App

評論