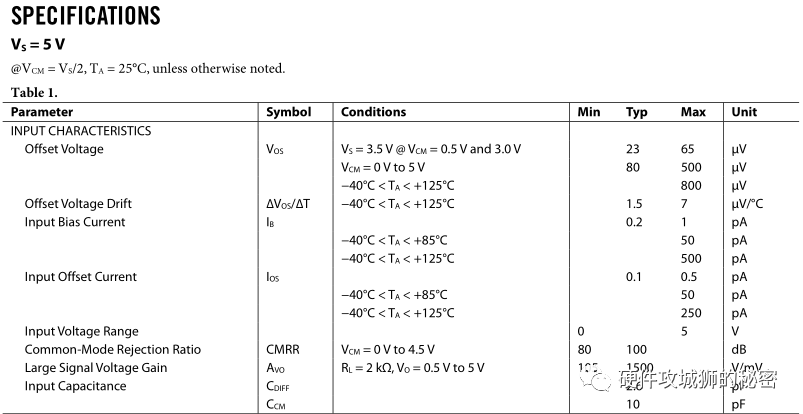

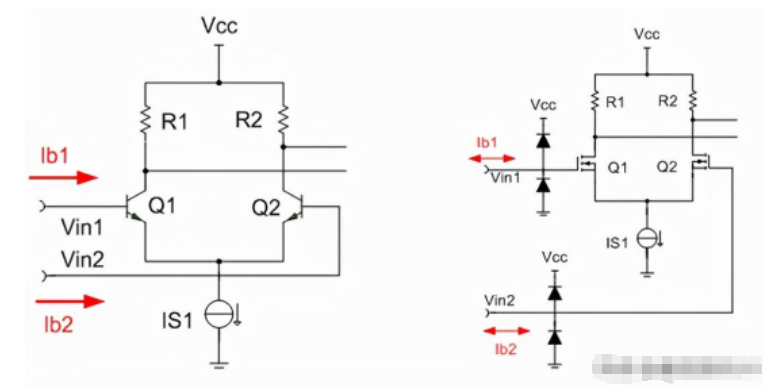

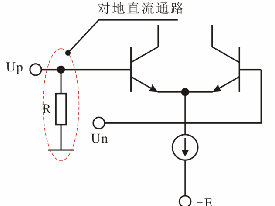

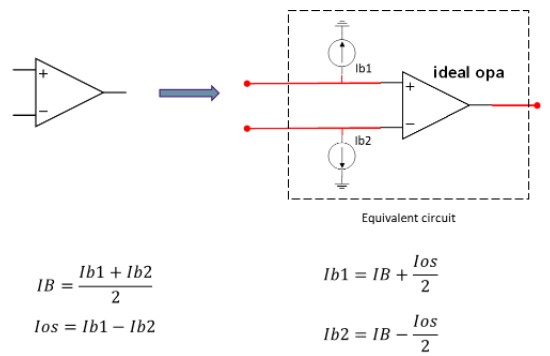

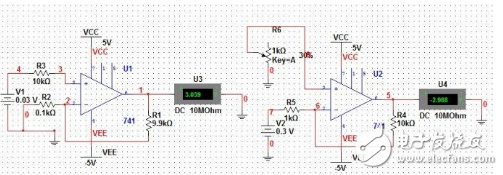

運放輸入失調(diào)電流為

Ios=(Ib+)-(Ib-)

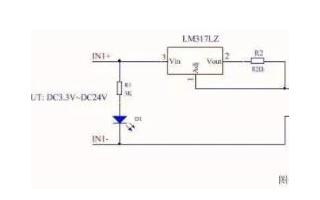

這種測試方法有幾個缺點,一個是使用了很大的電阻R1和R2,一般會是M歐級,這兩個電阻引入了很大的電壓噪聲。受到電阻R1和R2的阻值的限制,難以測得FET輸入運放的偏置電流。

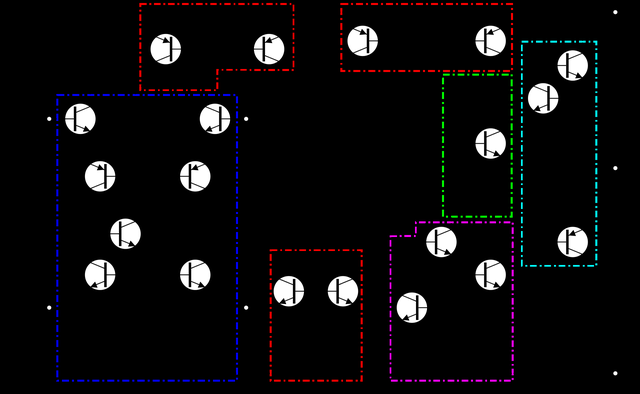

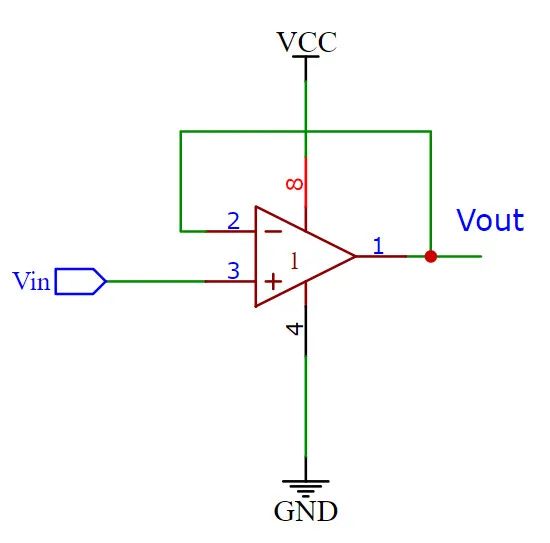

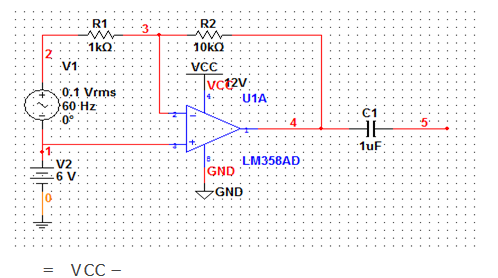

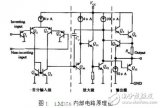

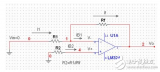

第二種方法測試方法,是讓運放的輸入偏置電流流入電容,具體測試如下圖。從圖中的公式很容易理解測試的原理,這個測試的關(guān)鍵,是選取漏電流極小的電容。

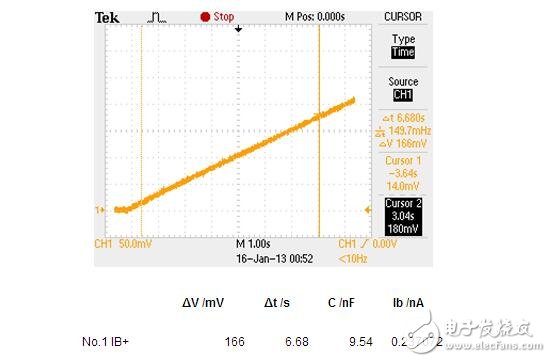

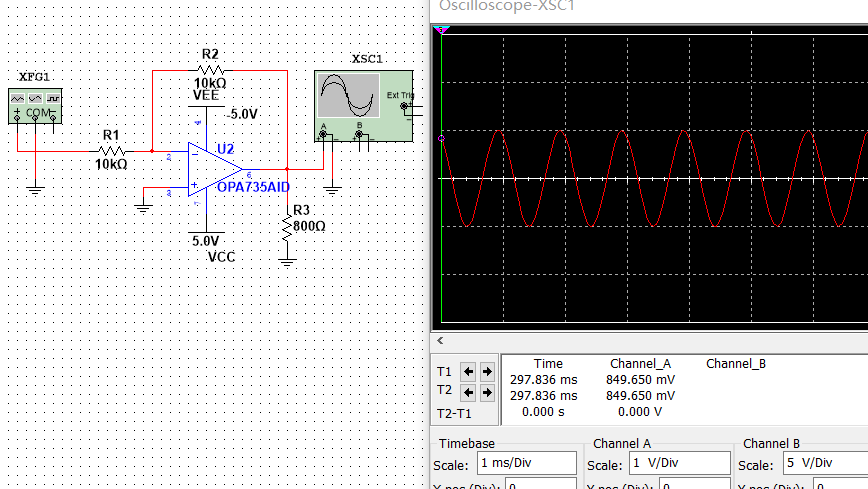

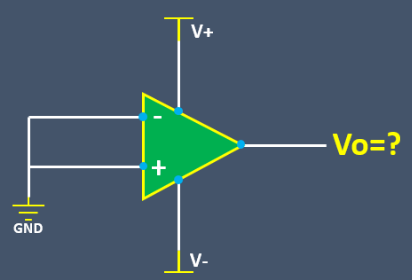

(1)打開S1,IB+流入電容C,用示波器觀察Vo的變化,結(jié)果如下圖,按上圖的方法就可以計算出IB+。

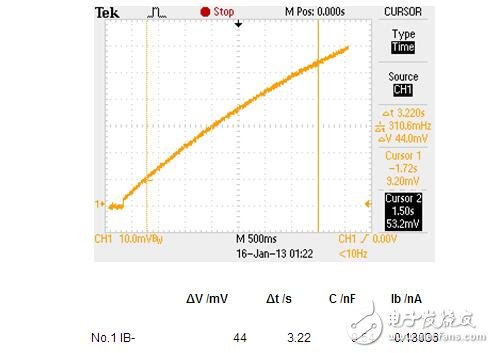

(2)關(guān)閉S1打開S2,IB-流入電容C,用示波器觀察Vo的變化,結(jié)果如下圖,可以計算出IB-。

(3)再根據(jù)定義就可以計算出運放的輸入偏置電流和失調(diào)電流。

這種測試方法可以測得fA級的失調(diào)電流。測試時需要選用低漏電流的電容,推薦使用極低漏電流的特氟龍電容,聚丙烯(PP)電容或聚苯乙烯電容。

再分享一個經(jīng)驗,就是貼片電容在焊接過程中,由于引腳可能殘留焊錫膏等雜質(zhì),會使FET運放的漏電流大大的增加。曾經(jīng)測試一個偏置電流為小于10pA級的運放,由于沒有對引腳 進行清洗,結(jié)果測得結(jié)果出現(xiàn)了很大的誤差,或者叫差錯,達了nA的水平了。

電子發(fā)燒友App

電子發(fā)燒友App

評論