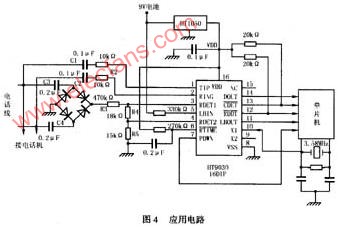

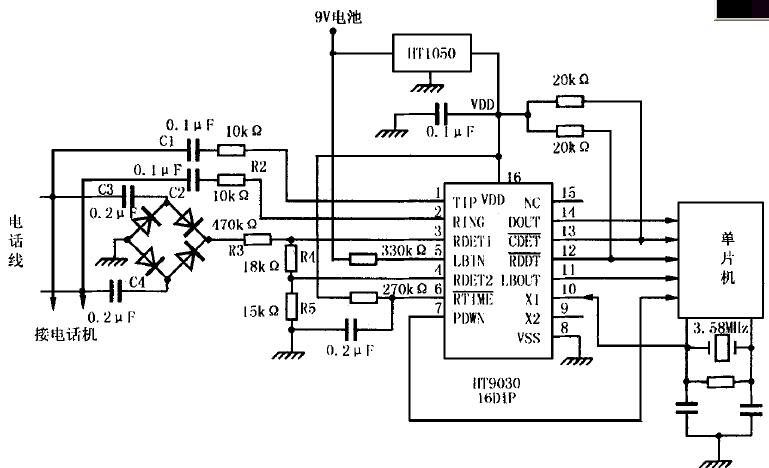

HT9030應(yīng)用電路

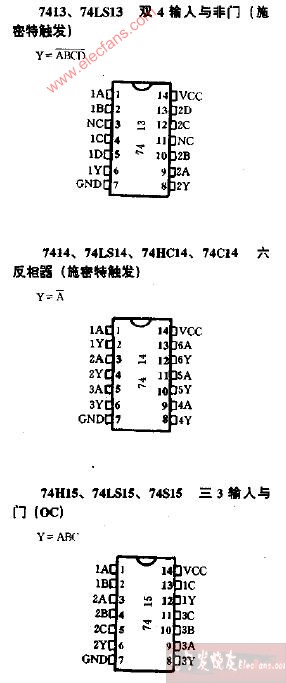

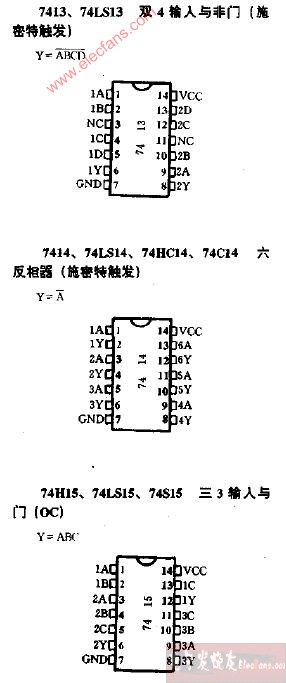

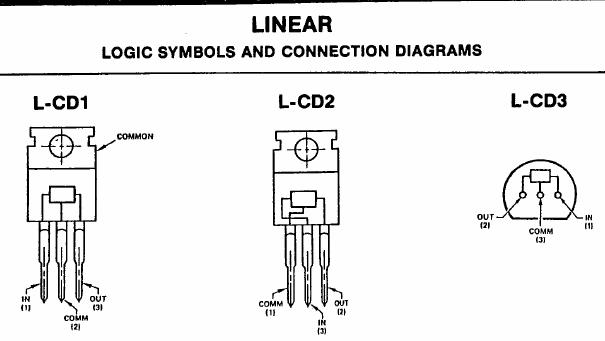

HT9030的引腳功能、管腳排列定義圖

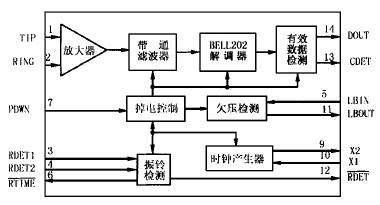

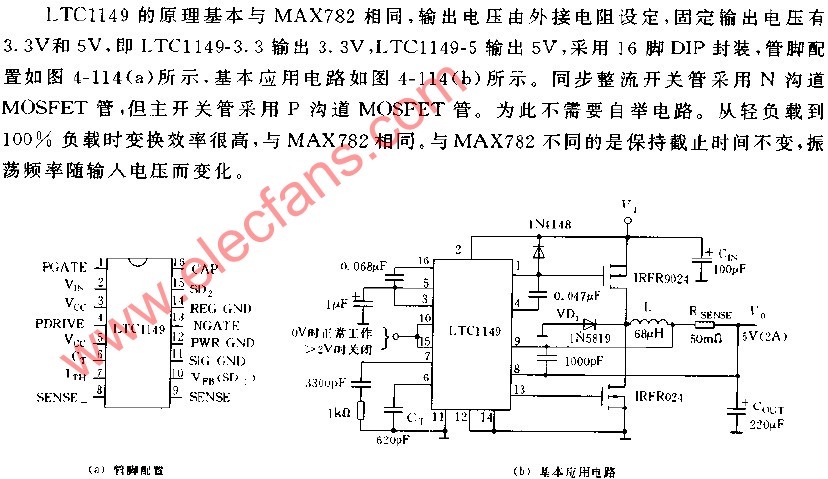

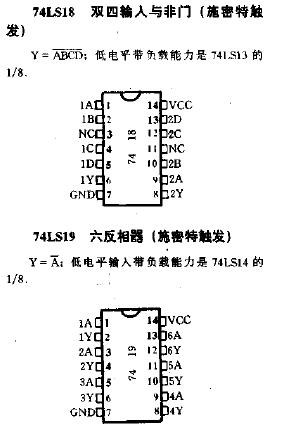

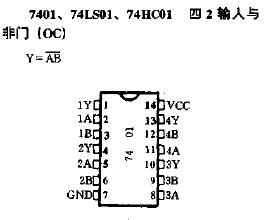

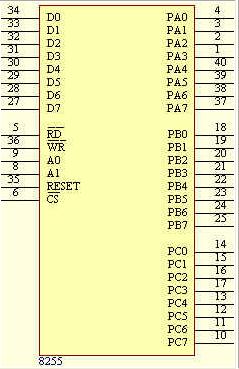

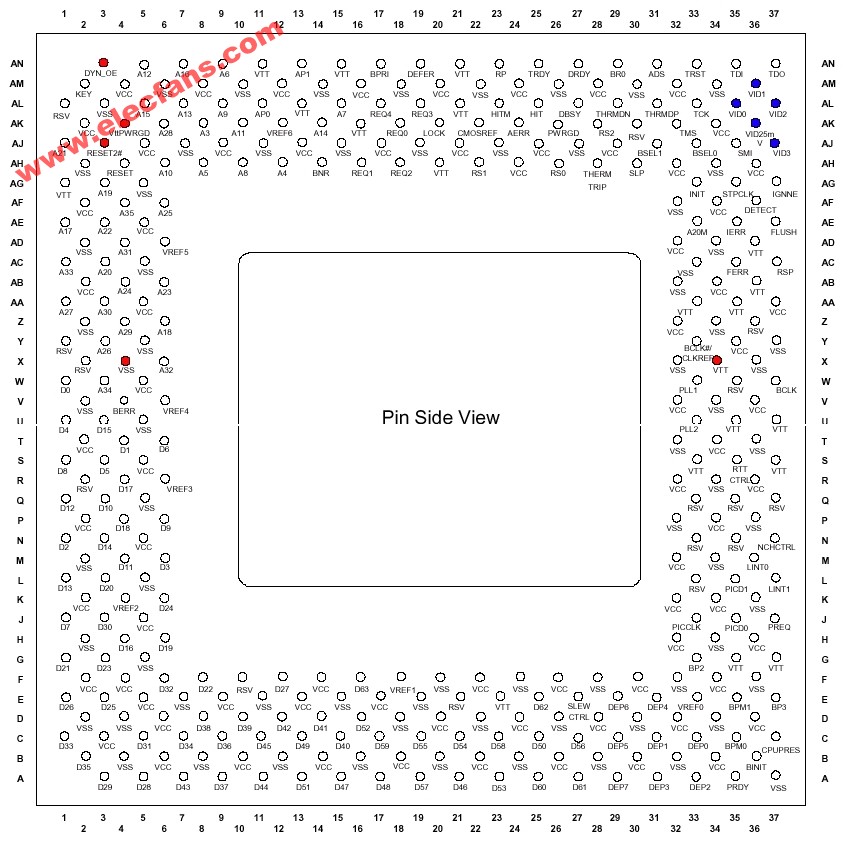

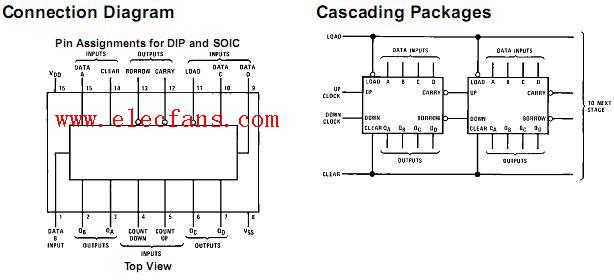

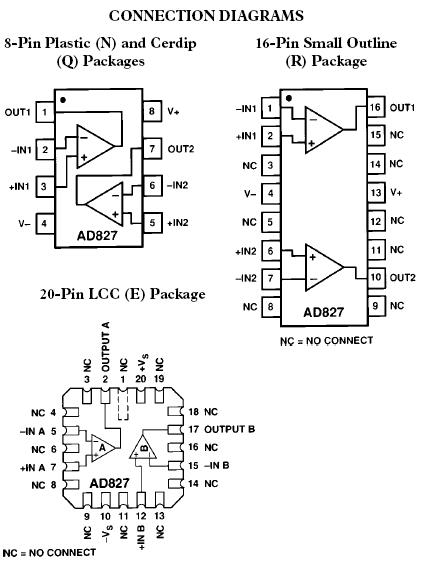

HT9030 采用雙列直插16 腳封裝,引腳排列及內(nèi)部結(jié)構(gòu)如圖3 所示。各引腳功能如下:

VDD 、VSS :分別是正電源和地;

TIP 、RIN G: 分別連接至電話線的兩端。工作時(shí), TIP 、RIN G 應(yīng)與電話線引出端分別串接一0. 1μF 的電容器,以實(shí)現(xiàn)電話線之間的直流隔離;

RDET1 : 通過(guò)衰減網(wǎng)絡(luò)檢測(cè)振鈴能量并啟動(dòng)振蕩器和鈴流檢測(cè)電路;

RDET2 : 通過(guò)衰減網(wǎng)絡(luò)將振鈴信號(hào)耦合至鈴流檢測(cè)電路;

LBIN :低電壓檢測(cè)輸入端;

RTIME :此端外接RC 網(wǎng)絡(luò),因此,此端在鈴流信號(hào)的峰值間的電壓低于2. 2 伏。它控制內(nèi)部上電并激活局部電路以判斷來(lái)電是否有效;

PDWN : 此端為高電平時(shí), 芯片處于掉電模式;為低電平時(shí),芯片被激活;

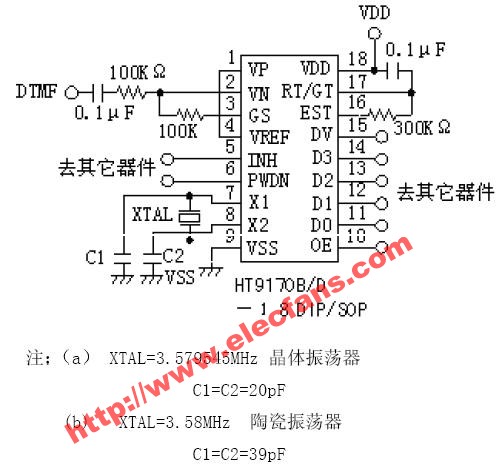

X1、X2 :外接3. 58MHz 晶振或陶瓷振蕩器;

LBPU T :當(dāng)LBIN 端的電壓低于內(nèi)部參考電壓時(shí),輸出高電平,否則輸出低電平;

RDET : 當(dāng)檢測(cè)到有效振鈴信號(hào)時(shí), 此端口變低。該腳與PDWN 腳相連時(shí)可自動(dòng)上電;

CDET : 當(dāng)檢測(cè)到電話線上的有效載頻時(shí),此端口變低。芯片內(nèi)置延時(shí)電路,允許載頻的瞬時(shí)偏移。此腳與PDWN 腳相連可用于自動(dòng)上電;

DOU T : 當(dāng)CDET 腳處于低電平時(shí), 此端輸出解調(diào)信號(hào), 數(shù)據(jù)流包括交替的1、0 和150ms 的標(biāo)記信號(hào),標(biāo)記信號(hào)位于數(shù)據(jù)的前端。其它時(shí)間,端口保持高阻態(tài)。芯片內(nèi)部由時(shí)鐘產(chǎn)生電路、振鈴檢測(cè)電路、掉電控制電路、欠壓檢測(cè)電路以及BELL 202 FSK 解調(diào)電路組成。振鈴檢測(cè)電路的作用是檢測(cè)電話線路上的振鈴信號(hào), 當(dāng)檢測(cè)到有效的鈴流信號(hào)時(shí), 芯片的12 腳輸出低電平, 同時(shí)觸發(fā)時(shí)鐘產(chǎn)生電路和掉電控制電路, 從而使整個(gè)芯片處于工作狀態(tài)。

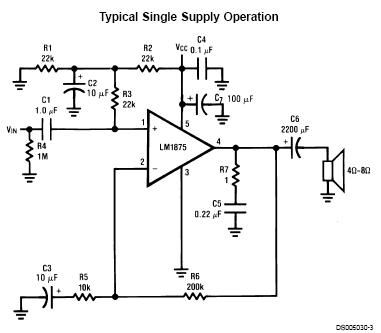

然后, 緊隨鈴流的BELL 202 FSK 信號(hào)從芯片的1、2 腳輸入, 經(jīng)放大器、帶通濾波器、解調(diào)器和有效數(shù)據(jù)檢測(cè)電路, 將主叫號(hào)碼信息從14 腳輸出。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論