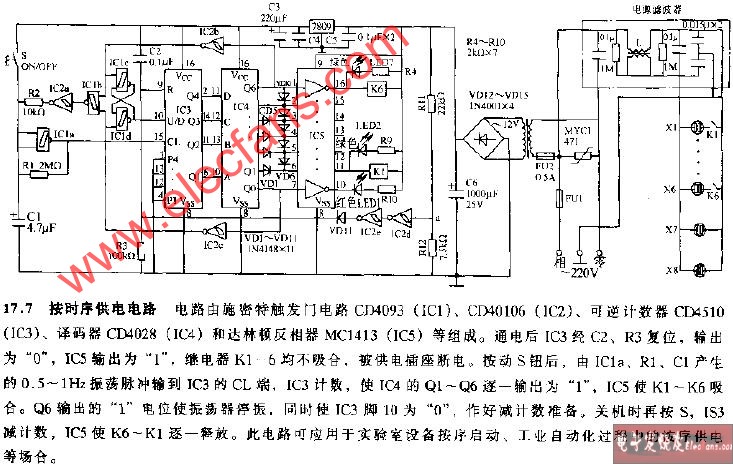

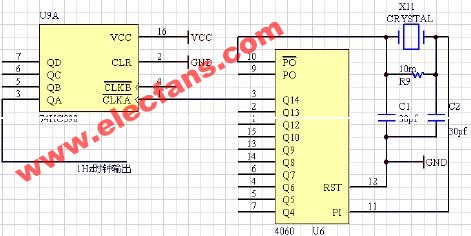

按時(shí)序供電電路

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術(shù)應(yīng)用>電路原理圖>電源>電源電路圖>按時(shí)序供電電路

相關(guān)推薦

836

836

422

422 211

211

375

375

266

266

830

830

680

680

886

886

10208

10208

424

424

2914

2914

546

546 6

6 5680

5680

3917

3917

989

989 15

15 1538

1538 2

2 9

9 4109

4109

2187

2187

3992

3992 3607

3607

1320

1320 5531

5531

13

13 19

19 7133

7133

48178

48178 29485

29485 9

9 3064

3064

868

868 41

41 24417

24417 170

170 5279

5279

104785

104785

51593

51593

61102

61102

120321

120321

89189

89189

12

12 12890

12890

25

25 82584

82584

20

20 91

91 17764

17764

3

3 63

63 67

67 67

67 23

23 51

51 14

14 80

80 6

6 4371

4371 9517

9517

59

59 71

71 37

37 7731

7731

71

71 47

47 5393

5393

30

30 3155

3155

1038

1038

評(píng)論